4月16日,三星官网发布新闻稿,宣布已经完成5纳米FinFET工艺技术开发,现已准备好向客户提供样品。

与7纳米工艺相比,三星的5纳米FinFET工艺技术提供了高达25%的逻辑面积效率提升。同时由于工艺改进,其功耗降低了20%、性能提高了10%,从而使芯片能够拥有更具创新性的标准单元架构。

跨越到5纳米工艺,除了在功率性能区域(PPA)的数据提高之外,客户还可以充分利用EUV(极紫外光刻)技术,推动产品接近性能极限。

除此之外,还可以将7纳米的相关知识产权重用到5纳米工艺上,使得客户从7纳米向5纳米过渡时可以大幅降低成本,缩短5纳米产品的开发周期。

三星表示,自2018年第四季度以来,三星5纳米产品就拥有了强大的设计基础设施,包括工艺设计工具、设计方法、电子设计自动化工具和IP。此外,三星晶圆厂已经开始向客户提供5纳米多项目晶圆服务。

2018年10月,三星宣布将首次生产7纳米制程芯片,这是三星首个采用EUV光刻技术的产品。目前,三星已于今年年初开始批量生产7纳米芯片。

除了7纳米与5纳米之外,三星还在与客户开发6纳米芯片,同样是一种基于EUV技术的芯片产品。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

三星电子

+关注

关注

34文章

15896浏览量

183211 -

FinFET

+关注

关注

12文章

262浏览量

92353 -

EUV

+关注

关注

8文章

615浏览量

88948

发布评论请先 登录

相关推荐

热点推荐

2nm“诸神之战”打响!性能飙升+功耗骤降,台积电携联发科领跑

(Tape out),预计2026年底进入量产。这意味着联发科成为首批采用台积电 2 纳米制程的公司之一。 此前,业内消息指出 三星电子 已完成其采用 2 纳米制程的Exynos

基于三星Exynos Modem的广和通5G模组Fx550正式全球量产

3月31日,广和通宣布:基于三星Exynos Modem平台开发的5G模组Fx550(包含LGA封装的FG550及M.2封装的FM550)已正式实现规模化量产。该产品的推出及量产不仅标

三星发布Exynos 2600,全球首款2nm SoC,NPU性能提升113%

电子发烧友网综合报道 近日,三星电子正式发布其手机芯片Exynos 2600。这款芯片意义非凡,它不仅是三星首款2nm芯片,更是全球首款采用2纳米(2nm)全环绕栅极(GAA)工艺制造

工程师选型指南:三星电机提供CLLC谐振专用1000V C0G MLCC及技术支持

贞光科技为三星电机授权代理商,贞光科技可提供同系列多档规格的选型支持与样品服务,协助客户加快项目导入。三星电机近日发布全新的1210(3.2×2.5mm)尺寸、C0G介质、1000V额定电压

三星公布首批2纳米芯片性能数据

三星公布了即将推出的首代2nm芯片性能数据;据悉,2nm工艺采用的是全栅极环绕(GAA)晶体管技术,相比第二代3nm工艺,性能提升5%,功耗

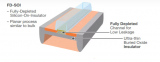

SOI工艺技术介绍

在半导体行业持续追求更高性能、更低功耗的今天,一种名为“SOI(Silicon-On-Insulator)”的工艺技术逐渐成为行业焦点。无论是智能手机、自动驾驶汽车,还是卫星通信系统,SOI技术都在幕后扮演着关键角色。

三星最新消息:三星将在美国工厂为苹果生产芯片 三星和海力士不会被征收100%关税

苹果称正与三星公司在奥斯汀的半导体工厂合作,开发一种创新的新芯片制造技术。 在新闻稿中苹果还宣布了将追加1000亿美元布局美国制造,这意味着苹果公司未来四年对美国的总投资承诺达到600

曝三星S26拿到全球2nm芯片首发权 三星获特斯拉千亿芯片代工大单

我们来看看三星的最新消息: 曝三星S26拿到全球2nm芯片首发权 数码博主“刹那数码”爆料称,三星Exynos 2600芯片已进入质量测试阶段,计划在今年10月完成基于HPB(High

新思科技与三星深化合作加速AI和Multi-Die设计

的经认证EDA流程优化功耗、性能和面积(PPA),并通过三星最新先进工艺技术支持的高质量IP产品组合可有效降低IP集成风险。

三星电子全力推进2纳米制程,力争在2025年内实现良率70%

根据韩国媒体ChosunBiz的报道,三星电子的晶圆代工事业部正在全力押注其2纳米制程技术,目标是在2025年内实现良率提升至70%。这一战略旨在吸引更多大客户订单,进一步巩固其在半导体市场中的竞争

看点:三星电子Q2利润预计重挫39% 星动纪元宣布完成近5亿元A轮融资

给大家带来一些业界资讯: 三星电子Q2利润预计重挫39% 由于三星向英伟达供应先进存储芯片延迟,三星预计将公布4-6月营业利润为6.3万亿韩元(约46.2亿美元;三星电子打算在周二公布

外媒称三星与英飞凌/恩智浦达成合作,共同研发下一代汽车芯片

据外媒 SAMMobile 报道,三星已与英飞凌(Infineon)和恩智浦(NXP)达成合作,共同研发下一代汽车芯片解决方案。 据悉, 此次合作将基于三星的 5 纳米

三星MLCC电容的微型化技术,如何推动电子产品轻薄化?

三星MLCC电容的微型化技术通过减小元件尺寸、提升单位体积容量、优化电路板空间利用率及支持高频高容量需求,直接推动了电子产品的轻薄化进程,具体如下: 1、先进的材料与工艺 :三星采用高

回收三星S21指纹排线 适用于三星系列指纹模组

深圳帝欧电子回收三星S21指纹排线,收购适用于三星S21指纹模组。回收三星指纹排线,收购三星指纹排线,全国高价回收三星指纹排线,专业求购指纹

发表于 05-19 10:05

三星宣布已完成5纳米FinFET工艺技术开发

三星宣布已完成5纳米FinFET工艺技术开发

评论