NVIDIA新一代显卡即将出炉,尽管对于个中细节并不了解细节,但业界普遍认为无论是NVIDIA还是AMD,新一代显卡搭载GDDR6显存可能性极高。什么?我的电脑才用上DDR4,怎么显卡就用GDDR6了?而且频率还跑得那么高?是不是理不清它们之间的关系?下面就让我们重新回顾一下显存的发展历史,展望下一代GDDR6显存的一些新特性。

其实DDR内存和GDDR显存本来就是同宗同源,初期时DDR/GDDR、DDR2/GDDR2其实规范差异很小,频率等参数基本上都是一致,两者不分家,因此当时显卡即可以用DDR2颗粒,也可以用GDDR2显存颗粒。

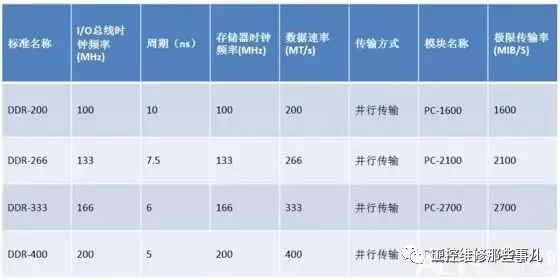

这个图是不是很熟悉

Q:

DDR的种类:

A:

1、DDR SDRAM:Double Data Rate Synchronous Dynamic Random Access Memory,双倍数据率同步动态随机存取存储器;

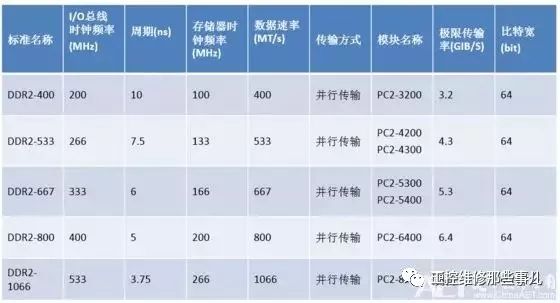

2、DDR2 SDRAM:Double-Data-Rate Two Synchronous Dynamic Random Access Memory,第二代双倍数据率同步动态随机存取存储器;

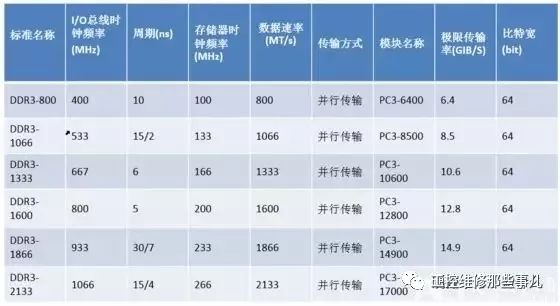

3、DDR3 SDRAM:Double-Data-Rate Three Synchronous Dynamic Random Access Memory,第三代双倍数据率同步动态随机存取存储器;

4、DDR4 SDRAM:Double-Data-Rate Fourth Synchronous Dynamic Random Access Memory,第四代双倍数据率同步动态随机存取存储器。

DDR的发展:

SDRAM

DDR

DDR2

DDR3

DDR4

可以很清楚地发现,DDR、DDR2、DDR3和DDR4之间的接口并不兼容,当然,其工作电压也是不一样的。(除了DDR4是台式机的接口,前三个为笔记本上的接口)

DDR SDRAM可在一个时钟周期内传送两次数据

DDR数据传输速度为系统钟频率的两倍,能在选通脉冲的上升沿和下降沿传输数据

DDR2的数据传输速度为系统时钟频率的四倍

DDR3的数据传输速度为系统时钟频率的8倍

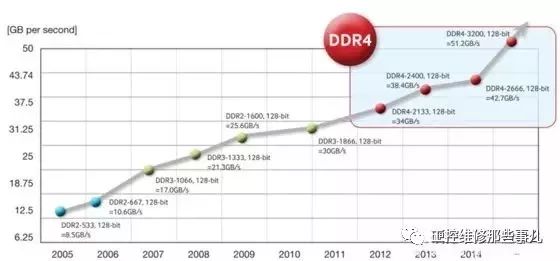

DDR的发展图

Samsung-DDR的带宽与数据传输率上升轨迹

Q:

QDR是什么?

A:

SDR(Single Data Rate):单倍数据倍率,只利用时钟信号的上沿传输数据,例如SDRAM等。

DDR(Double Data Rate):双倍数据倍率,利用时钟信号的上沿&下沿传输数据,例如DDR-SDRAM等。

QDR(Quad Data Rate):四倍数据倍率,在DDR的基础上,拥有独立的写接口和读接口,以此达到4倍速率,例如QDR-SRAM等 。DDR2-SDRAM,DDR3-SDRAM基本原理和DDR-SDRAM是一样的,通过提高时钟频率来提升性能,因为时钟频率提高了,必须做相应的预处理(DDR支持2、4、8busrt, DDR2支持4和8,而DDR3只支持8)。

QDR是Quad Data RateStatic Random Access Memory(QDR SRAM)的缩写,也就是四倍数据速率静态随机存取存储器的意思。QDR的四倍数据速率是相对普通SRAM而言的。

普通SRAM使用半双工总线,即在同一时刻只能进行读或者写操作(读/写共用一条数据通道),所以普通SRAM又称作SDR(Single Data Rate)SRAM,即“单倍数据速率静态随机存取存储器”。

DDR(Double Data Rate) SRAM在SDR SRAM的基础上做了改进,与SDR SRAM只在参考时钟的上升沿采样数据不同,DDR SRAM在参考时钟的上升沿和下降沿都采样数据,这样,DDR SRAM在一个时钟周期内可以传输双倍数据,DDR SRAM(双倍数据速率SRAM)也是由此得名的。

QDR在保留DDR特征的基础上,对其数据总线进行了升级,DDR只有一条数据通道,数据读/写操作共用,属于半双工工作方式,而QDR拥有两独立条数据通道,数据读/写操作可以同时进行,属于全双工工作方式,因此,QDR的数据存取速率又是DDR的两倍。

这样计算下来,QDR的数据存取速率是SDR的四倍,四倍数据速率的雅称也因此而来。QDR1/2/3的最高工作频率分别为200/333/500MHz。在高速通信系统中(40G/100G)基本上都使用QDR。

QDR器件规范是由Cypress、IDT、NEC、Samsung和Renesas等公司组成的QDR联盟共同定义和开发的。QDR联盟的官方网站是:http://www.qdrsram.com。

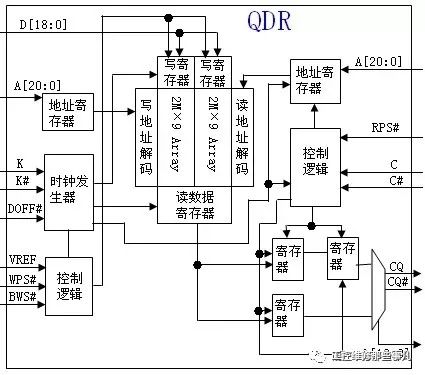

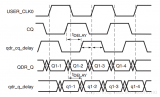

同DDR一样,QDR也分为QDR1、QDR2和QDR3。与QDR1相比,QDR2增加了一对源同步时钟,可以帮组SRAM控制器捕获数据,此时钟被称为反馈时钟(CQ和CQ#),这个反馈时钟与QDR2的输入参考时钟保持同步,同时又与QDR2输出路径的数据总线保持沿对齐。这样,QDR2产生的整体数据有效视窗便会比同频率的QDR1增大约35%,而延迟却比QDR1少了二分之一个周期,这额外的半周期可容许在最低的延迟下进行更高频率和更大带宽操作。QDR3目前还处在概念中,QDR联盟于2004年5月制定的QDR3规范中,器件的最高时钟频率可达500MHz。QDR器件结构示意图如下所示:

1).K/K#:QDR系统时钟信号;

3).CQ/CQ#:输出环回时钟;

这里说明下,K/K#、C/C#和CQ/CQ#不是真正的差分信号,而是相位相差180度的伪差分时钟,在测试时不能使用差分探头,一般使用两个单端探头。

4).A[20:0]:地址输入信号,读写通道复用,分别在时钟K/K#的上升沿采样;

5).WPS#:写端口选择输入信号,在时钟信号K的上升沿有效,当WPS#无效时,写端口信号被忽略;

6).BWS[3:0]#:比特写入选择信号,用于选择将拿个Byte写入到QDR钟,对于9位数据位宽的QDR,用BWS0#控制,对于18位数据位宽的QDR,由BWS0#控制低9位,BWS1#控制高9位,其他以此类推;

7).NWS[0:1]#:4字节写入选择信号(此管脚只在8位QDR器件上才有),用来控制当前写端口的哪4位字节被写入,NWS0#控制D[3:0],NWS1#控制D[7:4]。

8).RPS#:写端口地址选择输入信号,时钟K上升沿有效,当RPS#信号无效时,读端口信号被忽略;

9).D[18:0]:写操作数据输入通道,在时钟K和K#的上升沿有效;

10).Q[18:0]:读操作数据输出通道,单时钟模式下,在在时钟K和K#的上升沿有效,多时钟模式下,在时钟C和C#的上升沿有效;

11).ZQ:输出阻抗控制信号。用于控制QDR的输出端口的CQ/CQ#以及Q[18:0]等信号的输出阻抗。当ZQ和GND间的电阻为RQ时,则CQ/CQ#和Q[18:0]的输出阻抗被设置为0.2RQ。当ZQ直接连接到VDD时,输出信号有最小的输出阻抗,ZQ不能悬空或直接接地;

12).DOFF#:DLL使能输入信号,当该管脚接地时,将会关掉QDR内置的DLL;

13).144M/288M:144M/288M地址扩展引脚,在72M器件上,这些管脚必须拉低。

QDR SRAM的I/O端口采用的是HSTL电平。HSTL即High SpeedTransceiver Logic,是一种基于EIA/JESD8-6标准的数字接口电路逻辑,其输出为一差分放大器(如果只使用一端的话,另一端需要与内部参考电压相连),QDR具有单独的输出端口电源Vddq,QDR1为2.5V、QDR2为1.8V、QDR3为1.2V。

QDR有三对参考时钟,其中,只有K/K#时钟是必须的,它是写数据和地址信号的采样时钟。C/C#和CQ/CQ#这两对时钟可选,QDR有四种时钟设计方案,分别如下:

1).仅使用K/K#时钟。K/K#既是写参考时钟,也是读参考时钟;

2).用K/K#时钟和C/C#时钟,不使用CQ/CQ#时钟;

3).用K/K#时钟和C/C#时钟的换回环,不用CQ/CQ#时钟;

4).用K/K#时钟和CQ/CQ#时钟。

由于K/K#时钟和CQ/CQ#时钟分别是由QDR控制器和QDR本身提供的,这样,在读写时都有源同步时钟做参考,所以,在高速设计中,基本上都是使用第四种时钟方案。

使用单时钟模式时,C/C#时钟必须从外部上拉到高电平(CQ/CQ#是输出时钟,无需处理),在使用第二种时钟模式时,C/C#的时钟的PCB走线必需要比K/K#时钟长,QDR2 SRAM有一个参数tKHCH(即K/K#时钟和C/C#时钟的skew),规范中要求此参数必须大于0,因为QDR的同时读写特点,假设在同一时钟周期内,要对同一个地址的数据进行读操作和写操作,规范要求是,要先进行写操作,后进行读操作,也就是写参考时钟K/K#需要比读参考时钟C/C#先到达。但是,规范中同时规定,C/C#时钟与K/K#时钟之间的skew必须小于三分之一时钟周期。

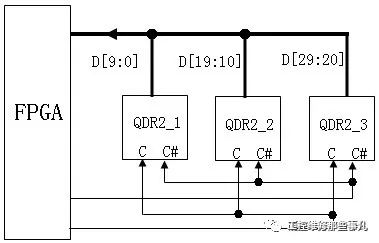

如果将多片QDR2 SRAM器件并联使用的话,需要注意C/C#时钟的PCB走线方式,即C/C#时钟须先到达最远端的QDR器件(即第三种时钟方案),最后到达最近处的QDR器件,这样,参考时钟信号的延迟正好可以抵消数据信号的延迟,确保几个器件上的数据保持同步,如下图所示。

使用QDR器件时,须注意一下几点:

1).QDR2有最低频率要求,最低工作频率不能低于120MHz;

2).QDR上电期间,要保证DOFF#管脚一直处于低电平,因为DOFF#的作用是使能器件内部的DLL,在刚上电的这段时间,时钟信号本身是不稳定的,为了让内部DLL正确的锁住时钟,需要停止时钟信号至少30ns来复位内部DLL,然后等外部时钟稳定后在使能DLL去锁定稳定的时钟;

3).VDD要先于VDDQ上电,VDDQ要先于VREF或与之同时上电。

Q:

GDDR是什么

A:

GDDR是Graphics Double Data Rate的缩写,为显存的一种,GDDR是为了设计高端显卡而特别设计的高性能DDR存储器规格,其有专属的工作频率、时钟频率、电压,因此与市面上标准的DDR存储器有所差异,与普通DDR内存不同且不能共用。一般它比主内存中使用的普通DDR存储器时钟频率更高,发热量更小,所以更适合搭配高端显示芯片。

当应用程序越来越多要进行3D显示及演算时,频繁地读取在显卡中的SDRAM或SGRAM保存的连续画面图像数据的速度开始不能满足需求,人们研发了GDDR,它是为了代替旧式显存的不足而出现。开始时第一代GDDR只是普通DDR的稍微改进版,但也比旧式显存要快的多。

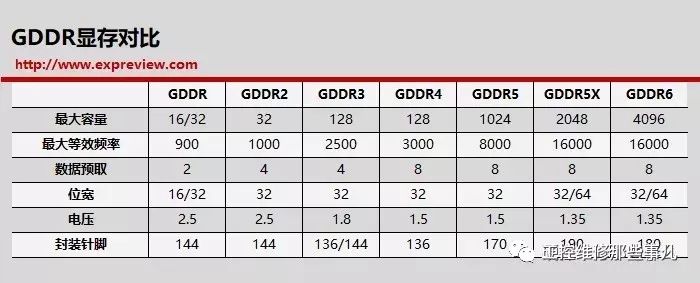

进入GDDR时代的显存家族一共有五兄弟,分别是GDDR、GDDR2、GDDR3、GDDR4和GDDR5。GDDR显存已在市场被淘汰,目前市场上常见的显存主要有GDDR2、GDDR3、GDDR4、GDDR5几种类型的产品。

GDDR2显存,目前多被低端显卡产品采用,采用BGA(Ball Grid ArrayPackage)封装,显存的速度从3.7ns到2ns不等,最高默认频率从500MHz~1000MHz,但明显不如GDDR3显存。其单颗颗粒位宽为16bit,组成128bit的规格需要8颗。

GDDR3显存是专门为图形处理开发的一种新型内存,同样采用BGA封装技术,其单颗颗粒位宽为32bit,8颗颗粒即可组成256bit/512MB的显存位宽及容量。显存速度在2.5ns(800MHz)~0.8ns(2500MHz)间。相比GDDR2,GDDR3具备低功耗、高频率和单颗容量大三大优点,使得GDDR3目前为主流显卡产品广泛采用。

GDDR4和GDDR3基本技术一样,GDDR4单颗显存颗粒可实现64bit位宽64MB容量,也就是说只需4颗显存芯片就能够实现256bit位宽和256MB容量,8颗更可轻松实现512bit位宽512MB容量。目前GDDR4显存颗粒的速度集中在0.7ns~0.9ns之间,但GDDR4显存时序过长,同频率的GDDR3显存在性能上要领先于采用GDDR4显存的产品,并且GDDR4显存并没有因为电压更低而解决高功耗、高发热的问题,这导致GDDR4对GDDR3缺乏竞争力,逐渐被淘汰了。

相对于GDDR3、GDDR4而言,GDDR5显存拥有诸多技术优势,还具备更高的带宽、更低的功耗、更高的性能。如果搭配同数量、同显存位宽的显存颗粒,GDDR5显存颗粒提供的总带宽是GDDR3的3倍以上。由于GDDR5显存可实现比目前主流的128bit或256bit显存更高的位宽,也就意味着采用GDDR5显存的显卡会有更大的灵活性,性能亦会有较大幅度的提升。所以目前主流的高端显卡都无一例外地采用了GDDR5显存。

DDR的带宽发展远远跟不上GDDR

因此显存与内存分道扬镳是基于技术需求上的考虑,毕竟术业有专攻,GDDR显存的推出就是更好地满足GPU胃口,达到更好的性能。

但是后期由于超大规模集成电路技术飞速进步,加上人们对于显卡性能日益增长的需求,普通的GDDR/GDDR2显存已经不能满足显卡GPU高速交互数据需求,毕竟GPU没有像CPU那样设计有大容量L1、L2、L3缓存,而且GPU与显存之间的数据交换非常频繁,还是那种大容量的纹理贴图数据,需要更高的显存带宽;其二是显存可以直接集成于显卡PCB上,不必像内存那样做成独立部件,又要考虑走线、信号传输延迟,可以专门做定向优化,同时提高显存位宽有利于减少显存颗粒,在显卡上实现更高容量的显存集成。

GDDR(Graphics Double Date Rate SDRAM,双倍速率同步动态随机存储器)

和DDR一样都是采用2bit预取,同时可以在一个时钟周期的上升沿和下降沿分别传输一次数据,这样就实现单时间周期两倍的传输速率。但此时GDDR频率并不比DDR要高出多少,但是GDDR为了追求更高的频率,在延迟要求上有所放宽。

GDDR颗粒为了追求大位宽,因此容量会特别小,那时候都是8×16Bit的规格,也就是一颗GDDR显存才16MB大小,而同期的DDR内存颗粒可以做到32甚至64MB大小。

如果你浸淫在PC DIY界多年,你可能会记得以前DDR、GDDR显存颗粒都是这种多脚的TSOP封装,而且GDDR显存颗粒体积也很大。

▲DDR内存

后期由于光刻工艺升级以及追求更加的封装面积,存储厂商在GDDR上实现了BGA封装技术,也就是针脚不外露,全部藏在底部。同时实现了32bit的显存位宽,并且一直延续至今。

GDDR2

技术细节同样来自于DDR2,和DDR2一样GDDR 2bit的预取升级到4bit,相比DDR1代可以将频率翻倍。不过由于GDDR2跑得比DDR2还快,诞生时间早,工艺上可能稍微欠缺了一点,工作电压高达2.5V,尽管等效工作频率高达1GHz,但巨大的发热量甚至媲美GPU核心,需要专门的散热片辅助散热。

▲DDR2内存

因此采用GDDR2显存的显卡都是昙花一现,只有NVIDIA的FX5800 /5600 Ultra、ATI9800Pro用过,很快就消息了,可以说GDDR2是个失败的产品。

▲ATI9800Pro

GDDR3

被GDDR2坑过后,大家都认为存储标准制定方JEDEC跑得实在是太慢了,GDDR、GDDR2标准严重不符合显卡GPU发展需求,NVIDIA、AMD开始联手对GDDR3标准实施深入的指导,因此GDDR3可以说真正地与DDR3分道扬镳,技术标准得到大幅度提升。

▲DDR3内存

深刻地认识到GDDR、DDR应用场景完全不同,因此设计之初就应该考虑到这个问题,考虑到高速读写需求,GDDR3设计有两条独立的数据选择脉冲DQS,一条用于读取,另一条用于写入,这样互不干扰,因此GDDR3读写数据速度要比GDDR2快多了,毕竟GPU存取数据频繁程度高,GDDR3的新设计可以让显存效率大幅度提升。

尽管GDDR3保留GDDR2的4bit预取,但对GDDR3也修改I/O控制电路,新的电路设计可以最大程度降低电流,工作电压也随之下降到1.8V,间接地控制住功耗和发热量,一举解决GDDR2存在的弊端。

都说工艺是提升性能、频率的良方,GDDR3凭借制程工艺红利,从1GHz不断攀升,一直走到了2.5GHz,因此其生命线长达五年才落幕。

▲奇梦达的GDDR3

▲三星的GDDR3

GDDR4

可能是GDDR3跑得太快,标准对于往后几代GPU来说还算是够用,加上NVIDIA与ATI之间竞争日益剧烈,就GDDR4标准制定分歧严重,最后NVIDIA明确表示不支持GDDR4,显卡产品也并没有采用,最终标准GDDR4由ATI一手操办,但缺乏NVIDIA的支持,存储厂商只有小规模试产,AMD也只有三款非主流产品采用了GDDR4显存,因此GDDR4起不了什么浪花。

▲DDR4内存,已经和GDDR4显存没有瓜葛了

事实上,GDDR4技术是有巨大进步,使用DDR3的8bit预取技术,这个也是NVIDA与ATI矛盾发展的开端。然后采用了Data Bus Inversion技术,提高数据精度、降低工作电压至1.5V,继续降低功耗。

而GDDR4频率起步就是2GHz水平,其后虽然有更高频率颗粒出现,但是由于NVIDIA的不支持,市场太小导致生产成本高涨,加上AMD显卡性能不如同期N卡,GDDR4很快就被历史所遗忘。

▲AMD Radeon HD2600XT用的就是GDDR4

GDDR5

GDDR显存的命运总是那么跌宕起伏,奇数代的显存总是存活得更久,2012年GDDR5显存终于登上舞台,在继承GDDR4的8bit预取,加上QDR双数据总线、4路bank设计让GDDR5显存频率突飞猛进,一路高歌,一并冲上8Gbps。

尽管GDDR5只有32bit的颗粒,但是它拥有两条并行的数据总线,那么他的工作模式就相当灵活,可以自由在32bit、16bit一下工作,同时一个32bit显存控制器也能控制两个GDDR5显存,实现了显存容量翻倍。

根据当时NVIDIA 200系列显卡上市情况来看,即便是采用相同GPU核心,使用GDDR5显存会比GDDR3显存,综合性能提升20%以上,这个提升幅度相当惊人。也因此GDDR5能够经久不衰,一直到1000系列还在用,而且频率不断在进步,达到8Gbps的巅峰。

▲三星GDDR5

GDDR5X

嗯?怎么突然冒出个GDDR5X,GDDR6哪里去了?这可不得怪JEDEC标准定制得太慢,NVIDIA已经忍不住了,联合美光推出了这样一个半代产品GDDR5X,还是高端NVIDIA显卡独占。

GDDR5X可以视为GDDR6的先行版,它继续将预取从8bit提升至16bit,使用了改进版的QDR 4倍数据倍率技术,也就是说每个时钟可以传输4bit数据!GDDR5X的电压下降到1.35V。最终我们见到首批使用GDDR5X显存频率可以高达10Gbps,据说后续还会有14Gbps的版本面世。

▲美光GDDR5X

GDDR6

GDDR6标准终于姗姗来迟,即将到来的NVIDIA 11系列显卡肯定是要用上它的。和GDDR5X一样采用了16bit预取,这已经是被证实提高数据传输速度最为有效的方法。其次就是GDDR6终于一改以往GDDR1/2/3/4/5/5X只有一个读写通道问题,使用双通道,虽然位宽变小了,但是实际上效率更高以后,会带来明显的性能提升。

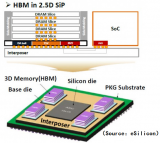

其次就是显存容量的进步,原本GDDR5最常见的都是8Gb单颗粒,而GDDR6标准下最高可以达到32Gb,换算过来单颗粒就是4GB,好处显而易见,那就是低端显卡单颗粒就搞定了,还要什么HBM2?高端3颗也就满足12GB,推算顶级显卡384bit显存位宽计算,搭载12颗就能达到48GB,难怪NVIDIA丝毫没有在消费级游戏卡上用HBM2显存的意思。

▲GDDR6带宽可以达到896GB/s,这是美光提供的数据

此外GDDR6修改了封装方式,减少了底部接口数目,从190 ball减少至180ball,尺寸更小,这样应用场景更为宽阔。

▲GDDR6优势——针脚少、尺寸更小、效能更高

目前全球三大存储芯片厂商三星、海力士和美光都推出了自己的GDDR6计划,不过由于技术实力差异和产品研发路线不同等因素,这三家的产品还存在一定的区别。

三星

期初三星在GDDR6上也是雷声大雨点小,推出GDDR6的时机也要晚于其余两家,但三星厚积薄发,一推出的GDDR6显存规格就是最高的,1Y nm工艺(10-16nm),单颗粒2GB,速度最高可达18Gbps,超过了JEDEC规范。

海力士

首批采用21nm工艺,单颗粒1GB容量,速度有10/12/14Gbps,也超过GDDR5X现时的极限,比较有趣的是,GDDR6电压应该是1.35V,海力士研发出1.25V低电压版的GDDR6显存,估计是为笔记本设备研发的。

美光

美光是最早、也是最积极推进GDDR6显存的存储厂商,将会采用16nm工艺制造,也是单颗粒8Gb,速度10-14Gbps不等,而且也有对应多款1.25V低电压版GDDR6显存。

如今GDDR6显存依靠高频率、高容量和低功耗特性,将会在未来新一代游戏显卡上大方异彩,为新架构显卡带来更强大的综合性能,而且对比成本居高不下、封装难度高的HBM 2显存来讲,GDDR6显然更加实惠,更易于往中低端显卡推广。

-

DDR

+关注

关注

11文章

761浏览量

69564 -

QDR

+关注

关注

0文章

14浏览量

12290 -

GDDR

+关注

关注

0文章

28浏览量

5044

原文标题:DDR、GDDR、QDR的区别

文章出处:【微信号:pcb_repaired,微信公众号:工控维修那些事儿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

DDR3不是GDDR3 细说GDDR3显存认识误区

FPGA控制8GDDR2

用于DDR、QDR和QDR-IV SRAM的完整高性能稳压器解决方案

用于DDR、QDR和QDR-IV SRAM的超薄型三路输出µmodule稳压器

三种主流内存技术(DDR、GDDR、LPDDR)的速度对比与应用和DDR5芯片的设计

QDR SRAM接口FPGA详细Verilog代码分享

简谈SDR、DDR、QDR存储器的比较

如何使用 QDR(TM) II SRAM 和 DDR II SRAM 用户手册

GDDR和DDR代表什么?GDDR和DDR内存有什么区别?

一文分析DDR、GDDR、QDR的区别

一文分析DDR、GDDR、QDR的区别

评论