声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1655文章

22287浏览量

630327 -

收发器

+关注

关注

10文章

3795浏览量

110587 -

赛灵思

+关注

关注

33文章

1797浏览量

133151

发布评论请先 登录

相关推荐

热点推荐

现已上市:AMD Spartan UltraScale+ FPGA SCU35 评估套件——面向所有开发人员的经济实惠平台

AMD Spartan UltraScale+ FPGA SCU35 评估套件现已开放订购。 该平台由 AMD 构建,为客户提供了一条利用 Spartan UltraScale+ FPGA

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

本篇将详细介绍如何利用Verilog HDL在FPGA上实现SRAM的读写测试。SRAM是一种非易失性存储器,具有高速读取和写入的特点。在FPGA中

NucleiStudio下载程序到FPGA中的E203上

使用NucleiStudio开发应用程序,并将应用程序的代码下载到FPGA上。这里,以helloworld为例,介绍该过程遇到的问题以及解决方法。

1、新建Nuclei RISC-V C/C++项目,使用ILM的下载

发表于 10-20 09:24

AMD Spartan UltraScale+ FPGA的优势和亮点

AMD Spartan UltraScale+ FPGA 集小型封装、先进的 I/O 功能与低功耗等优势于一体。该系列 FPGA 配备高速 16.3 Gb/s 收发器、内置的外部内存控制器以及

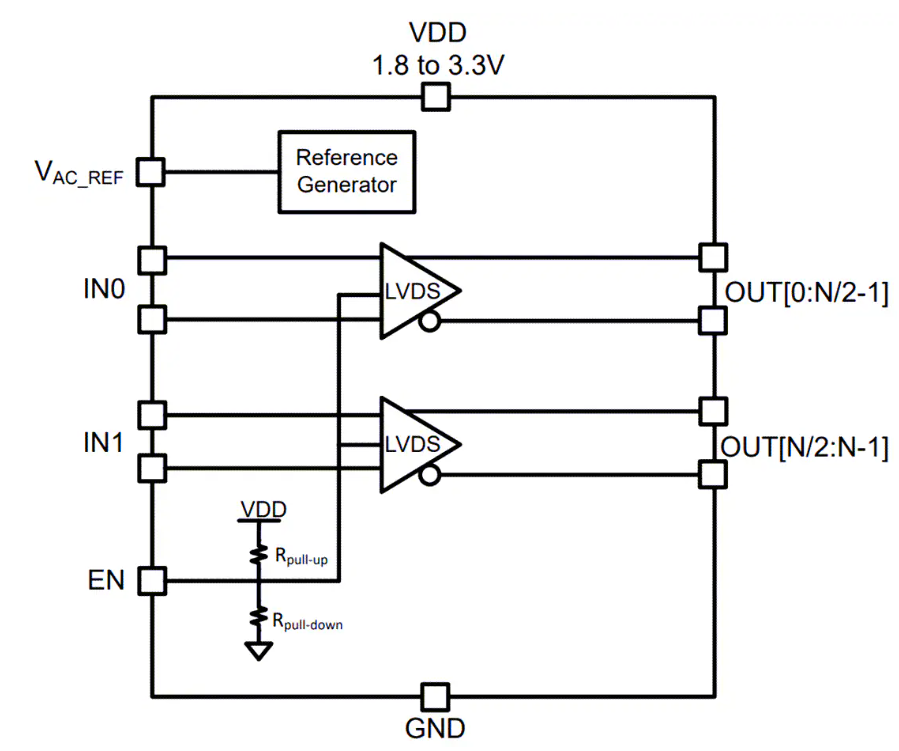

低附加抖动LVDS缓冲器LMK1D210x技术解析与应用指南

Texas Instruments LMK1D210x低附加抖动LVDS缓冲器将两个时钟输入(IN0和IN1)分配给总共多达8对差分LVDS时钟输出(OUT0、OUT7),偏移最小,用于时钟分配

AMD FPGA异步模式与同步模式的对比

本文讲述了AMD UltraScale /UltraScale+ FPGA 原生模式下,异步模式与同步模式的对比及其对时钟设置的影响。

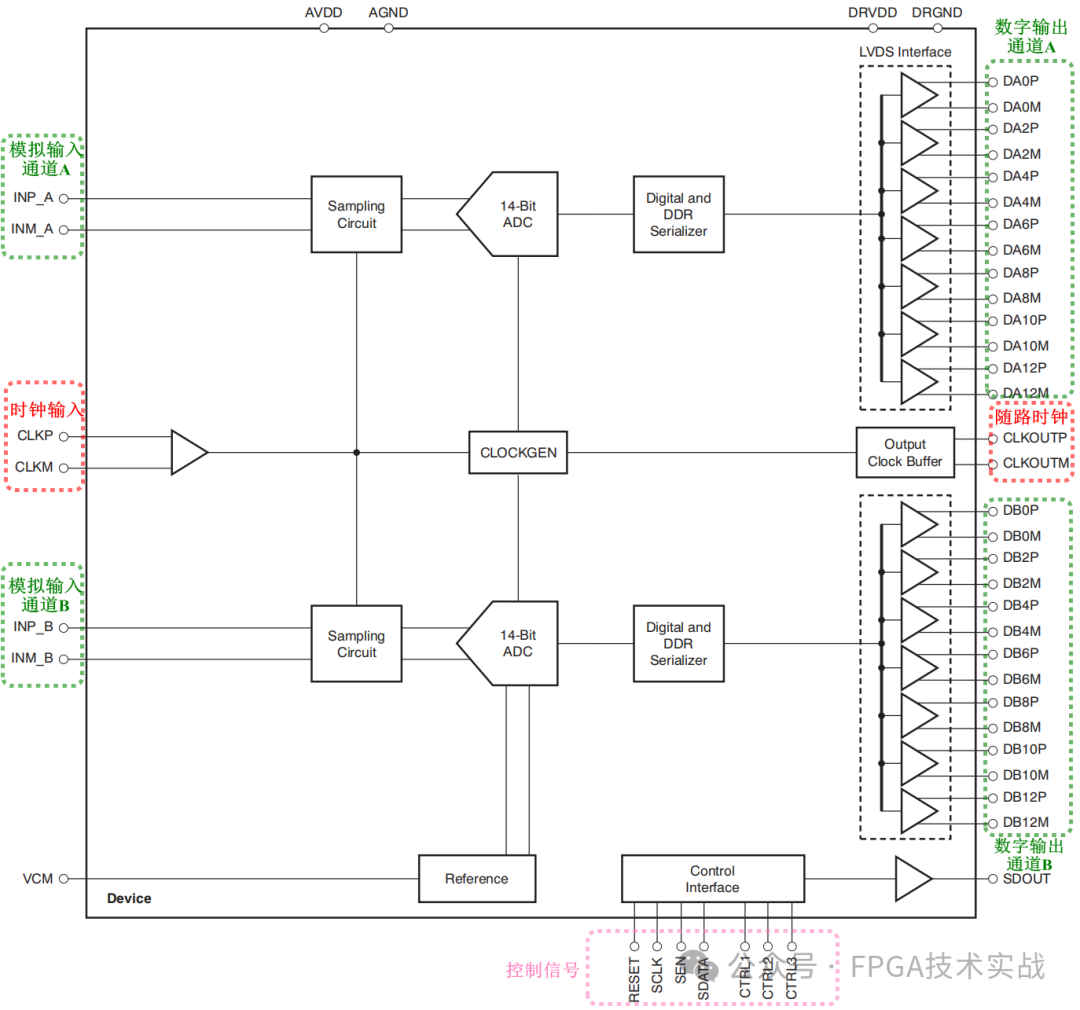

Altera FPGA与高速ADS4249和DAC3482的LVDS接口设计

引言: 本文以TI的ADS4249(ADC)和DAC3482(DAC)之间的接口为例,介绍Altera FPGA与ADC/DAC之间的DDR LVDS接口设计以及时序约束详细设计。本文介绍

AMD Spartan UltraScale+ FPGA 开始量产出货

边缘应用而设计,为业经验证的 UltraScale+ FPGA 和自适应 SoC 产品组合带来了现代化的连接、后量子密码等功能。 三款最低

正点原子AU15开发板资料发布!板载40G QSFP、PCIe3.0x8和FMC LPC等接口,性能强悍!

正点原子AU15开发板资料发布!板载40G QSFP、PCIe3.0x8和FMC LPC等接口,性能强悍!

正点原子AU15开发板搭载Xilinx Artix UltraScale+ 系列FPGA

发表于 05-30 17:04

基于RK3576的BASE64编解码

本文介绍了BASE64编解码的基本概念及其在EASY-EAI API中的实现。BASE64是一种用于传输8Bit字节码的编码方式,通过64个可打印字符表示二进制数据。EASY-EAI

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

Ultrascale是赛灵思开发的支持包含步进功能的增强型FPGA架构,相比7系列的28nm工艺,Ultrascale采用20nm的工艺,主要有2个系列:Kintex和Virtex

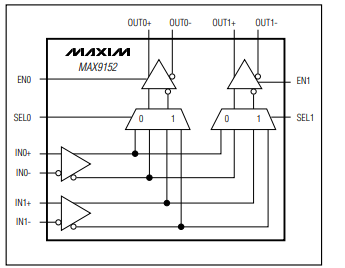

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉点开关技术手册

MAX9152 2 x 2交叉点开关专为需要高速、低功耗和低噪声信号分配的应用而设计。该器件包括两路LVDS/LVPECL输入、两路LVDS输出和两路用于设置差分输入和输出之间内部连接的逻辑输入。

ADS4229 differential LVDS最小值是多少?

关于ADS4229differential LVDS, datasheet上提到differential LVDS(ac-coupled) 正常值是0.7Vpp,请问最小值是多少?

现在我从

发表于 01-16 07:40

Marvell 88E1512-A0-NNP2I000、88E6176-A1-TFJ2C000 以太网交换机 QFN 封装

,包括集成延迟 - 这消除了在 PCB 上添加走线延迟的需要

• 在光纤接口上支持 1000BASE-X 和 100BASE-FX 以及 SGMII(仅限 88E1512 设备)

• 支持 RGMII

发表于 01-03 17:04

UltraScale FPGA中的LVDS上的1000Base-X的介绍

UltraScale FPGA中的LVDS上的1000Base-X的介绍

评论