到了今年Q4季度,Intel就正式量产32nm工艺了,2009年的时候Intel在CPU处理器架构及工艺上还是很无敌的,08年推出的Nehalem一举奠定了未来几年的基础,友商那时候完全没有还手之力。

Intel最早在2007年首次展示了32nm工艺,2009年Q4季度开始量产,最早的一批产品是Clarkdale系列的酷睿i3/i5,2010年Q1季度还有高端的Gulftown系列,比如i7-980X等,下半年还有更主流的酷睿i7-970。

与之前的45nm工艺相比,32nm工艺优点多多,首次使用HKMG材料,大幅提升了性能,SRAM面积从45nm的0.346um2减少到了0.171um2,晶体管密度提升带7MTr/mm2,晶体管性能提升22%。

当然,与现在Intel最先进的10nm工艺相比,其晶体管密度可达100MTr/mm2,比32nm工艺提升了10倍多,SRAM面积也缩小到了0.032um2,提升了5倍多。

值得一提的是,现在的酷睿处理器命名也差不多是32nm时代的酷睿处理器的10倍——酷睿i9-9900K/i7-9700K vs酷睿i7-970/980X。

不过更有意思的是,网友还对比了十年来处理器的单核性能,酷睿i7-970频率3.5GHz,GK4单核得分约为606分,而酷睿i9-9900K频率5GHz,单核得分1334分,10年来单核性能提升了一倍多点。

-

处理器

+关注

关注

68文章

20339浏览量

255302 -

cpu

+关注

关注

68文章

11332浏览量

225974 -

intel

+关注

关注

19文章

3511浏览量

191670

发布评论请先 登录

深耕干法智造,赋能固态量产 | 清研电子亮相2026高工固态电池峰会

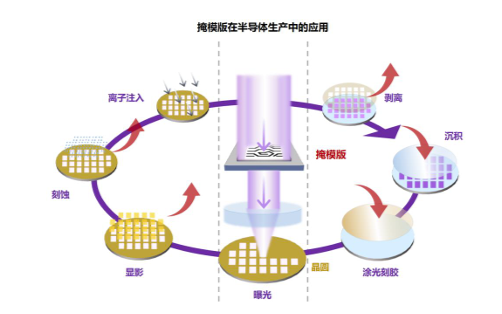

半导体制造中刻蚀工艺技术介绍

1.4nm制程工艺!台积电公布量产时间表

2nm芯片量产狂欢下,一个被忽视的“测不准”危机

热压键合工艺的技术原理和流程详解

芯源EEPROM产品的优势

半导体“光刻(Photo)”工艺技术的详解;

芯片键合工艺技术介绍

SOI工艺技术介绍

全球首款2nm芯片被曝准备量产 三星Exynos 2600

10CX150YF672E5G现场可编程门阵列(FPGA)芯片

龙图光罩90nm掩模版量产,已启动28nm制程掩模版的规划

Intel量产32nm工艺技术的回顾

Intel量产32nm工艺技术的回顾

评论