在分析place_design生成的dcp时,就要开始关注保持时间违例,尤其是当WHS < -0.5ns时。这是因为过大的保持时间违例往往会导致布线时间增大,同时,在布线阶段,工具未必能修复此类违例。

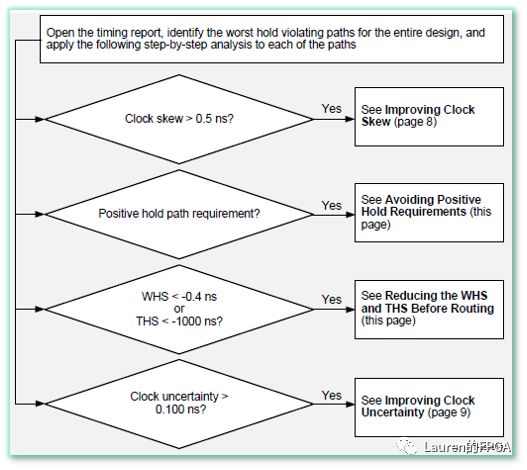

解决保持时间违例流程如下图所示。按照此流程,要逐步关注以下几个因素:

Clock Skew是否大于0.5ns

Hold Requirement是否为正(应该为0)

WHS是否小于-0.4ns或THS是否小于-1000ns

Clock Uncertainty是否大于0.1ns

图片来源 page 4, ug1292

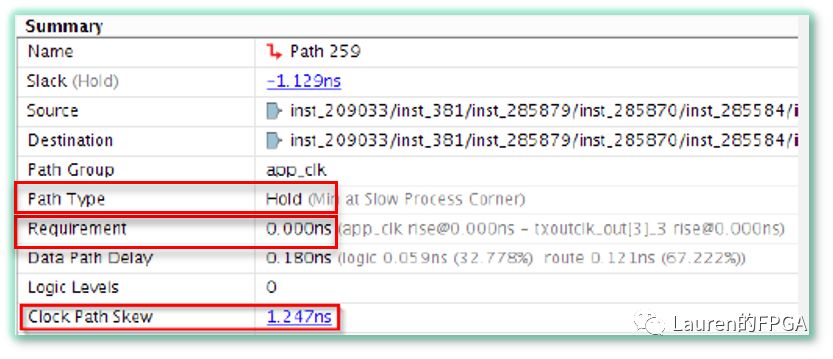

这几个指标的具体数值可在时序报告中查到,如下图所示。图中,Path Type用于确定分析的是保持时间。

图片来源 page 4, ug1292

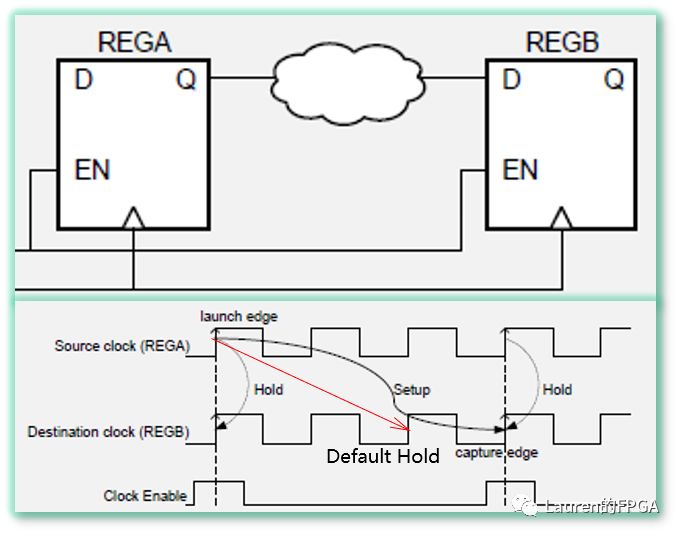

Hold Requirement为正的可能情形出现在使用多周期路径约束的时序路径中。如下图所示,时钟使能信号EN使得路径的Setup Requirement为3个时钟周期,但Hold Requirement仍应为0。

图片来源 page 4, ug1292

在此情况下,应采用如下图所示的多周期路径约束。其中的第2条约束是对hold的调整,却往往容易被遗漏。对于-hold,它表示相对于缺省捕获沿(图中的Default hold),实际捕获沿应回调的时钟周期个数。

对于过大的WHS或THS,应在布线之前做一些优化,尽可能地降低WHS和THS。为此,可在phys_opt_design阶段采取如下图所示的几个措施。

其中方法(1)是在两个同步时序元件之间插入与至相反的时钟沿触发的寄存器,将该路径一分为二,该方法的前提是建立时间不会被恶化。方法(2)至方法(4)都是在路径中插入LUT1。方法(2)只在WHS最大的路径中插入LUT1;方法(3)则是在更多的路径中插入LUT1;方法(4)则是在-directive为Explore的基础上进一步修正保持时间违例,等效于-directive Explore +-aggressive_hold_fix。

-

寄存器

+关注

关注

31文章

5590浏览量

129092 -

信号

+关注

关注

11文章

2903浏览量

79686 -

时钟

+关注

关注

11文章

1953浏览量

134561

原文标题:深度解析ug1292(4)

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

移植E203到Genesys2开发板时遇到时序问题的常见原因

E203内核移植到FPGA开发板时出现时序违例的解决方式

时序约束问题的解决办法

关于综合保持时间约束不满足的问题

是谁偷走了我的时间?RTC时间异常的秘密

赛思高保持小型时钟模块:精确时间的守护者

RK3128 Android 7.1 进入深度休眠流程分析

一文看懂芯片的设计流程

ADS1112的读出的AD值就会保持不变,好长一段时间以后才会恢复,为什么?

ADC采样保持过程的具体时间要如何确定?

使用瑞萨AnalogPAK SLG47001/03节省开发时间

解决保持时间违例流程

解决保持时间违例流程

评论