MT6825磁编码器 是纳芯微基于饱和区各向异性磁阻(AMR)技术的 18 位绝对式磁编码器,核心优势在于:仅敏感 X/Y 平面磁场方向、与磁场强度无关、天然抑制 Z 轴杂散磁场,配合全差分信号链与多级校准,在锂电吸尘器、BLDC 电机、伺服等强干扰场景下仍能实现 ±0.5° 精度与 ≤2μs 延时。本文从饱和区 AMR 物理机制、正交电桥架构、信号链抗干扰、系统级鲁棒设计四大维度,深度解析其技术内核与工程实现。

一、饱和区 AMR 敏感原理:MT6825 的物理根基

1.1 各向异性磁阻(AMR)基本效应

MT6825 采用NiFe 坡莫合金薄膜作为敏感材料,其电阻随磁化方向与电流方向夹角周期性变化,且仅在饱和磁场(30~1000mT)下稳定工作:

物理机制:电流通过铁磁材料时,电子散射概率由磁化方向与电流方向夹角决定:

磁化方向平行于电流 → 散射增强 → 电阻最大((R_{text{max}}))

磁化方向垂直于电流 → 散射减弱 → 电阻最小((R_{text{min}}))

数学模型:单 AMR 电阻随磁场夹角 (theta) 的变化满足:

( R(theta) = R_0 + Delta R cdot cos2theta )

其中:(R_0) 为零场基准电阻,(Delta R) 为磁阻变化量(约 2%~5%),(theta) 为磁场方向与电流方向夹角。

饱和区核心特性:

方向敏感、强度无关:磁化方向完全跟随外部磁场方向,输出仅与角度相关,与磁场强度波动无关。

平面选择性:仅响应平行于芯片表面的 X/Y 平面磁场,对 Z 轴杂散磁场(电机绕组漏磁、外部永磁干扰)天然免疫。

高线性、低噪声:饱和区磁阻 — 角度特性线性度优于 0.1%,固有噪声 <5nV/√Hz。

1.2 饱和区工作条件与工程意义

饱和磁场阈值:≥30mT(300 高斯),典型工作区间 50~500mT。

工程价值:

对磁铁加工误差、安装气隙(0.5~3mm)、温度导致的磁场强度衰减不敏感,大幅降低系统设计难度。

彻底消除传统霍尔传感器 “磁场过弱 / 过强导致精度下降” 的问题,鲁棒性显著提升。

二、正交 AMR 惠斯通电桥:饱和区信号采集核心

2.1 电桥架构与饱和区信号输出

MT6825 集成两对互成 45° 的 AMR 惠斯通电桥(SIN 电桥、COS 电桥),在饱和区输出纯净正交差分信号:

SIN 电桥:敏感轴与 X 轴夹角 0°,输出 (V_{text{SIN}} propto sin2theta)。

COS 电桥:敏感轴与 X 轴夹角 45°,输出 (V_{text{COS}} propto cos2theta)。

饱和区输出特性:

幅值稳定(20~50mV),不受磁场强度波动影响。

360° 无盲区、无跳变、无累积误差,实现单圈绝对角度检测。

差分输出抑制共模干扰,CMRR >100dB,SNR 较单端提升 20dB+。

2.2 电桥抗干扰设计(芯片级)

共模抑制:惠斯通电桥天然抵消电源噪声、温度漂移、电磁耦合等共模干扰。

杂散磁场免疫:仅响应 X/Y 平面磁场,对 Z 轴杂散磁场抑制比 >80dB。

温度稳定性:NiFe 合金工艺优化,-40℃~125℃ 全温域电阻一致性 <±0.5%。

Set/Reset 线圈:内置磁化复位线圈,消除磁滞与失调,提升长期稳定性。

三、信号链抗干扰设计:从模拟到数字的全链路防护

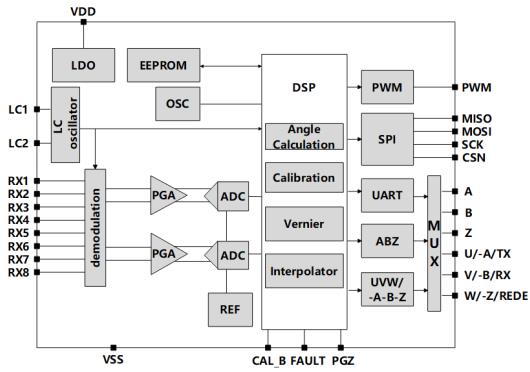

MT6825 采用低噪声模拟前端(AFE)+ 高精度同步 ADC + 数字校准 + 硬件 CORDIC 解算的全链路架构,系统性抑制干扰、保障精度。

3.1 模拟前端(AFE):微弱信号抗干扰调理

AMR 电桥输出仅数十 mV,需经低噪声、高抗干扰 AFE 放大滤波:

低噪声差分放大器:输入噪声 <10nV/√Hz,CMRR>100dB@工频,斩波技术消除直流失调。

可编程增益放大器(PGA):增益 1~64 倍可调,适配不同气隙与磁场强度,确保信号满量程输入 ADC,最大化 SNR。

抗混叠低通滤波(LPF):二阶巴特沃斯拓扑,截止频率 1~5MHz 可编程,滤除高频噪声,避免 ADC 采样混叠。

AGC 自动增益控制:自适应调整增益,抵消磁环强度波动、安装间隙变化的影响。

3.2 高精度同步 ADC:数字化抗干扰量化

架构:双通道同步采样 SAR ADC,SIN/COS 信号同时采样,保持相位关系。

关键参数:18 位分辨率,采样率 ≥1MSPS,INL <±1LSB,SNR>95dB,ENOB >17 位。

基准:内部高精度带隙基准(温漂 <10ppm/℃),降低 ADC 增益误差,保证全温域量化精度稳定。

数字滤波:可编程 IIR 低通滤波,截止频率 1~50kHz 可调,滤除 ADC 采样噪声与数字量化噪声。

多级校准补偿:

失调补偿:修正电桥、放大器直流偏置,失调从 ±50mV → <±1mV。

幅值失衡校正:补偿 SIN/COS 信号幅度不一致,失衡从 ±15% → <±1%。

正交误差校正:修正相位非 90° 偏差,正交误差从 ±1.0° → <±0.1°。

非线性补偿:多项式拟合校正 AMR 特性非线性,INL 从 ±1° → ±0.2°。

动态温漂补偿:内置 NTC 温度传感器,实时修正全温域误差,温度系数 <±0.001°/℃。

3.4 硬件 CORDIC 解算:高速低干扰角度计算

核心原理:通过硬件加速 CORDIC 算法,快速解算 (theta = frac{1}{2}arctanleft(frac{V_{text{SIN}}}{V_{text{COS}}}right)),替代传统浮点运算。

抗干扰优势:

解算延时 <1μs,系统总延时 ≤2μs,支持 25,000rpm 高速电机。

无需浮点运算,降低芯片功耗与噪声,适合嵌入式应用。

18 位精度输出,最小角度步长 0.00137°,抗微小干扰能力强。

四、系统级抗干扰设计:工程应用落地要点

4.1 硬件安装抗干扰

磁铁选型:径向磁化钕铁硼磁铁(直径 6~10mm),表面磁场 ≥50mT,确保饱和区工作。

安装参数:最优气隙 0.5~1.5mm,轴心偏心 <0.5mm,磁场倾斜 ≤±5°。

PCB 布局:

模拟 / 数字电源独立供电,单点共地,避免地环路干扰。

SIN/COS 差分线等长、平行、短距布线,包地屏蔽,远离功率回路。

电源引脚就近加 0.1μF 高频瓷片 + 10μF 电解去耦电容。

功率区与控制区物理隔离 ≥5mm,电机动力线加装磁环。

4.2 接口与软件抗干扰

输出接口:支持 SPI/ABZ/UVW/PWM 多格式输出,差分 ABZ 接口抗干扰能力最强。

软件滤波:MCU 端可叠加滑动平均、中值滤波,进一步抑制高频噪声。

故障检测:实时监测角度数据跳变、信号幅值异常,触发保护机制。

五、核心性能与抗干扰对比

5.1 MT6825 核心抗干扰参数

| 参数 | 典型值 | 说明 |

| 饱和磁场范围 | 30~1000mT | 对磁场强度不敏感 |

| Z 轴杂散磁场抑制比 | >80dB | 天然免疫电机漏磁 |

| 共模抑制比(CMRR) | >100dB | 差分输出抑制共模干扰 |

| 角度误差(校准后) | ±0.5° | 全温度范围内 <±1.0° |

| 系统延时 | ≤2μs | 高速响应,抗动态干扰 |

| 工作温度 | -40℃~125℃ | 工业级宽温,抗温度干扰 |

5.2 与霍尔编码器抗干扰对比

| 特性 | MT6825(AMR 饱和区) | 传统霍尔编码器 |

| 敏感对象 | 磁场方向(饱和区) | 磁场强度 |

| Z 轴杂散磁场 | 天然免疫 | 敏感,易受干扰 |

| 气隙容忍度 | 0.5~3mm | 0.5~1mm,要求严苛 |

| 磁场强度波动 | 无影响 | 精度显著下降 |

| 抗干扰能力 | 强(CMRR>100dB) | 弱(单端输出) |

| 高速适应性 | 25,000rpm | ≤10,000rpm |

六、总结

MT6825 以饱和区 AMR 正交惠斯通电桥为敏感核心,通过全差分信号链、多级校准补偿、硬件 CORDIC 解算、系统级抗干扰布局,实现了 “高抗干扰、高精度、高速响应” 的完美平衡。其核心价值在于:饱和区工作模式彻底解决磁场强度波动问题,天然抑制 Z 轴杂散磁场,全链路抗干扰设计保障在严苛工业 / 家电场景下稳定可靠,是锂电吸尘器 BLDC 电机、伺服系统等高精度、强干扰应用的理想选择。

审核编辑 黄宇

-

AMR

+关注

关注

3文章

485浏览量

32286 -

纳芯微

+关注

关注

3文章

442浏览量

16223

发布评论请先 登录

MT6825 18 位绝对式磁编码器:正交 AMR 电桥与角度解算机制

纳芯微 AMR/TMR 磁编码器:单芯片绝对角度检测核心技术与信号链

从 ±1° 到 ±0.01°:纳芯微霍尔/AMR/TMR 磁编码器精度体系解析

纳芯微 MT 系列磁编码器工作机理:AMR 敏感单元、差分信号调理与数字角度解算-艾毕胜电子

纳芯微AMR磁编码器MT6835/MT6826S:21位高精度角度检测技术-艾毕胜电子

MT6826S 磁性角度编码器内部信号链与 DSP 解算原理

纳芯微推出双路输出霍尔锁存器MT73xx系列

MT6825磁编芯片为伺服电机控制系统带来全角度测量能力

MT6825磁编芯片如何突破伺服电机控制精度瓶颈

MT6825磁编芯片:为伺服电机控制系统注入全角度测量新活力

MT6825超高频角度编码机制及深空探测器极端工况纳米级角分辨

纳芯微 MT6825:饱和区 AMR 敏感原理与抗干扰设计

纳芯微 MT6825:饱和区 AMR 敏感原理与抗干扰设计

评论