纳芯微磁编码器SPI接口硬件接线设计与工程实现 纳芯微(含原麦歌恩MagnTek)磁编码器(MT68xx/NSM301x系列)的SPI接口是直播云台、伺服电机、机器人关节等高精度闭环系统的核心反馈链路,其硬件接线直接决定角度数据的 稳定性、实时性与抗干扰能力 。本文以 MT6816/MT6826S/NSM3012 三款主流型号为核心,从 接口定义、硬件接线、模式配置、电源滤波、PCB Layout、EMC防护、时序匹配、工程验证 八大维度,提供完整的SPI接口硬件设计方案与可直接落地的接线图。

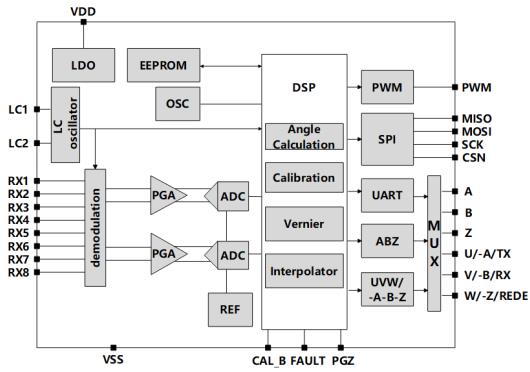

一、纳芯微磁编码器SPI接口核心特性

纳芯微磁编码器SPI接口为 标准四线制(CS/SCK/MISO/MOSI) ,支持 Mode 0(CPOL=0, CPHA=0) 与 Mode 3(CPOL=1, CPHA=1) 两种时序,最高时钟频率可达 10–16MHz ,数据传输延迟≤10μs,适配高速闭环控制场景。

1. 主流型号SPI接口参数对比 | 型号 | 分辨率 | 工作电压 | SPI时钟上限 | 模式配置引脚 | 封装 | 典型应用 |

| :--- | :--- | :--- | :--- | :--- | :--- | :--- |

| MT6816 | 14位 | 3.3V/5V | 10MHz | MODE0/MODE1 | TSSOP-16 | 云台、步进电机 |

| MT6826S | 15位 | 3.3V/5V | 16MHz | 无(默认SPI) | QFN-16 | 伺服、机器人关节 |

| NSM3012 | 14位 | 3.3V/5V | 10MHz | 无(默认SPI) | SOP-8 | 工业自动化、EPS |

2. SPI接口信号定义(通用) | 编码器引脚 | 信号名称 | 方向 | 功能说明 | 电平 |

| :--- | :--- | :--- | :--- | :--- |

| CS/CSn | 片选 | 输入 | 低电平有效,使能SPI通信 | 3.3V/5V | | SCK | 串行时钟 | 输入 | 主设备提供时钟,同步数据传输 | 3.3V/5V |

| MISO | 主入从出 | 输出 | 编码器向MCU发送角度数据 | 3.3V/5V |

| MOSI | 主出从入 | 输入 | MCU向编码器发送命令/配置 | 3.3V/5V |

| VDD | 电源 | 输入 | 3.3V或5V供电 | 3.3V/5V | | GND | 地 | 输入 | 数字地,与MCU共地 | 0V | | MODE0/MODE1 | 模式选择 | 输入 | 仅MT6816,配置SPI/ABI/PWM模式 | 3.3V/5V |

二、SPI接口硬件接线设计(含完整原理图)

(一)MT6816 SPI模式硬件接线(最常用)

MT6816需通过 MODE0/MODE1 引脚硬件配置为SPI模式: MODE1=高(3.3V)、MODE0=低(GND) 。

1. 接线原理图(MCU侧以STM32为例)具体可咨询艾毕胜电子官网http://www.abitions.com

[纳芯微MT6816] [STM32主控] ┌─────────────┐ ┌─────────────┐ │ VDD │───3.3V───────│ 3.3V │ │ GND │───GND───────│ GND │ │ CSn │───PA4────────│ SPI_NSS │ │ SCK │───PA5────────│ SPI_SCK │ │ MISO │───PA6────────│ SPI_MISO │ │ MOSI │───PA7────────│ SPI_MOSI │ │ MODE1 │───3.3V───────│ (上拉) │ │ MODE0 │───GND───────│ (下拉) │ └─────────────┘ └─────────────┘

2. 外围关键器件(必加) - CSn上拉电阻 :10kΩ,接3.3V,防止上电误触发。 - 电源去耦电容 :100nF陶瓷电容+10μF钽电容,就近贴在VDD与GND之间,滤除电源噪声。 - 模式配置电阻 :MODE1串联1kΩ上拉至3.3V,MODE0串联1kΩ下拉至GND,确保模式稳定。

(二)MT6826S/NSM3012 SPI硬件接线(默认SPI模式) 该系列无模式配置引脚, 上电即默认SPI模式 ,接线更简洁。

1. 接线原理图 [纳芯微MT6826S/NSM3012] [STM32主控] ┌─────────────┐ ┌─────────────┐ │ VDD │───3.3V───────│ 3.3V │ │ GND │───GND───────│ GND │ │ CS │───PA4────────│ SPI_NSS │ │ SCK │───PA5────────│ SPI_SCK │ │ MISO │───PA6────────│ SPI_MISO │ │ MOSI │───PA7────────│ SPI_MOSI │ └─────────────┘ └─────────────┘

2. 外围关键器件

- CS上拉电阻 :10kΩ,接3.3V。 - 电源去耦电容 :100nF+10μF,就近布局。 - 信号端接电阻 :SCK/MISO/MOSI串联22–33Ω电阻,抑制信号反射(高速SPI≥5MHz时必加)。

(三)5V MCU与3.3V编码器电平匹配设计 若主控为5V(如STM32F103),编码器为3.3V,需添加 电平转换电路 ,防止编码器引脚过压损坏。 电平转换方案(采用TXB0104芯片)[5V MCU] [TXB0104] [3.3V编码器] PA4(5V)───┐ ┌─A1───B1───CS(3.3V) PA5(5V)───┤ ├─A2───B2───SCK(3.3V) PA6(5V)───┤ ├─A3───B3───MISO(3.3V) PA7(5V)───┘ └─A4───B4───MOSI(3.3V) VCCA(5V)───────VCCA VCCB(3.3V)─────VCCB GND────────────GND

三、电源与接地系统设计(抗干扰核心)

1. 电源架构 - 单电源供电 :编码器VDD直接由MCU 3.3V LDO供电,避免开关电源噪声耦合。 - 多级滤波 : - 输入级:LC滤波(22μH电感+1000μF电解电容),抑制电源纹波。 - 芯片级:100nF陶瓷电容(高频)+10μF钽电容(低频),就近贴装。 - 数字地与模拟地单点汇接,避免地环路噪声。 2. 接地设计要点 - 编码器GND与MCU GND 直接单点连接 ,走线宽度≥2mm。 - 避免编码器地与电机功率地共线,功率地与信号地分开布局后汇接主地。 - PCB铺地:编码器区域大面积铺地,减少信号回流阻抗。

四、PCB Layout设计规范(信号完整性保障)

1. 信号线布局原则

-等长布线 :SCK/MISO/MOSI/CS四条信号线长度差≤5mm,减少时钟偏移与数据错位。

-走线长度 :SPI信号线总长度≤10cm,远离电机驱动、开关电源等强干扰源,间距≥3mm。

-阻抗控制 :单端信号特性阻抗控制为50Ω,根据PCB叠层调整线宽(4层板通常0.2mm线宽)。

-避免交叉 :SPI信号线与功率线垂直交叉,减少串扰。

2. 关键区域布局 - 编码器芯片与去耦电容 零距离贴装 ,电容引脚尽量短。

-端接电阻(22–33Ω)靠近编码器引脚放置,抑制信号反射。

-模式配置电阻(MT6816)靠近MODE0/MODE1引脚,减少干扰。

3. 4层板推荐叠层(从 top 到 bottom) 1. Top层:信号层(SPI信号线、控制信号)

2. GND层:完整地平面,屏蔽干扰 3. Power层:3.3V/5V电源层 4. Bottom层:信号层(备用信号、地线)

五、EMC防护设计(工业/户外场景必备)

1. 信号防护

-TVS管 :CS/SCK/MISO/MOSI引脚并联SMBJ3.3A TVS管,抑制静电与浪涌。

-RC滤波 :信号线串联1kΩ电阻+10nF电容,滤除高频干扰。

-屏蔽线 :编码器与MCU距离>5cm时,SPI信号线采用双绞屏蔽线,屏蔽层单端接地。

2. 电源防护

-保险丝 :VDD串联0.5A自恢复保险丝,防止过流损坏。

六、SPI时序匹配与软件配置(硬件接线配套)

1. 时序模式选择 纳芯微磁编码器 优先推荐Mode 3(CPOL=1, CPHA=1) ,数据在时钟上升沿采样,稳定性更高。

-Mode 0:空闲时钟低,数据在上升沿采样。

-Mode 3:空闲时钟高,数据在上升沿采样。 2. STM32 SPI配置示例(HAL库)

c hspi1.Instance = SPI1; hspi1.Init.Mode = SPI_MODE_MASTER; hspi1.Init.Direction = SPI_DIRECTION_2LINES; hspi1.Init.DataSize = SPI_DATASIZE_8BIT; hspi1.Init.CLKPolarity = SPI_POLARITY_HIGH; // CPOL=1 hspi1.Init.CLKPhase = SPI_PHASE_1EDGE; // CPHA=1(Mode 3) hspi1.Init.NSS = SPI_NSS_SOFT; // 软件控制CS hspi1.Init.BaudRatePrescaler = SPI_BAUDRATEPRESCALER_8; // 8MHz(72MHz/8) hspi1.Init.FirstBit = SPI_FIRSTBIT_MSB; hspi1.Init.TIMode = SPI_TIMODE_DISABLE; hspi1.Init.CRCCalculation = SPI_CRCCALCULATION_DISABLE; HAL_SPI_Init(&hspi1);

七、工程验证与常见问题排查

1. 硬件接线验证步骤

1. 通电前:用万用表测量VDD与GND阻值,确保无短路。

2. 通电后:测量VDD电压为3.3V±5%,CS引脚空闲时为高电平。

3. 通信测试:通过SPI读取角度数据,旋转磁铁时数据应连续变化,无跳变。

2. 常见问题与解决方案 | 问题现象 | 可能原因 | 解决方案 |

| :--- | :--- | :--- |

| 无数据输出 | CS未拉低、模式配置错误、接线短路 | 检查CS电平、MODE0/MODE1、接线 |

| 数据跳变/乱码 | 信号干扰、时序不匹配、时钟过高 | 优化Layout、调整时序、降低时钟 |

| 角度漂移 | 电源噪声、磁铁安装偏差、未校准 | 加强滤波、校准磁铁、执行自校准 |

| 通信不稳定 | 端接电阻缺失、阻抗不匹配 | 添加22–33Ω端接电阻、控制阻抗 |

八、纳芯微磁编码器SPI接口硬件接线的核心是 稳定供电、可靠通信、抗干扰设计、时序匹配 。设计时需严格遵循: 1. 模式配置正确 (MT6816),确保SPI模式生效。 2. 电源去耦充分 ,就近贴装滤波电容。 3. 信号线等长、短距、远离干扰 ,控制阻抗。 4. 添加端接与防护器件 ,提升信号完整性与EMC性能。 5. 时序配置匹配 (优先Mode 3),保证数据可靠传输。 本文提供的接线方案与设计规范可直接应用于直播云台、伺服电机、机器人等高精度闭环系统,结合纳芯微官方数据手册与评估板测试,可快速实现稳定可靠的SPI角度反馈链路。

审核编辑 黄宇

-

SPI

+关注

关注

17文章

1898浏览量

102083 -

磁编码器

+关注

关注

0文章

137浏览量

6688 -

纳芯微

+关注

关注

3文章

435浏览量

16216

发布评论请先 登录

纳芯微 AMR/TMR 磁编码器:单芯片绝对角度检测核心技术与信号链

纳芯微磁编码器全角度误差建模与自适应校准

纳芯微磁编码器校准机制与信号链设计:自校准流程、延时与多接口兼容性

从 ±1° 到 ±0.01°:纳芯微霍尔/AMR/TMR 磁编码器精度体系解析

纳芯微 MT 系列磁编码器工作机理:AMR 敏感单元、差分信号调理与数字角度解算-艾毕胜电子

纳芯微磁编码器:磁电转换与高精度角度解析原理深度解析

纳芯微推出MT6901双码道游标算法电感编码器芯片

磁编码器接口定义及标准接线方法

磁编码器电气接口与信号接线技术

磁编码器接口定义及标准接线方法

纳芯微传感新品:MT6901电感编码器深度解析

纳芯微磁编码器 SPI 接口硬件接线设计

纳芯微磁编码器 SPI 接口硬件接线设计

评论