AD9953:高性能直接数字合成器的探秘与应用

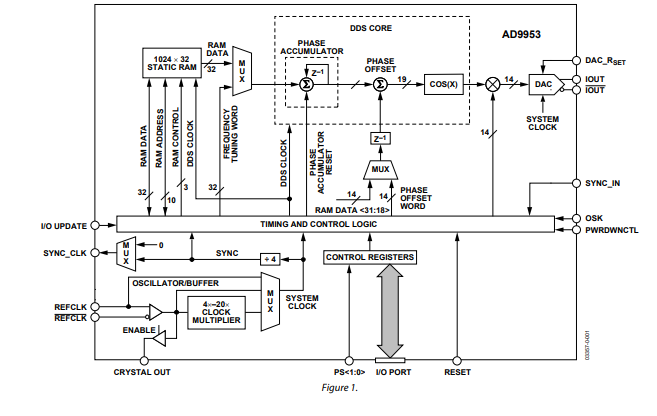

在电子工程领域,直接数字合成器(DDS)以其出色的频率合成能力和灵活性,成为众多应用场景中的关键组件。AD9953作为一款高性能的DDS芯片,由Analog Devices推出,它集成了先进的技术,为工程师们提供了强大的频率合成解决方案。本文将深入探讨AD9953的特性、工作原理、应用模式以及编程要点,帮助工程师们更好地理解和应用这款芯片。

文件下载:AD9953.pdf

一、AD9953的特性亮点

1. 高速与高精度

AD9953具备400 MSPS的内部时钟速度,集成了14位DAC,能够产生高达200 MHz的频率捷变模拟输出正弦波形。其32位的调谐字提供了精细的频率调整分辨率,可满足各种高精度频率合成的需求。

2. 出色的动态性能

在动态性能方面,AD9953表现卓越。在160 MHz(±100 kHz偏移)的AOUT输出下,其无杂散动态范围(SFDR)大于80 dB,在1 kHz偏移时,相位噪声≤ –120 dBc/Hz(DAC输出),能够有效减少杂散信号,提供纯净的输出信号。

3. 灵活的控制与同步

芯片支持串行输入/输出(I/O)控制,方便与各种微控制器和微处理器接口。同时,它具备软件和硬件控制的掉电功能,可根据实际需求灵活管理功耗。此外,AD9953还支持多芯片同步,适用于需要多通道同步输出的应用场景。

4. 丰富的功能集成

内部集成了1024 × 32的静态RAM,支持多种模式的灵活频率扫描能力。还具备相位调制功能,可实现复杂的调制需求。同时,它配备了PLL REFCLK乘法器(4×到20×)和内部振荡器,可由单个晶体驱动,为时钟输入提供了多种选择。

二、工作原理剖析

1. DDS核心

AD9953的输出频率((fo))由系统时钟(SYSCLK)频率、频率调谐字(FTW)和累加器容量((2^{32}))共同决定。具体关系如下: 当 (0 leq FTW leq 2^{31}) 时,(f{O}=(FTW)(f{S}) / 2^{32}); 当 (2^{31}< FTW<2^{32}-1) 时,(f{O}=f_{S} times(1-(FTW / 2^{32})))。 相位累加器的输出值通过COS(x)功能块转换为振幅值,然后路由到DAC。

2. 锁相环(PLL)

PLL可对REFCLK频率进行乘法运算。通过编程控制功能寄存器2的5位REFCLK乘法器部分(Bits <7:3>),可实现4到20倍的频率乘法。当PLL值改变时,需要一定时间(约1 ms)让PLL锁定。若编程值不在4到20的范围内,PLL将被旁路以节省功耗。

3. 时钟输入

AD9953支持多种时钟模式,可通过用户可编程位控制差分或单端输入时钟、片上振荡器和PLL乘法器的启用。通过CLKMODESELECT引脚、CFR1<4>和CFR2<7:3>可配置六种工作模式来生成系统时钟。

4. DAC输出

芯片集成了14位电流输出DAC,输出参考电压为AVDD,而非AGND。两个互补输出提供组合的满量程输出电流((I_{out})),可减少共模噪声,提高信噪比。满量程电流由连接在DAC_RSET引脚和DAC地(AGNDDAC)之间的外部电阻((R{SET}))控制,关系为 (R{SET}=39.19 / I{OUT})。

三、多种工作模式

1. 单音模式

在单音模式下,DDS核心使用单个调谐字,存储在FTW0中的值被提供给相位累加器。可通过向FTW0写入新值并发出I/O UPDATE来手动更改频率,还可通过相位偏移寄存器进行相位调整。

2. RAM控制模式

- 直接切换模式:适用于FSK或PSK调制。通过将RAM使能位设置为真,并将每个所需配置文件的RAM段模式控制位编程为逻辑000(b)来实现。该模式直接读取当前配置文件的RAM段起始地址处的RAM内容,无地址斜坡功能。

- 斜坡上升模式:结合分段RAM功能,允许最多四个不同的扫描配置文件被编程到AD9953中。通过将RAM使能位设置为真,并将每个配置文件的RAM模式控制位编程为逻辑001(b)来启用。

- 双向斜坡模式:使用Profile<0>信号作为控制输入,实现两个频率之间的对称扫描。通过将RAM使能位设置为真,将RSCW0的RAM模式控制位编程为逻辑010(b)来配置。

- 连续双向斜坡模式:实现两个频率之间的自动对称扫描。通过将RAM使能位设置为真,将每个配置文件的RAM模式控制位编程为逻辑011(b)来启用。

- 连续循环模式:实现两个频率之间的自动、连续单向扫描。通过将RAM使能位设置为真,将每个配置文件的RAM模式控制位编程为逻辑100(b)来配置。

四、编程要点

1. 相位偏移控制

可通过控制寄存器向相位累加器的输出添加14位相位偏移(θ),提供静态相位调整和动态相位调制两种方法。静态相位调整是将固定的相位偏移加载到相应的相位偏移寄存器中;动态相位调制则是通过I/O端口定期更新相位偏移寄存器。

2. 整形开关键控(OSK)

AD9953支持自动和手动整形开关键控模式,用于控制DAC输出的上升和下降时间,减少数字数据突发传输的频谱影响。自动模式由外部引脚(OSK)控制,根据振幅斜坡率(ARR)寄存器生成线性比例因子;手动模式允许用户直接将比例因子值写入振幅比例因子(ASF)寄存器来控制输出振幅。

3. 同步功能

AD9953提供自动同步、软件控制手动同步和硬件控制手动同步三种模式,方便多个芯片的同步操作。在同步多个设备时,需确保所有单元共享公共时钟源,I/O UPDATE信号的上升沿同步提供,且将DVDD_I/O电源设置为3.3 V。

4. 串行端口操作

AD9953的串行端口通过指令字节指定读写操作和寄存器地址,通信周期分为指令周期和数据传输周期。指令字节包含读写信息和寄存器地址,数据传输的字节数取决于所访问的寄存器。

五、应用电路示例

1. 同步本振用于上变频/下变频

在通信系统中,AD9953可作为同步本振,为上变频或下变频提供稳定的频率信号。通过低通滤波器(LPF)对输出信号进行滤波,可得到干净的本振信号。

2. 锁相环中的数字可编程分频功能

在锁相环(PLL)中,AD9953可实现数字可编程分频功能,通过调整频率调谐字,可精确控制分频比,满足不同的频率合成需求。

3. 提供独立相位偏移的I和Q载波

在通信调制系统中,两个AD9953可同步工作,提供具有独立相位偏移的I和Q载波,用于实现零陷功能,提高通信系统的性能。

六、总结与思考

AD9953以其高速、高精度、灵活的控制和丰富的功能,为电子工程师们提供了一个强大的频率合成解决方案。在实际应用中,工程师们需要根据具体需求选择合适的工作模式和编程方法,同时注意布局和电源管理,以确保芯片的性能和稳定性。

思考:在多芯片同步应用中,如何进一步优化时钟树的设计,以减少不同时钟分支的相位延迟差异?在使用整形开关键控功能时,如何根据实际应用场景选择合适的斜坡率和比例因子,以达到最佳的频谱性能?这些问题值得我们在实际设计中深入探讨。

-

频率合成

+关注

关注

1文章

33浏览量

22328

发布评论请先 登录

500 MSPS直接数字频率合成器AD9911:功能、特性与应用深度解析

AD9854:高性能CMOS 300 MSPS正交直接数字频率合成器的技术剖析

TI CDCDLP223:DLP™ 系统的高性能时钟合成器

1930–1990 MHz 高性能 VCO/频率合成器,带集成开关 skyworksinc

AD9953 400 MSPS、14位DAC、1.8 V CMOS直接数字频率合成器技术手册

AD9953:高性能直接数字合成器的探秘与应用

AD9953:高性能直接数字合成器的探秘与应用

评论