文章来源:十二芯座

原文作者:MicroX

本文介绍了集成电路制造工艺中的COAG技术。

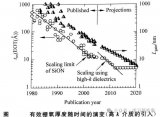

在半导体先进制程的跨代演进中,我们往往将目光聚焦于光刻机(EUV)的波长抑或是晶体管架构(从Planer到FinFET到GAA到CFET)的变革。

然而,在芯片微缩的路上,也有很多其他新技术的出现,例如COAG (Contact Over Active Gate,有源栅极上方接触) 。COAG技术的出现,正是为了解决先进制程中逻辑单元(Standard Cell)面积缩减遭遇的“拓扑学瓶颈”。

先进制程的布局

在传统的半导体制造中,晶体管的三个基本电极——源极(Source)、漏极(Drain)和栅极(Gate)——都需要通过金属接触孔(Contact)引出,以便与上层的金属互连线(Interconnects)相连。

传统非COAG布局的缺陷

在14nm及更早的工艺节点中,栅极接触孔(Gate Contact)的设计遵循“避让原则”。由于制造过程中的套刻误差(Overlay Error)和等离子体刻蚀的局限性,栅极接触孔必须放置在有源区(Active Area)之外,即位于浅沟槽隔离(STI)区域的上方。

这种布局导致了严重的面积浪费:

横向间距限制:为了防止接触孔在刻蚀时误伤栅极边缘或引起源漏极短路,必须在栅极和接触孔之间留出足够的安全间距(Registration Margin)。

单元高度(Cell Height)膨胀:由于接触点在侧方,逻辑单元的高度必须增加,以容纳这些额外的接触区。可以称之为“空间税”,直接限制了晶体管密度(MTr/mm²)的提升。

COAG技术

COAG技术的本质是将原本“横向并列”的布局改为“纵向堆叠”。它允许接触孔直接落在有源栅极(Active Gate)的正上方。

物理架构的拓扑演进

在COAG架构下,晶体管的平面布局发生了根本性变化。通过取消侧方的接触区,逻辑单元的高度得到压缩。

Track Height(绕线轨道高度)的突破:从传统的9T(9条金属线轨道)降低到6T甚至5T。这意味着在同样的芯片面积下,可以容纳多出30%以上的逻辑门。

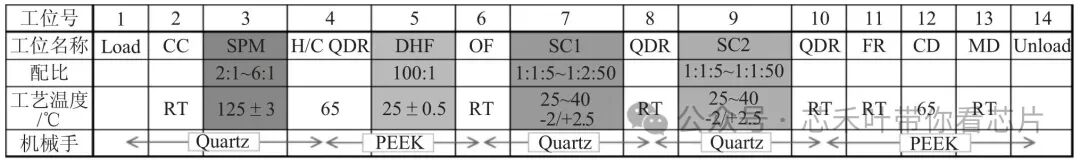

自对准策略(Self-Aligned Strategy)

COAG的实现依赖于自对准工艺(Self-Aligned Contact, SAC)。在制造过程中,工程师首先在栅极金属上方沉积一层非常薄但极其坚硬的绝缘保护层(通常是氮化硅或特殊的低k材料掩模)。

选择性刻蚀:当进行接触孔刻蚀时,化学试剂和等离子体能够区分“层间介质”和“栅极保护层”。刻蚀过程会自动在碰到栅极保护层时“减速”或“停止”,从而确保孔洞精准地落在栅极顶部而不向四周偏移,避免了灾难性的短路。

钴(Cobalt)互连:解决寄生电阻

随着接触孔(Contact Via)的直径缩小到10nm以下,传统的金属插塞材料——钨(Tungsten)遇到了巨大的瓶颈。

钴的优势:Intel在10nm节点率先在大规模量产中引入钴替代钨作为M0层和接触孔材料。钴具有更长的平均电子自由程和流动性,能够完美填充高深宽比的COAG孔洞,且电阻率远低于同尺寸下的钨。这解决了COAG结构因接触面积减小可能导致的信号延迟(RC Delay)问题。

未来挑战

尽管COAG成功将摩尔定律延续到了3nm节点,但随着制程向2nm(18A)演进,物理极限再次降临。

1. 散热与可靠性的博弈

由于接触点直接位于晶体管最热的部分(栅极)上方,热量散发的路径变得更加拥挤。在高频运行下,COAG结构可能产生微小的热应力,导致介质层开裂。未来的研究重点在于寻找具有更高导热率的绝缘掩模材料。

2. 与背面供电(BSPDN)的结合

在2nm节点,Intel的PowerVia和台积电的背面供电技术将彻底改变互连架构。届时,电源线将移至晶圆背面,而正面的空间将完全留给信号线和COAG结构。

3. CFET

在1nm节点,n型和p型晶体管将垂直堆叠(CFET)。在这种情况下,COAG将演变为一种复杂的“3D垂直通孔”技术,不仅要在栅极上方接触,还要在多层堆叠的栅极之间进行选择性接触。

参考文献

1.Intel

2.VLSI 2024

3. Razavieh, A., et al, “FinFET with Contact over Active-Gate for 5G Ultra-Wideband Applications”, VLSI 2020 Symposium, paper JFS2.5.

-

集成电路

+关注

关注

5463文章

12669浏览量

375607 -

半导体

+关注

关注

339文章

31192浏览量

266321 -

制造工艺

+关注

关注

2文章

215浏览量

21315

原文标题:COAG(Contact Over Active Gate)技术原理与工艺演进

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

集成电路制造工艺中的COAG技术介绍

集成电路制造工艺中的COAG技术介绍

评论