从DUV到EUV,掩膜版为什么越来越难?Reticle的结构、制造与缺陷

在晶圆厂里,最像“押运黄金”的物件之一不是晶圆,而是Reticle(倍缩式掩模/掩膜版):一块看似普通的玻璃板,却承载着芯片每一层电路图形的“母版”。它被装进专用承载盒、按资产编号追溯、按寿命与风险分级管理——原因只有一个:它一旦出问题,缺陷可能会被复制到整片晶圆的无数颗Die(芯片裸片)里,直接拉低良率、拖慢产线节拍、抬高单位成本。聊光刻,大家习惯从“光刻机”说起;但从制造工程的视角,光刻其实是一套“系统工程”:光源、投影光学、工艺胶、刻蚀、量测、以及Reticle共同决定你能不能把图形稳定地印出来。本文用一篇长文把Reticle讲透:它是什么、怎么工作、长什么样、怎么制造、为什么误差会被放大、EUV(Extreme Ultraviolet,极紫外)时代又为什么更难。一句话总结:Reticle把“电路设计”变成“可量产的物理图形”,它既是制造能力的上限,也是工艺波动的放大器。

01Reticle是什么:为什么Mask和Reticle常被混用?

光刻(Photolithography)的核心任务,是把设计数据里的图形(Pattern)转印到晶圆(Wafer)上。投影式光刻系统把光投射到“蓝图”上——这张蓝图就叫Mask/Reticle(Mask/Reticle,掩膜版)。ASML把它概括为:光被投射穿过(或在EUV里反射自)“mask or reticle(掩膜/倍缩掩膜)”,再成像到晶圆上。工程语境里,“Reticle”常特指用于2X/4X/5X等倍率缩小投影曝光的掩膜版;而“Photomask(光掩模/光罩)”更像一个总称。中文维基百科也用“倍缩式掩模(reticle)”来强调:掩膜图形通常会缩小4~10倍投影到晶圆上(现代多见4倍)。理解Reticle的第一把钥匙,是“层”的概念:一颗芯片并不是一次曝光完成,而是经过很多层工艺叠加——每一层(例如多晶硅、接触孔、金属互连等)通常都对应一张或多张掩膜版。也就是说,一套工艺要稳定量产,既要机台稳定,也要整套Reticle在规格、缺陷、可印性上都“可控”。

02它怎么“印”出芯片:缩小成像 + 步进/扫描

Reticle更像一枚“邮票”,而不是整片晶圆的“地图”。曝光时,光刻机把这枚“邮票”一次次投到晶圆不同位置,形成重复阵列;这就是“步进重复(step-and-repeat)”或“步进扫描(step-and-scan)”。步进扫描可以理解为:Reticle与晶圆在曝光过程中按严格比例、同步运动,让投影系统像“扫面仪”一样把图形扫过曝光区域。为什么缩小成像重要?因为掩膜上图形更大、更容易加工到足够精度,再由投影光学按倍率缩小得到更小的晶圆图形。Chris Mack给出一个典型工程描述:掩膜常见为6英寸方形熔融石英(Fused Silica)基板,吸收层可为铬(Cr,Chromium)或钼硅(MoSi,Molybdenum Silicide,硅化钼),且常见4X倍率。这里有个常被忽略的“乘法效应”:同一张Reticle会在一片晶圆上曝光许多次,而一片晶圆又会切出许多颗芯片——因此Reticle上的系统性问题,不是影响“一颗芯片”,而可能影响“一整片晶圆的一整批芯片”。这也是为什么掩膜规格、寿命管理、以及缺陷处置会如此严苛。

03Reticle长什么样:材料、对准标记、以及Pellicle的“离焦防尘”

一块Reticle通常由高平整度石英基板 + 吸收层(Absorber)图形构成;先进节点的掩膜基板表面粗糙度、平整度与缺陷密度要求都极高,因为它既是“图形载体”,也是成像系统的一部分。KLA在Reticle制造介绍中提到:Reticles built upon blanks(reticle blanks,掩膜空白基板),其基础是石英基板上沉积吸收膜层;任何缺陷与位置误差都可能影响良率。但Reticle上真正“工程感”的地方,是那些为量产服务的细节:对准标记(Alignment Mark,对准标记)、监控结构、条码/ID(Identification,身份识别)等。它们帮助工厂完成三件事:

- 让每一层图形与前一层对齐(Overlay,叠加对准);

- 让关键尺寸CD(Critical Dimension)和焦距/剂量漂移可被量测与反馈;

- 让每一次上机、清洗、检测、维修都可追溯。

最关键的“配件”是Pellicle(掩膜防尘膜/防尘罩)。它是一层张紧薄膜,距离掩膜图形面通常为毫米级。SPIE对其机理的解释很直白:颗粒落在Pellicle上时,离成像平面有毫米级距离,而先进光刻的焦深DOF(Depth of Focus)往往只有微米量级,因此颗粒会严重离焦、难以打印;同时Pellicle本身也会成为成像系统的一部分,其光学性质需要纳入考虑。在DUV(Deep Ultraviolet,深紫外)里,Pellicle材料要兼顾透过率与耐光;AGC在其材料介绍中提到,Pellicle需要在ArF(Argon Fluoride,氟化氩,193 nm)与KrF(Krypton Fluoride,氟化氪,248 nm)等曝光波长环境下使用,并强调材料的深紫外透过特性。

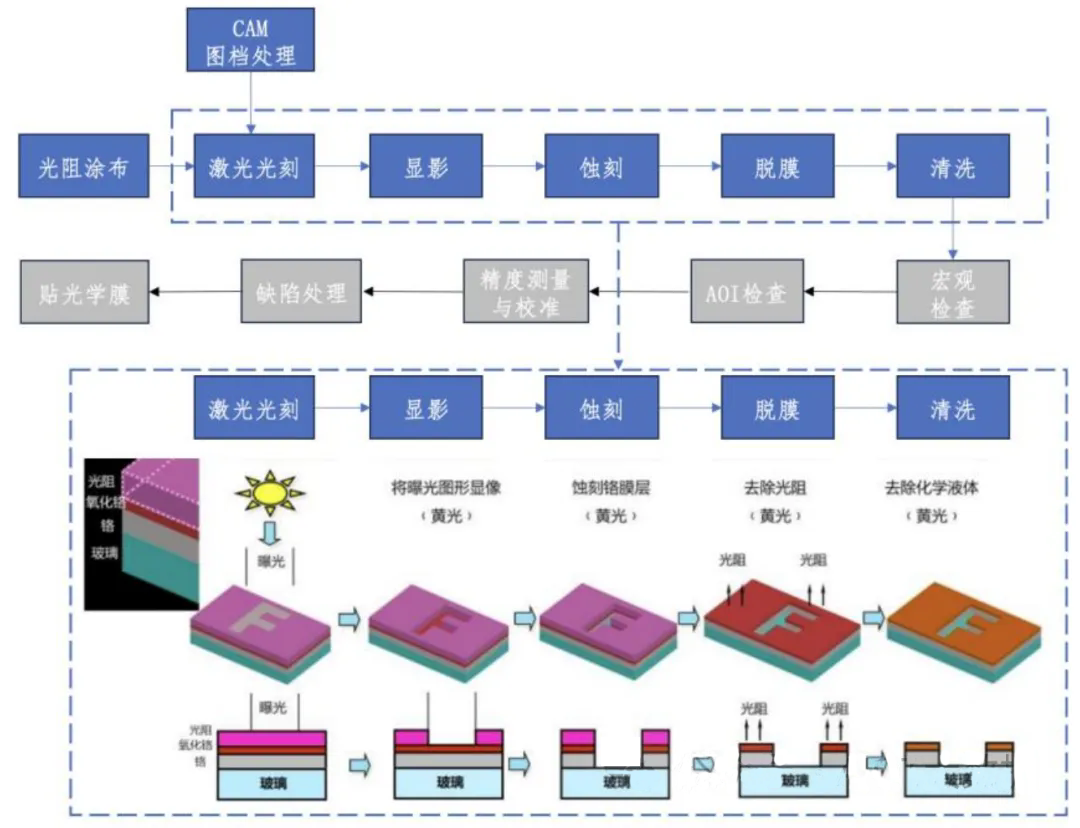

04一块Reticle怎么做出来:数据准备→电子束写版→刻蚀→检测→可印性判定

Reticle制造可以理解为“在玻璃上再做一遍微缩的半导体工艺”,并且对缺陷更敏感。KLA指出:无缺陷Reticle对良率至关重要,因为掩膜缺陷或图形位置误差会在生产晶圆上被复制到很多Die里。一个典型流程可以抓住五个关键环节:

- 掩膜空白基板(Blank)准备:先有高规格石英基板与吸收膜层(例如铬层)。这一步决定了“底子干不干净”:一旦空白基板里存在缺陷,后续再精密的写版与刻蚀也只能“带着缺陷往下走”。

- 数据准备:OPC与“让机器能写”的版图处理:版图不是直接写上去就能印好。成像、胶反应、刻蚀都会让线条变形,因此要做OPC(Optical Proximity Correction,光学邻近效应校正):在Reticle上加入辅助结构(例如SRAF,Sub-Resolution Assist Feature,亚分辨率辅助特征)或做边界修正,抵消邻近效应,让最终晶圆图形更接近目标。

- 写版:电子束曝光:掩膜主图形常用E-beam(Electron Beam,电子束)在抗蚀剂里直接“写”出来,再显影。Chris Mack的课程材料把“用电子束曝光抗蚀剂来做掩膜”作为典型流程描述。

写版阶段还有一个现实难题:先进节点的掩膜图形越来越“碎”,OPC/ILT带来大量细小边界与辅助结构,数据量暴涨、写版时间变长,任何漂移都可能在后续显影与刻蚀里体现为CD不均或位置误差。于是“写得快”与“写得准”往往要一起做工程权衡。 - 刻蚀与清洗:把抗蚀剂图形转移到吸收层里:写完、显影后,图形还只是“抗蚀剂窗口”,需要把窗口刻蚀到铬/吸收层里,再去胶、清洗。这个阶段会影响线边粗糙度LER(Line Edge Roughness)、残留缺陷与污染风险。

- 检测与“可印性”判定:缺陷不只要看见,还要判断会不会印:先进节点的难点之一是“看见≠危险,危险≠看得见”。因此产线会把缺陷分级处置:先高通量检测找到疑似缺陷,再用复检/模拟工具判断缺陷是否会在晶圆上打印。ZEISS的AIMS(Aerial Image Measurement System,空中像测量系统)强调其在与扫描仪等效的光学条件下,能在Mask Shop阶段评估掩膜打印表现与缺陷可印性。

05为什么“差一点”会变成“差很多”:MEEF、Overlay、缺陷复制与良率的链式反应

先进节点里,Reticle的误差往往不会“等比例传到晶圆”,而可能被放大。背后可以用三条链来理解:

链1:尺寸链——从Reticle误差到晶圆CD漂移MEEF(Mask Error Enhancement Factor,掩膜误差放大因子)描述的是:Reticle上的尺寸/形状变化,最终在晶圆CD上引起的变化比例。Lithoguru的教程指出:任何导致成像过程非线性的因素都会让MEEF偏离1;当特征尺寸逼近分辨率极限时,系统非线性增强,MEEF问题更突出。这意味着:你以为掩膜改动“很小”,但在某些工艺窗口里,晶圆上的CD可能“变得更大”。再把“误差”拆得更细一点,你会发现它并不只来自掩膜图形本身:

- 掩膜受温度与应力会发生微小形变;

- 吸收层边缘的粗糙会改变局部对比度;

- 污染薄膜会改变透过/反射特性。

很多时候,工程团队要做的是把这些误差的来源“定量化”,再用量测与反馈把它们关进规格范围里。

链2:位置链——Overlay对齐的“多层叠加效应”一颗芯片要叠很多层图形,任何一层的对准偏差都可能造成开路、短路或性能漂移。Overlay(叠加对准)不仅取决于机台平台与量测系统,也与Reticle的对准标记、热应力、污染状态相关。更现实的是:Overlay不是“单次误差”,而是“层层累积”的统计问题——层数越多,窗口越紧。

链3:复制链——缺陷从“局部”变成“系统性”Reticle是母版,缺陷会在一片晶圆上被重复曝光许多次,再扩散到许多颗芯片上。KLA强调:Reticle缺陷或图形位置误差会在生产晶圆上被复制到很多Die里,因此无缺陷Reticle是高良率的关键。这也是为什么缺陷处置要引入“可印性判定”:不是所有缺陷都要报废,但必须明确哪些缺陷在当前照明、焦距、剂量条件下会打印出来。

06在晶圆厂里怎么“护送”它:Pod、微环境、污染控制与追溯

Reticle的敌人之一是污染(Contamination),尤其是颗粒与分子污染。为了把运输、存储、转运中的环境变量最小化,行业普遍使用专用承载盒(Reticle Pod,掩膜承载盒)。Entegris在产品介绍中明确强调:Reticle SMIF Pod(SMIF,Standard Mechanical Interface,标准机械接口)用于在存储与运输中保护贵重Reticle,并提供高水平的污染防护。相关专利也把SMIF载具描述为:通过过滤等方式降低载具内部的化学与颗粒污染,从而形成可控的“微环境”。有些工厂还会配合惰性气体/过滤换气的存储柜(Purge Cabinet,净化柜)来控制分子污染与湿度波动:对先进掩膜来说,“存放方式”本身就是工艺的一部分。在工厂现场,Reticle管理往往会做到“流程化+系统化”:

- 上机前:状态确认、清洁度/外观检查、必要时复检;

- 下机后:回盒、记录使用次数/批次/机台、异常处置与隔离;

- 生命周期:按风险分级(例如关键层/非关键层)、按缺陷/污染历史决定是否维修、报废或降级使用。

这些看似繁琐的动作,本质是为了让问题“可定位、可追溯、可止损”。

07EUV时代的Reticle:从透射到反射,多层膜结构、掩膜3D效应与Pellicle极限

EUV(Extreme Ultraviolet,极紫外)把波长降到13.5 nm左右。中文维基百科指出:EUV波长极短、易被空气吸收,因此需要在真空环境中完成;同时EUV光掩模与传统光掩模截然不同,采用复合多涂层反射结构。英文维基百科在“Masks”章节中给出EUV掩膜的关键结构:通过多对Mo/Si(Molybdenum/Silicon,钼/硅)交替层形成多层膜反射镜(multilayer stack,多层膜堆栈),再在其上用钽基吸收层定义图形;其反射依赖布拉格衍射,并对入射角与波长敏感。条目还提到,多层膜通常由约40–50对钼/硅交替层组成,并可能有保护性的钌(Ru,Ruthenium)封帽层等结构。这直接带来三类工程难题:

- 掩膜本身更像“精密光学元件”:反射式、斜入射、厚度明显的堆栈结构,使掩膜三维效应(Mask 3D effects,掩膜三维效应)更突出:同样的线条在不同方向、不同位置可能出现成像差异;边缘与非对称结构也更容易引入系统性偏差。

- 缺陷更难:不仅在表面,还可能“埋在多层膜里”:英文维基百科提到,EUV掩膜缺陷可能埋在多层膜堆栈内部或其表面,缺陷控制是商业化关键问题之一。这让检测、修补与缺陷处置更复杂:你不仅要知道“有没有缺陷”,还要知道它会以何种方式影响反射相位与成像对比度。

- EUV Pellicle更难:透明、耐热、低形变、低污染要同时满足:Photomask条目与SPIE对Pellicle的说明都强调:Pellicle作为防尘膜能让颗粒远离掩膜图形面以避免打印,但Pellicle也会成为成像系统的一部分,需要计入光学影响。到了EUV,这个“必须件”要扛更高功率、更苛刻环境,难度指数级上升。

08未来趋势:更多“计算”、更多“掩膜”、High-NA时代耦合加深

未来的Reticle会越来越像“计算结果”。从OPC到更激进的ILT(Inverse Lithography Technology,逆向光刻技术),掩膜图形会更复杂、更曲线化,只为换取更稳定的晶圆图形与更大的工艺窗口。与此同时,多重图形化(Multiple Patterning)在不少场景仍难避免:当单次曝光无法满足间距要求时,需要把一层图形拆成两次、三次甚至更多次曝光/刻蚀流程。它意味着更多张Reticle、更高的Overlay压力、更复杂的检测与缺陷处置链条。当High-NA EUV推进时,掩膜三维效应与缺陷可印性会更敏感,“掩膜—光学—工艺”的耦合将进一步加深——Reticle不再只是“模板”,更像“硬件+数据产品”的混合体。

原创声明: 本文综合公开资料梳理,转载需授权。

-

芯片

+关注

关注

463文章

54379浏览量

468988 -

晶圆

+关注

关注

53文章

5445浏览量

132713 -

芯片制造

+关注

关注

11文章

734浏览量

30527

发布评论请先 登录

光掩膜(mask)制造流程和检测流程及其他资料整理

国内首条G11掩膜板项目开工 成都或成我国最大掩膜版制造基地

芯片制造真正的“底片”——Reticle(掩膜版)全解析

芯片制造真正的“底片”——Reticle(掩膜版)全解析

评论