——从高速串行链路看DP线对显示同步的隐性门槛

当你将DisplayPort线插入显卡与显示器,“咔哒”一声锁扣就位,屏幕随即亮起——

物理连接宣告完成。系统识别出4K@144Hz、HDR、G-SYNC,一切参数如预期般呈现。

但深入使用后,你可能察觉:

游戏快速转向时画面有轻微“拖影感”;

视频剪辑时间轴拖动不够跟手;

音画偶尔错位,尤其在高帧率播放时更明显。

物理连接完成了,但信号的时序对齐,其实还没真正开始。

在高速数字显示时代,能否“亮屏”只是第一步;

真正的体验,取决于数据是否在正确的时间被正确接收——而这,高度依赖DP线的时序保真能力。

时序对齐:高刷与同步功能的隐形基石

DisplayPort采用高速串行差分传输,将像素数据、音频、控制指令打包成微包(Micro-packet)流。

要实现无撕裂、低延迟、精准HDR,不仅要求数据完整,更要求所有通道的数据包严格对齐到达。

这一过程称为“时序对齐”(Timing Alignment),它依赖两个关键条件:

通道间偏斜(Lane Skew)极小:四条主数据通道必须几乎同时抵达;

时钟恢复精度高:接收端需从数据流中准确提取时钟,重建像素时序。

若DP线制造工艺粗糙,即使物理连通,也会破坏时序一致性:

通道长度不一致→ 数据包错位 → 接收端需缓冲等待 → 引入延迟;

阻抗波动或介质不均→ 信号传播速度差异 → 眼图抖动增大 → 时钟恢复失准;

高频衰减严重→ 信号边沿变缓 → 判决时刻漂移 → 帧间隔不稳定。

结果就是:系统虽能显示画面,却无法真正实现“跟手”“跟眼”的同步体验。

为什么普通DP线难以保障时序?

多数低价DP线仅满足“通电即用”的基本需求,但在时序控制上存在先天不足:

手工绞合或无控绞距:各差分对长度误差达数厘米,导致纳秒级偏斜;

绝缘材料介电常数不均:信号在不同通道中传播速度不一致;

接头内部走线随意:高速信号路径突变,引发反射与群延迟;

未进行Skew或抖动测试:出厂仅验证“能否点亮”,不验证“是否准时”。

这些问题在1080p@60Hz下影响微弱,

但在4K@120Hz+VRR+DSC的复合负载下,会被显著放大,

表现为“总觉得哪里不太顺”,却难以 pinpoint 源头。

时序保真的工程实践

真正面向高性能场景的DP线,会在制造环节严格控制时序变量:

精密自动化绞合设备:确保四条主通道长度误差控制在毫米级内;

统一低损耗发泡PE绝缘层:维持各通道传播速度一致;

接头内部信号路径等长设计:避免PCB走线引入额外偏斜;

出厂进行Skew与抖动实测:确保通道间时延差<0.3纳秒,满足VESA HBR3时序容限。

以山泽推出的高精度DisplayPort 1.4线为例,其在产线阶段即通过矢量网络分析仪(VNA)和误码仪验证通道一致性,并模拟G-SYNC动态刷新场景,确保在帧率剧烈波动时,时序依然稳如磐石。

用户可感知的时序价值

当DP线真正保障时序对齐,体验差异是真实可感的:

电竞玩家在《CS2》中快速甩枪,画面响应毫无迟滞;

视频调色师拖动时间轴,每一帧预览即时呈现;

家庭影院播放高帧率演唱会,鼓点敲击与画面震动完全同步。

这种“理所当然”的协调,

不是软件补偿的结果,

而是物理层时序可靠带来的自然状态。

结语

物理连接的完成,只是故事的序章;

时序对齐的成功,才是流畅体验的正文。

在追求极致响应的时代,

我们真正需要的,

不是一根“插得进”的线,

而是一段能让每一比特都在正确时刻抵达的通路。

因为再高的刷新率,

也经不起几纳秒的无声偏移。

而那段沉默的DP线,

或许正决定着你的画面,

是“刚好赶上”,

还是“始终同步”。

审核编辑 黄宇

-

时序

+关注

关注

5文章

411浏览量

38997

发布评论请先 登录

JL杰理AC696N开发板引脚速查:AC6966B开发板关键接口连接图

杰理蓝牙音频产品开发,五分钟上手:从杰理AC696N开发板出厂直观的功能体验开始

JL杰理AC696N开发板引脚速查:AC6966B开发板关键接口连接图

伺服电机正余弦编码器的相位对齐方式

CW32操作FLASH地址对齐的要求

基于蜂鸟E203处理器的DMA模块设计

DDR200T中DDR的使用与时序介绍

辅助偏置电源启动时序的精确验证

LP5899-Q1 汽车级SPI兼容连接芯片总结

LP5899 SPI兼容连接设备技术文档总结

BLE连接未启动的原因?

配线架和理线架是一个东西吗

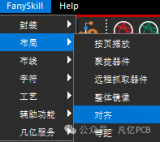

Allegro Skill布局功能--器件丝印过孔对齐介绍与演示

FPGA时序约束之设置时钟组

理连接完成了,时序对齐还没开始

理连接完成了,时序对齐还没开始

评论