LMX2485x 3 - GHz Delta - Sigma低功耗双PLLatinum™频率合成器深度解析

在电子设计领域,频率合成器扮演着至关重要的角色。今天我们来深入探讨德州仪器(TI)的LMX2485x 3 - GHz Delta - Sigma低功耗双PLLatinum™频率合成器,它在众多应用场景中展现出了卓越的性能。

文件下载:lmx2485.pdf

一、产品概述

LMX2485x系列包含LMX2485和LMX2485E两款产品,是低功耗、高性能的delta - sigma分数N PLL,还带有辅助整数N PLL。该系列采用了TI先进的工艺制造,具有丰富的特性和广泛的应用前景。

二、产品特性亮点

2.1 四重模数预分频器

- RF PLL:支持8/9/12/13或16/17/20/21的预分频比,为不同的频率需求提供了灵活的选择。

- IF PLL:支持8/9或16/17的预分频比,满足中频应用的要求。

2.2 先进的Delta - Sigma分数补偿

- 具备12位或22位可选的分数模数,可根据具体应用灵活配置。

- 高达4阶可编程的Delta - Sigma调制器,能够有效降低近端杂散,提高频率合成的精度。

2.3 改善锁定时间的特性

- 集成了超时计数器的快速锁定/周期滑动减少功能,只需单字写入即可实现,大大缩短了锁定时间。

2.4 宽工作范围

- LMX2485 RF PLL:工作频率范围为500 MHz至3.0 GHz。

- LMX2485E RF PLL:工作频率范围更宽,从50 MHz至3.0 GHz,适用于更多不同频率的应用场景。

2.5 实用特性

- 数字锁定检测输出:方便工程师实时监测PLL的锁定状态。

- 硬件和软件电源控制:可灵活控制芯片的功耗,在不同的工作模式下实现低功耗运行。

- 片上输入频率倍增器:有助于提高参考频率,减少因晶体参考频率带来的相位检测器频率限制。

- RF相位检测器频率高达50 MHz:能够满足高频应用的需求。

- 2.5至3.6 V工作电压,ICC = 5.0 mA:低功耗设计,适合电池供电的应用。

三、应用领域

LMX2485x适用于多种应用场景,包括但不限于:

- 蜂窝电话和基站:在无线通信领域,低功耗和低杂散的特性能够有效提高通信质量。

- 直接数字调制应用:其精细的频率分辨率和快速编程速度,非常适合直接数字调制的需求。

- 卫星和有线电视调谐器:宽工作范围和低杂散性能,可确保信号的稳定接收和解调。

- WLAN标准:满足无线局域网对频率合成的要求,提供稳定的频率输出。

四、详细功能剖析

4.1 TCXO、振荡器缓冲器和R计数器

振荡器缓冲器由信号源(如TCXO)单端驱动,OSCout引脚提供输入信号的缓冲输出。R计数器将TCXO频率分频至比较频率,为后续的相位检测提供合适的参考信号。

4.2 相位检测器

IF PLL的最大相位检测器工作频率较为明确,而RF PLL由于是分数型,情况稍复杂。LMX2485 RF PLL的最大相位检测器频率为50 MHz,但在某些情况下,由于N计数器的非法分频比,可能无法达到该频率。晶体参考频率也会对相位检测器频率产生限制,不过频率倍增器可以在一定程度上缓解这一问题。在选择相位检测器频率时,需要权衡相位噪声和锁定时间等因素。较高的频率可以降低相位噪声,但可能会增加锁定时间,并且环路滤波器中的电容可能会变得较大。

4.3 电荷泵

大多数情况下,电荷泵输出处于高阻抗状态,只有三态泄漏电流。当相位检测器检测到相位误差时,电荷泵会输出快速校正脉冲,其宽度与相位误差成正比。IF PLL的电荷泵电流不可编程,而RF PLL的电荷泵电流可在16个步骤中进行编程,并且在PLL锁定时可以使用更高的电荷泵电流来缩短锁定时间。

4.4 环路滤波器

环路滤波器的设计较为复杂。对于delta - sigma PLL,环路滤波器的阶数通常应比Delta - Sigma调制器的阶数高至少一阶,以确保能够有效抑制调制器产生的噪声。虽然理论上使用4阶调制器时需要5阶环路滤波器,但实际中通常使用4阶滤波器。目前有许多仿真工具和参考资料可用于环路滤波器的设计,例如TI网站上提供的相关资源。

4.5 N计数器和高频输入引脚

N计数器将VCO频率分频至比较频率。由于使用了预分频器,N值存在一定的限制。高频输入引脚(FinRF和FinIF)的布局需要特别注意,TI建议VCO输出先经过电阻衰减器,再通过直流阻断电容连接到这些引脚。当走线长度足够短(小于波长的1/10)时,衰减器可能不是必需的,但仍建议使用约39 Ω的串联电阻来隔离PLL和VCO。直流阻断电容的选择应根据频率而定,至少为27 pF。互补高频引脚FinRF*通常会并联一个电容,典型值为100 pF,以确保在PLL工作频率下阻抗接近交流短路。

4.6 数字锁定检测操作

RF PLL的数字锁定检测电路通过比较相位检测器输入相位与RC产生的延迟ε来判断锁定状态。当相位误差连续5个参考周期小于ε RC延迟时,判定为锁定状态(Lock = HIGH);锁定后,RC延迟变为约0。当相位误差大于该延迟时,判定为失锁状态(Lock = LOW)。为了在较高比较频率下准确检测锁定状态,当比较频率超过20 MHz时,建议启用DIV4位,将RF PLL比较频率除以4。

4.7 周期滑动减少和快速锁定功能

4.7.1 周期滑动减少(CSR)

CSR通过在频率采集期间降低比较频率,同时保持相同的环路带宽,来减少比较频率与环路带宽的比值,从而避免周期滑动。当比较频率与环路带宽的比值超过约100倍时,周期滑动可能会显著影响锁定时间,此时CSR可以发挥重要作用。在选择CSR因子时,应根据实际情况选择合适的值,以避免过度降低比较频率导致相位噪声变差。

4.7.2 快速锁定(Fastlock)

Fastlock通过在频率采集期间增加环路带宽来缩短锁定时间。在比较频率小于等于2 MHz的情况下,Fastlock可能比CSR提供更好的效果。但Fastlock在解除时会产生一个毛刺,并且在较高比较频率下,毛刺的影响会更加明显。因此,在使用Fastlock时,建议将稳态电荷泵电流设置为4X或更小,并且在使用高阶滤波器时,需要注意第三和第四极点的位置,以确保环路滤波器的优化。

4.8 分数杂散和相位噪声控制

控制分数杂散是一项需要经验和技巧的工作。可以通过以下步骤来优化杂散和相位噪声性能:

- 选择FM:对于Delta - Sigma调制器的阶数,建议先从3阶调制器(FM = 3)开始,并使用强抖动。一般来说,4阶调制器(FM = 0)可以提供较好的主分数杂散抑制,但会产生较差的子分数杂散;2阶调制器(FM = 2)则相反。

- 选择DITH:抖动对主分数杂散的影响较小,但对次分数杂散的影响较大。启用抖动可能会增加相位噪声,因此需要根据具体应用来决定是否启用以及选择何种强度的抖动。

- 调整分数字:使用较大的分数分子通常可以改善分数杂散,但分数分母的增加对杂散的改善有一定的限制,一般建议将分数分母保持在不超过4095的范围内。

五、编程与寄存器配置

5.1 编程接口

LMX2485通过三线高速(20 - MHz)MICROWIRE接口进行编程,数据以MSB优先的方式移入24位移位寄存器。建议最后编程N计数器,因为这会初始化数字锁定检测器和快速锁定电路。

5.2 寄存器映射

寄存器分为基本寄存器和高级寄存器。基本寄存器包含实现PLL锁定所需的关键信息,高级寄存器用于优化杂散、相位噪声和锁定时间性能。在实际应用中,可以根据需要选择使用快速启动寄存器映射或完整寄存器映射。

六、应用与设计要点

6.1 应用信息

LMX2485适用于需要低电流消耗和低分数杂散的应用。对于只需要单个PLL的应用,可以将未使用的PLL断电,以避免额外的电流消耗和杂散干扰。

6.2 典型应用设计

在典型应用中,需要考虑多个设计参数,如相位裕度、环路带宽、极点比率等。环路滤波器的设计是关键,需要平衡锁定时间、杂散和相位噪声的要求。TI网站提供了丰富的参考资料、设计工具和仿真工具,可帮助工程师进行环路滤波器的设计和仿真。

七、电源和布局建议

7.1 电源建议

建议使用低噪声稳压器为电源引脚供电,并对所有电源引脚使用串联18 - Ω电阻和两个并联接地的电容进行滤波,以创建低通滤波器。在选择电容值时,应考虑电容的ESR,以实现最佳的滤波效果。

7.2 布局建议

高频输入引脚的布局至关重要,应尽量缩短走线长度。同时,应确保接地和电源平面与电源引脚的过孔保持20 mils或更远的距离,以防止杂散能量耦合。

八、总结

LMX2485x 3 - GHz Delta - Sigma低功耗双PLLatinum™频率合成器凭借其丰富的特性、广泛的应用领域和良好的性能表现,为电子工程师提供了一个强大的频率合成解决方案。在实际设计中,工程师需要充分理解其功能和特性,合理配置寄存器和设计外部电路,以实现最佳的性能。希望本文能为大家在使用LMX2485x进行设计时提供一些有用的参考和指导。大家在实际应用中遇到过哪些问题呢?欢迎在评论区分享交流。

-

频率合成器

+关注

关注

5文章

368浏览量

33879 -

低功耗

+关注

关注

12文章

4032浏览量

106852

发布评论请先 登录

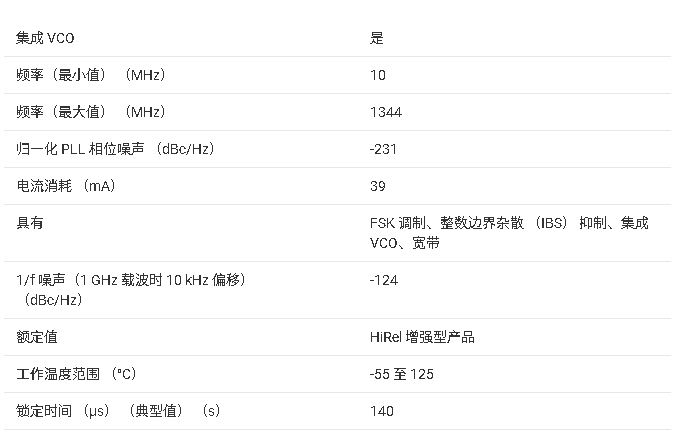

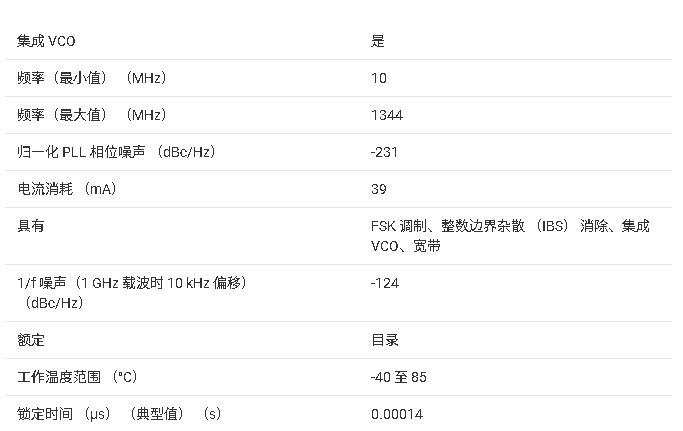

LMX2571-EP 低功耗高性能射频合成器技术文档总结

LMX2571 低功耗高性能射频合成器技术文档总结

LMX2485x 3 - GHz Delta - Sigma低功耗双PLLatinum™频率合成器深度解析

LMX2485x 3 - GHz Delta - Sigma低功耗双PLLatinum™频率合成器深度解析

评论