探索LMH2191:52 MHz时钟树驱动的卓越之选

在电子设计领域,时钟信号的稳定与精确对于设备的性能至关重要。今天,我们就来深入了解一款出色的时钟树驱动芯片——Texas Instruments的LMH2191,看看它如何为我们的设计带来便利与优势。

文件下载:lmh2191.pdf

一、LMH2191概述

LMH2191是一款双通道时钟树驱动芯片,专为移动手机外设(如蓝牙、无线局域网和数字视频广播 - H等)提供通用时钟。它能有效解决扇出驱动能力有限或长走线等时钟问题,保护主时钟免受负载变化和频率牵引影响,隔离噪声模块和串扰。其超低相位噪声特性使其能够驱动像无线局域网和蓝牙这类对时钟信号敏感的模块。

二、芯片特性亮点

2.1 独特的时钟输出设计

- 一路输入两路输出:仅需一个输入时钟,就能产生两个输出时钟,方便为多个外设提供时钟信号。

- 1.8V方波时钟输出:输出标准的1.8V方波时钟,满足大多数外设的时钟需求。

- 反相时钟输出:CLK2输出反相,有助于进一步降低电磁干扰(EMI)。

- 独立时钟请求:每个时钟输出都有独立的时钟请求引脚,允许外设自主控制时钟的启用,实现灵活的时钟管理。

2.2 出色的隔离与低噪声性能

- 高电源噪声隔离:对电源噪声有很高的隔离能力,确保时钟输入不受电源波动的影响。

- 高输出间隔离:时钟输出之间的高隔离度,保证了各外设之间不会相互干扰。

- 集成低噪声LDO:集成了1.8V低压差稳压器(LDO),输出噪声电压低,能够提供10 mA的负载电流,为TCXO或其他时钟源供电。

2.3 其他特性优势

- EMI滤波:具备EMI滤波功能,降低电磁干扰,提高系统的电磁兼容性。

- 超低待机电流:在待机模式下消耗的电流极低,有助于延长电池续航时间。

- 宽电源电压范围:VBAT范围为2.5V至5.5V,适应多种电源供电场景。

- 小巧封装:采用8 - 凸块DSBGA封装,尺寸仅为1.61 mm x 1.063 mm,适合便携式应用。

三、电气性能剖析

3.1 供电与工作条件

- 绝对最大额定值:供电电压(VBAT - VSS)范围为 - 0.3V至6V,不同端口的电压、ESD耐受、输出短路持续时间等都有明确的限制,使用时需严格遵守,防止芯片损坏。

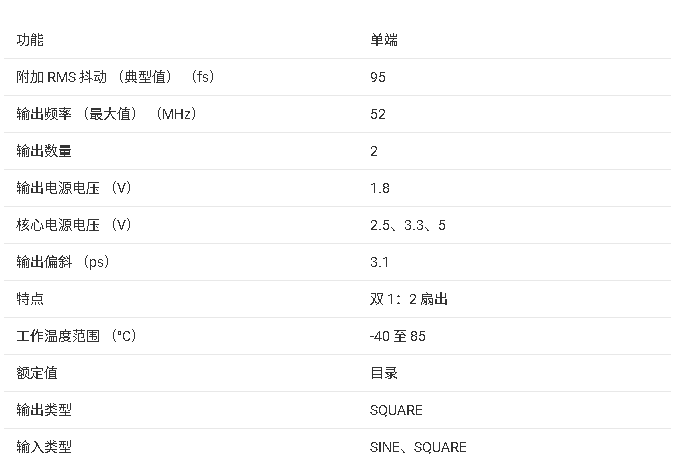

- 工作额定值:供电电压(VBAT - VSS)在2.5V至5.5V之间,输入时钟频率范围为10 MHz至52 MHz,输入时钟占空比为45%至55%,工作温度范围为 - 40°C至 + 85°C。

3.2 关键电气参数

- 供电电流:在不同的输入时钟频率和负载电容下,供电电流会有所变化。例如,当SCLK_IN = 19.2 MHz,两个时钟输出都翻转,负载电容为0pF时,供电电流典型值为1.65 mA;当负载电容为33.5pF时,供电电流典型值为4.45 mA。在关机模式下,输入时钟不活动或翻转时,电流仅为0.1至1 μA。

- 时钟输出参数:包括传播延迟、输出间偏斜、上升时间、下降时间、输出时钟占空比和抖动等。例如,传播延迟(低到高或高到低)在负载电容为33 pF时,典型值为6.1 ns,最大值为10.5 ns;输出间偏斜典型值为1.5 ns,最大值为3.1 ns。

- LDO参数:输出电压在负载电流为1 mA时,典型值为1.8V,范围为1.73V至1.88V;负载电流最大可达10 mA;压差电压在输出电流为10 mA,输出电压为1.7V时,典型值为125 mV。

四、内部结构与工作原理

4.1 时钟树驱动

- 输入部分:源时钟输入(SCLK_IN)通过内部连接的33pF耦合电容进行直流偏置,防止外部直流电压影响内部偏置电路。由于耦合电容的存在,最小时钟频率为10 MHz。该电路能够根据输入信号的边缘调整开关点,使输出时钟的占空比接近50%,满足外设对占空比的要求。输入阻抗由直流输入电阻和交流输入阻抗组成,交流输入阻抗受输入信号幅度影响。

- 输出部分:每个输出能够驱动高达50 pF的容性负载,同时将电磁干扰降至最低。CLK2输出反相进一步减少了EMI。

4.2 时钟请求逻辑

每个时钟输出都有独立的时钟请求输入,允许外设控制时钟的启用。时钟请求信号连接到锁存器的D输入,同步控制时钟输出驱动器的开关,防止时钟输出出现毛刺。当两个请求输入都为低电平时,LDO输出电压将被禁用。

4.3 低压差稳压器(LDO)

LDO用于调节输入电压VBAT,为TCXO和内部时钟路径提供稳定的1.8V超低噪声电源。它能够抑制电源电压纹波和噪声,减少时钟信号的相位噪声。LDO在时钟请求激活时上电,支持过热检测,过热时会自动关闭。推荐的上电顺序是在电源已上电的情况下将时钟请求拉高,使LDO在需要输出时钟时才上电,降低功耗。

五、应用与布局建议

5.1 典型应用

LMH2191常用于为移动手机外设提供时钟,如蓝牙、无线局域网和数字视频广播 - H等。其高隔离度和低相位噪声特性确保了各外设之间不会相互干扰,时钟质量不受影响。

5.2 布局建议

- 布线:SCLK_IN输入走线和CLK1、CLK2输出走线应尽可能短,以减少时钟输出的额外容性负载。

- 去耦:在器件附近进行适当的去耦,推荐使用低ESR的表面贴装陶瓷电容(MLCC),如CBAT为1 μF,COUT为2.2 μF。

六、总结

LMH2191以其丰富的特性、出色的电气性能和小巧的封装,成为移动设备和便携式设备时钟设计的理想选择。它不仅能够解决时钟驱动和隔离问题,还能有效降低功耗和电磁干扰。在实际应用中,我们需要根据具体需求合理选择工作条件和参数,同时注意布局布线,以充分发挥其性能优势。大家在使用LMH2191的过程中,有没有遇到过什么有趣的问题或者独特的应用场景呢?欢迎在评论区分享交流。

-

移动设备

+关注

关注

0文章

531浏览量

56043

发布评论请先 登录

探索LMH2191:52 MHz时钟树驱动的卓越之选

探索LMH2191:52 MHz时钟树驱动的卓越之选

评论