LMK04906:超低噪声时钟抖动清理器与乘法器的深度剖析

在电子设计领域,时钟抖动清理器与乘法器对于确保系统时钟信号的稳定性和准确性至关重要。今天,我们就来深入探讨德州仪器(TI)的LMK04906,一款具备超低噪声性能的时钟抖动清理器与乘法器。

文件下载:lmk04906.pdf

一、产品特性亮点

超低RMS抖动性能

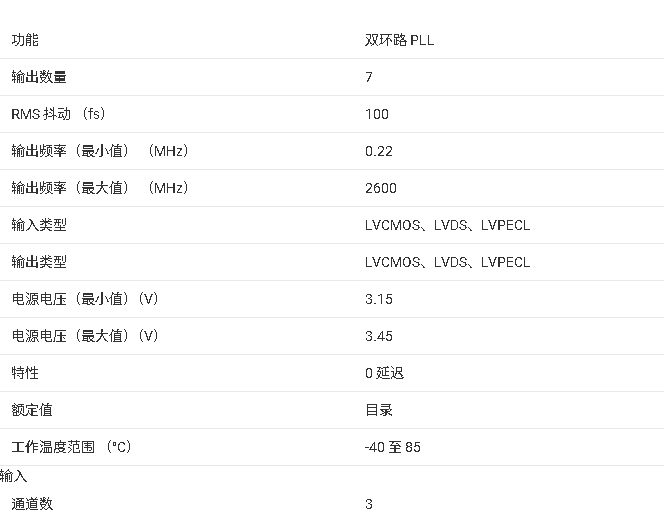

LMK04906在抖动性能方面表现卓越,其100 - fs RMS抖动(12 kHz至20 MHz)和123 - fs RMS抖动(100 Hz至20 MHz)的指标,能有效满足对时钟信号质量要求极高的应用场景,如高速数据传输和高精度测量等。

双环PLLatinum™PLL架构

该架构是LMK04906的核心优势之一。PLL1集成了低噪声晶体振荡器电路,在输入时钟丢失时具备保持模式,可实现自动或手动触发/恢复。PLL2则拥有归一化[1 Hz]PLL噪声底至 - 227 dBc/Hz的出色表现,相位检测器速率高达155 MHz,还配备了OSCin频率倍增器和集成低噪声VCO,为系统提供了稳定且低噪声的时钟信号。

冗余输入时钟与灵活输出配置

它具备3个带LOS的冗余输入时钟,支持自动和手动切换模式,增强了系统的可靠性。输出方面,提供50%占空比输出分频,范围从1到1045(偶数和奇数),且支持LVPECL、LVDS或LVCMOS可编程输出,满足不同应用的多样化需求。此外,还具备精密数字延迟,可固定或动态调整,以及25 - ps步长的模拟延迟控制,为时钟信号的相位调整提供了精细的手段。

二、广泛的应用领域

LMK04906的应用范围十分广泛,涵盖了10G、40G和100G OTN线卡、SONET/SDH OC - 48/STM - 16和OC - 192/STM64线卡、GbE/10GbE、1/2/4/8/10GFC线卡等通信领域,以及同步以太网光模块、DSLAM/MSANs测试与测量、广播视频、无线基站、数据转换器时钟等多个领域,展现了其强大的通用性和适应性。

三、详细的技术规格分析

绝对最大额定值与ESD额定值

在绝对最大额定值方面,电源电压(VCC)范围为 - 0.3至3.6 V,输入电压(VIN)为 - 0.3至(VCC + 0.3)V等,这些参数为设计人员在电路设计时提供了安全边界。ESD额定值方面,人体模型(HBM)为±2000 V,带电设备模型(CDM)为±750 V,机器模型(MM)为±150 V,表明该器件具备一定的静电防护能力,但在实际使用中仍需注意静电防护措施。

推荐工作条件与电气特性

推荐工作条件规定了器件正常工作的环境范围,如结温(TJ)最大为125°C,环境温度(TA)在VCC = 3.3 V时为 - 40至85°C等。电气特性部分详细列出了各项参数,如电流消耗、时钟输入频率、输入摆率、差分输入电压等,这些参数对于准确设计电路和评估系统性能至关重要。例如,在电流消耗方面,所有时钟启用时的电源电流(ICC_CLKS)典型值为410 mA,最大为470 mA,设计人员可据此进行电源设计和功耗评估。

四、系统架构与工作模式

双环PLL架构优势

双环PLL架构使得LMK04906在输出频率范围和相位噪声积分带宽方面都能实现最低抖动性能。PLL1通过外部参考时钟驱动,使用外部VCXO或可调晶体为PLL2提供频率准确、低相位噪声的参考时钟,同时抑制参考时钟可能积累的高频相位噪声。PLL2则利用内部VCO的优越高频相位噪声特性和参考VCXO或可调晶体的良好低频相位噪声,实现超低抖动的输出。

多种工作模式

LMK04906支持双PLL、单PLL和时钟分配等多种模式。在双PLL模式下,PLL1和PLL2协同工作,为系统提供高精度的时钟信号;单PLL模式下,PLL1断电,OSCin作为PLL2的参考输入;时钟分配模式则允许使用CLKin1将时钟信号分配到输出端。此外,还具备0 - 延迟模式,可确保时钟输入和输出之间的固定相位关系,满足特定应用对相位准确性的要求。

五、编程与配置要点

寄存器编程

该器件使用32位寄存器进行编程,每个寄存器由5位地址字段和27位数据字段组成。编程时需注意按顺序进行,如从R0到R16,以及R24到R31,以确保器件正常工作。例如,在编程R0时,需将复位位(b17)设置为1以确保器件处于默认状态,后续编程时再将其清除。

特殊编程情况

在编程R0至R5以更改CLKoutX_DIV或CLKoutX_DDLY值时,若CLKoutX_DIV > 25或CLKoutX_DDLY > 12,可能需要额外的CLKuWire时钟周期。如SYNC_EN_AUTO = 1时,还需特殊的编程方法,这些细节在实际编程中需要特别关注,以避免出现错误。

六、应用与实现建议

环路滤波器设计

每个PLL都需要专用的环路滤波器。PLL1的环路滤波器应连接到CPout1引脚,推荐设计为总闭环带宽在10 Hz至200 Hz范围内,以保留参考时钟输入信号的频率准确性并抑制高频相位噪声。PLL2的电荷泵直接连接到可选的内部环路滤波器组件,设计时需考虑VCO的Kvco值变化对环路带宽的影响,确保环路在整个VCO调谐频率范围内稳定工作。

时钟输入与输出驱动

在驱动CLKin和OSCin输入时,需根据信号源的类型(差分或单端)选择合适的耦合方式和终止方法,以确保信号的质量和稳定性。对于时钟输出,要遵循传输线理论进行阻抗匹配,为不同类型的驱动(如LVDS和LVPECL)提供合适的负载和直流偏置,以实现最佳的相位噪声和抖动性能。

频率规划

计算LMK04906的输出分频值相对简单,可通过计算时钟输出频率的最小公倍数(LCM),确定支持目标频率的VCO范围,进而计算出时钟输出分频值。一般建议绕过VCO分频器,以简化设计并提高性能。

七、总结

LMK04906凭借其超低噪声性能、灵活的架构和丰富的功能,为电子工程师在时钟信号处理方面提供了强大的解决方案。在实际应用中,我们需要深入理解其技术规格、系统架构和编程要点,结合具体的应用需求进行合理的设计和配置,以充分发挥其优势,确保系统的稳定性和可靠性。同时,在设计过程中要注意各个环节的细节,如环路滤波器设计、时钟输入输出驱动和频率规划等,以实现最佳的系统性能。你在使用LMK04906或类似器件时遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

LMK04906

+关注

关注

0文章

4浏览量

6559

发布评论请先 登录

LMK04906 具有 6 个可编程输出的超低噪声时钟抖动消除器/乘法器

LMK04906带6路可编程输出的,超低噪声时钟抖动清除器和乘法器数据表

LMK04906:超低噪声时钟抖动清理器与乘法器的深度剖析

LMK04906:超低噪声时钟抖动清理器与乘法器的深度剖析

评论