电子工程师必看:CDCDB800时钟缓冲器深度解读

在电子设计领域,时钟缓冲器对于确保信号的稳定传输和分配起着至关重要的作用。今天,我们就来深入探讨一下德州仪器(Texas Instruments)的CDCDB800,一款专为PCIe Gen 1至Gen 7设计的8输出时钟缓冲器。

文件下载:cdcdb800.pdf

一、CDCDB800的核心亮点

1. 输出性能卓越

CDCDB800拥有8个LP - HCSL输出,可通过编程设置集成85Ω(默认)或100Ω差分输出端接,能很好地适应不同的阻抗需求。输出到输出的偏斜小于50 ps,输入到输出延迟小于3 ns,确保了信号的高精度传输。

2. 低抖动表现

在不同的滤波器条件下,它都展现出了极低的附加相位抖动。例如,经过PCIE Gen 7滤波器后,附加相位抖动最大为11.3 fs RMS,这种低抖动特性对于高速数据传输系统来说至关重要。

3. 架构兼容性强

支持Common Clock(CC)和Individual Reference(IR)架构,并且与扩频兼容,为不同的系统设计提供了更多的灵活性。

4. 功能丰富实用

具备8个硬件输出使能(OE#)控制,可独立控制每个输出通道;拥有故障安全输入功能,能在电源未施加时保护设备;还提供可编程输出摆率控制,可根据电路板设计调整输出信号的摆率。

5. 低功耗设计

采用3.3V核心和IO电源电压,硬件控制的低功耗模式(PD#)可有效降低功耗,最大电流消耗仅为72 mA。

6. 封装小巧

采用6mm × 6mm、48引脚的VQFN封装,节省了电路板空间,适合在紧凑的设计中使用。

二、应用场景广泛

CDCDB800的应用场景十分广泛,涵盖了多个领域:

- 服务器领域:包括微服务器、塔式服务器和机架服务器等,为服务器内部的PCIe接口提供稳定的时钟信号。

- 存储网络:如存储区域网络(SAN)、网络附属存储(NAS)以及主机总线适配卡(HBA)等,确保数据存储和传输的准确性。

- 硬件加速:为硬件加速器提供精确的时钟,提升其处理性能。

三、技术规格详解

1. 绝对最大额定值

在使用过程中,需要注意其绝对最大额定值,如电源电压范围为 - 0.3V至3.6V,结温最高为125°C等,超出这些范围可能会导致设备永久性损坏。

2. ESD额定值

该器件具有良好的静电放电(ESD)保护能力,人体模型(HBM)下所有引脚的ESD额定值为±3500V,带电设备模型(CDM)下为±1000V。

3. 推荐工作条件

推荐的IO和核心电源电压为3V至3.6V,输入电源电压同样为3V至3.6V,环境温度范围为 - 40°C至105°C。

4. 电气特性

在电气特性方面,它的输入频率范围为50 MHz至250 MHz,输出频率与之相同。不同工作模式下的电流消耗也有所不同,例如在所有输出禁用时,电源电流最大为18 mA。

四、功能模块剖析

1. 故障安全输入

CDCDB800支持故障安全输入操作,允许在电源未施加时驱动设备输入而不损坏设备,这为系统的上电和断电过程提供了额外的保护。

2. 输出使能控制

通过SMBus和OE#引脚可以控制输出通道的状态。每个OE#引脚对应一个输出通道,当相应的OE#引脚为低电平时,SMBus寄存器可以进一步控制该通道的启用或禁用。

3. SMBus接口

当CKPWRGD_PD# = 1时,SMBus接口处于激活状态,可用于单独启用或禁用每个输出。当CKPWRGD_PD# = 0时,SMBus引脚处于高阻状态,但所有寄存器设置会被保留。

五、注册映射与编程

1. 寄存器介绍

CDCDB800包含多个寄存器,如RCR1、OECR1、OECR2等。这些寄存器用于控制输出使能、设置输出阻抗、调整输出摆率等功能。例如,OECR1和OECR2寄存器可用于控制各个输出时钟通道的启用或禁用。

2. 编程方式

使用SMBus对八个输出驱动器的状态进行编程。通过特定的协议,如字节写入、字节读取、块写入和块读取协议,可以实现对寄存器的读写操作。

六、实际应用设计

1. 典型应用案例

在一个典型的服务器主板应用中,时钟发生器提供100MHz的参考时钟给CDCDB800,然后它将这个时钟分配给多个PCIe端点,如处理器、转接卡/重定时器和DDR内存控制器等。

2. 设计要点

- 输出使能控制方法:可以选择使用SMBus编程寄存器(软件控制)或硬件OE#引脚来控制输出。如果使用软件控制,硬件OE#引脚可以浮空;如果使用硬件控制,可将这些引脚连接到GPIO控制器。

- 电源供应:高性能时钟缓冲器对电源噪声非常敏感,因此需要使用滤波电容和旁路电容来降低电源噪声。同时,建议在板级电源和芯片电源之间插入铁氧体磁珠,以隔离高频开关噪声。

- 布局设计:所有连接到CKx引脚的传输线应根据输出阻抗设置相应的差分阻抗,以避免反射和辐射发射增加。在PCB布局时,要注意消除或减少传输线上的短截线,并确保良好的热性能和电源连接。

七、设备与文档支持

1. 设备支持工具

TICS Pro是一个离线软件工具,可用于EVM编程和寄存器映射生成,方便为特定应用配置设备。

2. 文档支持与更新

相关文档包括Texas Instruments, CDCDB800/803 Ultra - Low Additive Jitter, 8 - Output PCIe Gen1 to Gen5 Clock Buffer。用户可以在ti.com上注册接收文档更新通知。

3. 技术支持论坛

TI E2E™支持论坛是获取快速、可靠答案和设计帮助的好去处,工程师们可以在这里与专家交流经验。

总之,CDCDB800以其出色的性能、丰富的功能和广泛的应用场景,为电子工程师在PCIe时钟分配设计中提供了一个优秀的选择。在实际应用中,我们需要充分了解其技术规格和设计要点,以确保系统的稳定运行。大家在使用CDCDB800的过程中,有没有遇到过什么有趣的问题或挑战呢?欢迎在评论区分享交流。

-

电子设计

+关注

关注

42文章

2870浏览量

49916

发布评论请先 登录

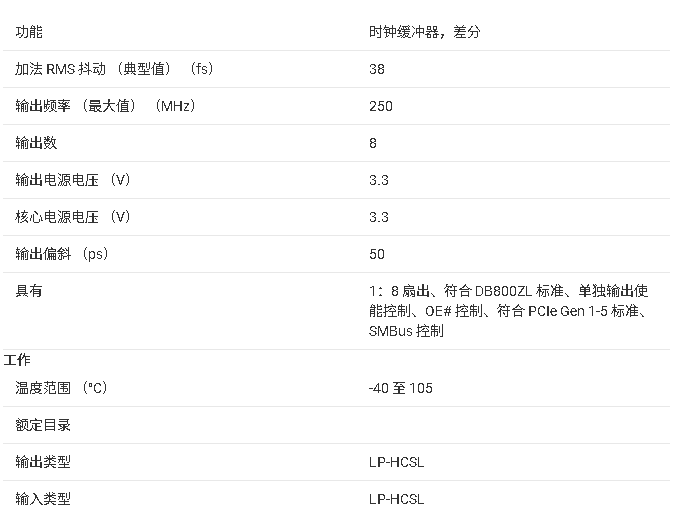

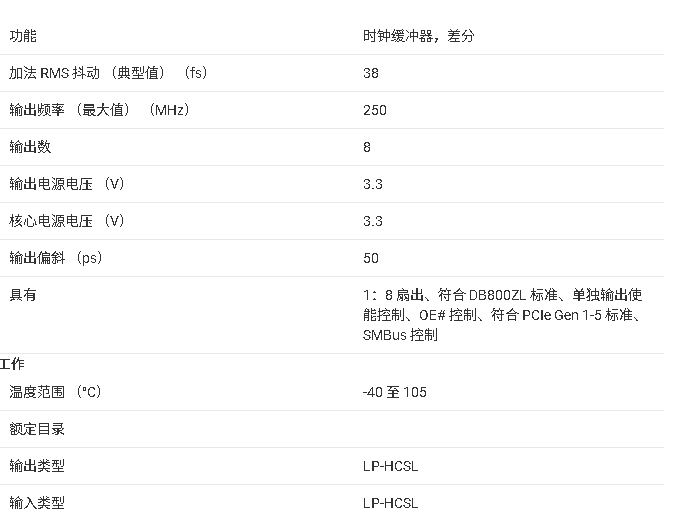

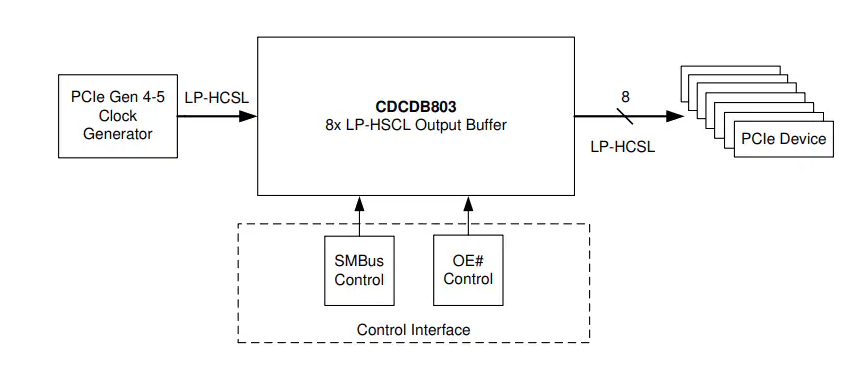

CDCDB803适用于第1代到第6代PCIe、符合DB800ZL标准的8输出时钟缓冲器数据表

CDCDB800适用于第1代到第6代PCIe、符合DB800ZL标准的8输出时钟缓冲器数据表

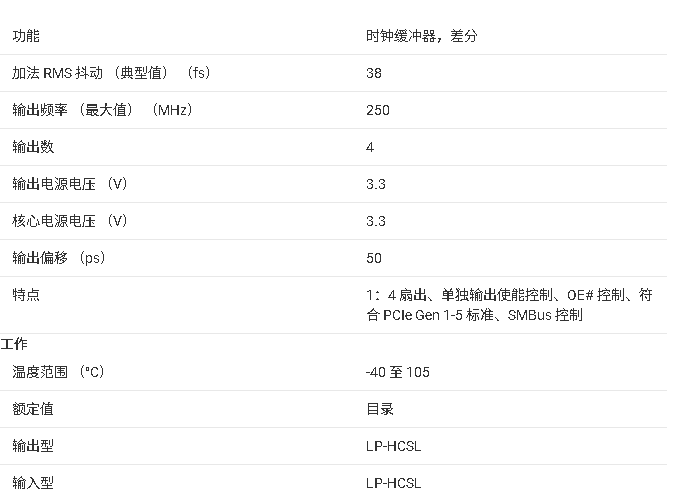

CDCDB400适用于第1代到第6代PCIe、符合DB800ZL标准的4输出时钟缓冲器数据表

CDCDB800/803超低附加抖动、8路输出PCIe Gen1至Gen5时钟缓冲器

CDCDB400 4输出时钟缓冲器技术文档总结

CDCDB803 8输出时钟缓冲器技术文档总结

CDCDB800 8输出时钟缓冲器技术文档总结

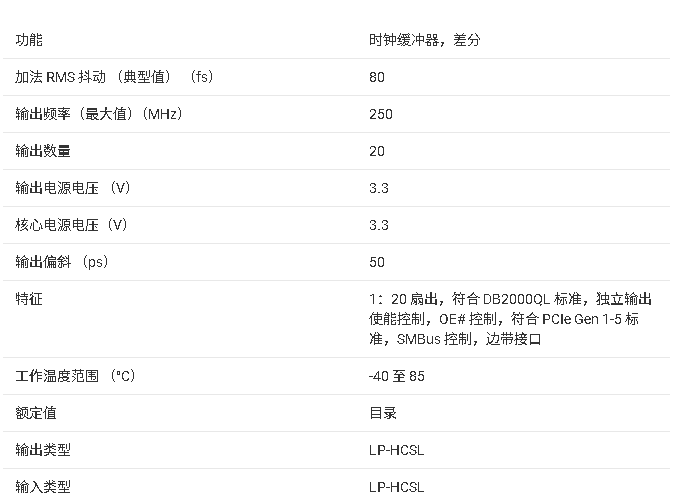

CDCDB2000 20输出时钟缓冲器技术文档总结

PCIe Gen7时钟缓冲技术解析:TI CDCDB400芯片深度剖析

Texas Instruments CDCDB803用于PCIe®第1代至第5代的8输出时钟缓冲器数据手册

电子工程师必看:CDCDB800时钟缓冲器深度解读

电子工程师必看:CDCDB800时钟缓冲器深度解读

评论