电子工程师的宝藏:CDCLVD2108时钟缓冲器全面解析

在电子设备的设计中,时钟信号的稳定传输可是个关键因素,它直接影响着设备的性能和可靠性。今天我就来深入剖析一款超厉害的时钟缓冲器——CDCLVD2108,这可是德州仪器精心打造的产品。咱们一起看看它到底有啥过人之处,以及在实际应用中该怎么发挥它的优势。

文件下载:cdclvd2108.pdf

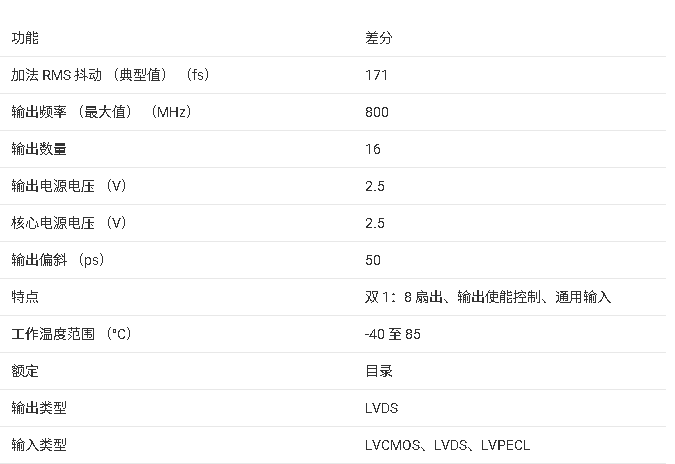

产品概述

CDCLVD2108是一款双1:8低附加抖动LVDS缓冲器。它能把两个时钟输入(IN0、IN1)精准地分配到总共16对差分LVDS时钟输出(OUT0 - OUT15)。每个缓冲器模块都有一个输入和8个LVDS输出,而且输入信号可以是LVDS、LVPECL或者LVCMOS,兼容性超棒。特别值得一提的是,它专门为驱动50 - Ω传输线设计,能保证信号在传输过程中的稳定和准确。

核心特性

低抖动性能

在10 kHz到20 MHz的频率范围内,它的附加抖动小于300 fs RMS,这个抖动水平非常低。低抖动对于高精度的时钟信号传输至关重要,能有效减少信号失真,确保设备的精确运行。大家想想,如果时钟信号抖动过大,就好比跑步时步伐乱了,设备的性能肯定会大打折扣。

输出偏差小

在同一个缓冲器组内,输出偏差最大只有50 ps。这意味着各个输出信号之间的时间差很小,能保证多个时钟信号同步性好。在一些对同步要求极高的系统中,比如数据中心的服务器集群,各个服务器的时钟同步就需要这种低偏差的缓冲器来保证数据传输的准确性和一致性。

输入兼容性强

它的输入端口能够接收LVDS、LVPECL和LVCMOS三种不同类型的信号。这大大增加了它的通用性,工程师在设计电路时可以根据实际情况选择合适的信号源,而不用再为信号匹配问题头疼。

高频率支持

时钟频率最高能达到800 MHz,能满足高速数据传输和处理的需求。在现代高速通信、数据处理等领域,对时钟频率的要求越来越高,CDCLVD2108的高频率支持能力让它在这些应用场景中表现出色。

引脚功能详解

电源和接地引脚

VCC引脚(6、7、13、24、37、48)为设备提供2.5V的电源,GND引脚(1、12)是设备的接地端。电源的稳定供应是设备正常工作的基础,在设计电路板时,要注意电源的滤波和接地的可靠性,避免电源噪声对设备性能产生影响。

输入引脚

INP0和INN0(10、9)是缓冲器0的差分输入对或单端输入引脚,INP1和INN1(3、4)是缓冲器1的差分输入对或单端输入引脚。这些输入引脚可以灵活地连接不同类型的时钟信号源,为设计带来了更多的可能性。

输出引脚

从OUTP0、OUTN0到OUTP15、OUTN15,一共有16对差分LVDS输出引脚。每个输出引脚对都对应着一个特定的输入,能将输入的时钟信号准确地输出。在实际应用中,要根据输出信号的负载情况合理设计输出电路,确保信号的质量。

控制引脚

EN引脚(2)是一个带有内部200kΩ上拉和下拉电阻的输入引脚,用于控制输出的开启和关闭。通过设置EN引脚的逻辑电平,可以方便地控制输出信号的状态。大家不妨思考一下,这种灵活的输出控制功能在哪些具体的应用场景中会发挥重要作用呢?

参考电压输出引脚

VAC_REF0(8)和VAC_REF1(5)是为电容耦合输入提供偏置电压的输出引脚。使用时,建议在这些引脚上连接一个0.1µF的电容到地,以保证参考电压的稳定。这对于一些采用电容耦合方式输入的电路来说非常重要。

电气特性剖析

输入特性

不同类型的输入信号有着各自的特性要求。比如,对于2.5V LVCMOS输入,输入频率最高为200 MHz,输入阈值电压在1.1 - 1.5V之间。而对于差分输入,输入频率最高能达到800 MHz,差分输入电压峰 - 峰值在0.3 - 1.6V之间。了解这些输入特性,能帮助我们正确地选择输入信号源和设计输入电路。

输出特性

LVDS输出特性也很关键。差分输出电压幅度在250 - 450 mV之间,输出过冲和下冲不超过输出幅度的10%。这些特性保证了输出信号的质量和稳定性,能满足大多数应用场景的需求。同时,输出的传播延迟、输出偏差等参数也都有明确的指标,在设计时要根据这些参数合理规划信号的传输路径。

电源特性

静态电源电流在27 - 45 mA之间,当所有输出都开启,负载为100Ω,频率为100 MHz时,电源电流在119 - 158 mA之间;频率为800 MHz时,电源电流在168 - 211 mA之间。了解电源特性有助于我们合理设计电源电路,确保设备在不同工作状态下都能稳定运行。

应用信息

热管理

为了保证设备的可靠性和性能,芯片的温度最高不能超过125°C。该设备的封装有一个暴露的焊盘,这是主要的散热通道。在设计PCB时,要在封装的占位区内设计包含多个过孔到接地平面的散热焊盘图案,并将散热焊盘焊接好,以确保良好的散热效果。大家可以想想,如果散热设计不好,会对设备的性能产生哪些具体的影响呢?

电源滤波

高性能的时钟缓冲器对电源噪声非常敏感,电源噪声会显著增加缓冲器的附加抖动。因此,必须采取措施降低系统电源的噪声。可以使用滤波电容消除低频噪声,旁路电容为高频噪声提供低阻抗路径。旁路电容要尽量靠近电源引脚布局,并且布线环路要短,以减少电感。同时,还可以在板级电源和芯片电源之间插入铁氧体磁珠,隔离时钟驱动器产生的高频开关噪声。

输出端接

对于LVDS输出,在接收器端的两个50Ω线路之间使用100Ω的端接电阻能保证信号的完整性。可以选择直流耦合端接或交流耦合端接方式,端接电阻要尽量靠近接收器放置。如果接收器的内部偏置电压与CDCLVD2108的输出共模电压不同,就应该使用交流耦合方式。如果LVDS接收器有内部100Ω端接电阻,就不需要再使用外部端接电阻了。

输入端接

CDCLVD2108的输入可以与LVDS、LVPECL或LVCMOS驱动器连接。不同类型的驱动器连接方式有所不同,比如LVDS驱动器可以采用直流或交流耦合方式连接,LVPECL输入需要使用串联电阻来降低信号摆幅,LVCMOS时钟输入需要根据情况合理设置串联电阻。在使用时,要根据实际的驱动器类型选择合适的连接方式。

CDCLVD2108凭借其出色的性能和丰富的功能,在电信、医疗成像、测试测量设备、无线通信等众多领域都能大显身手。作为电子工程师,深入了解它的特点和应用方法,能让我们在设计电路时更加得心应手。大家在实际应用中如果遇到问题,欢迎一起交流探讨!

-

时钟缓冲器

+关注

关注

2文章

273浏览量

51954

发布评论请先 登录

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析

CDCLVP2108 16路LVPECL输出高性能时钟缓冲器数据表

CDCLVD2108双通道1:8低附加抖动LVDS缓冲器数据表

CDCLVD2108 双路1:8低附加抖动LVDS缓冲器技术文档摘要

电子工程师的宝藏:CDCLVD2108时钟缓冲器全面解析

电子工程师的宝藏:CDCLVD2108时钟缓冲器全面解析

评论