该CDCDB400是一款符合 DB800ZL 标准的 4 输出 LP-HCSL 时钟缓冲器,能够为 CC、SRNS 或 SRIS 架构中的 PCIe Gen 1-7、QuickPath 互连 (QPI)、UPI、SAS 和 SATA 接口分配参考时钟。SMBus 接口和四个输出使能引脚允许单独配置和控制所有四个输出。该CDCDB400是一种DB800ZL导数缓冲器,符合或超过DB800ZL规范中的系统参数。该器件还满足或超过DB2000Q规范中的参数。该CDCDB400采用 5mm × 5mm 32 引脚 VQFN 封装。

*附件:cdcdb400.pdf

特性

- 4 个 LP-HCSL 输出,具有可编程集成 85Ω(默认)或 100Ω 差分输出端接

- 4 个硬件输出使能 (OE#) 控件

- PCIE Gen 7滤波器后的附加相位抖动:11.3fs,RMS(最大值)

- PCIE Gen 6滤波器后的附加相位抖动:16.1fs,RMS(最大值)

- PCIE Gen 5滤波器后的附加相位抖动:25fs,RMS(最大值)

- DB2000Q滤波器后的附加相位抖动:38fs,RMS(最大值)

- 支持通用时钟 (CC) 和单独基准 (IR) 架构

- 扩频兼容

- 输出到输出偏斜:< 50ps

- 输入到输出延迟:< 3ns

- 故障安全输入

- 可编程输出压摆率控制

- 3 个可选的 SMBus 地址

- 3.3V 内核和 IO 电源电压

- 硬件控制的低功耗模式 (PD#)

- 电流消耗:最大 46mA

- 5mm × 5mm、32引脚VQFN封装

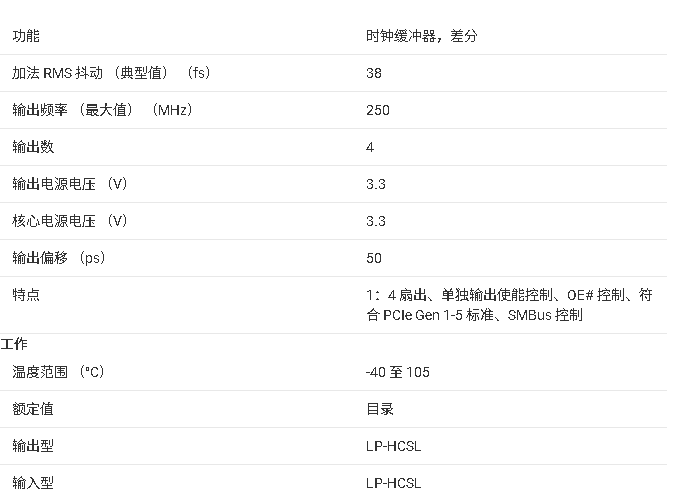

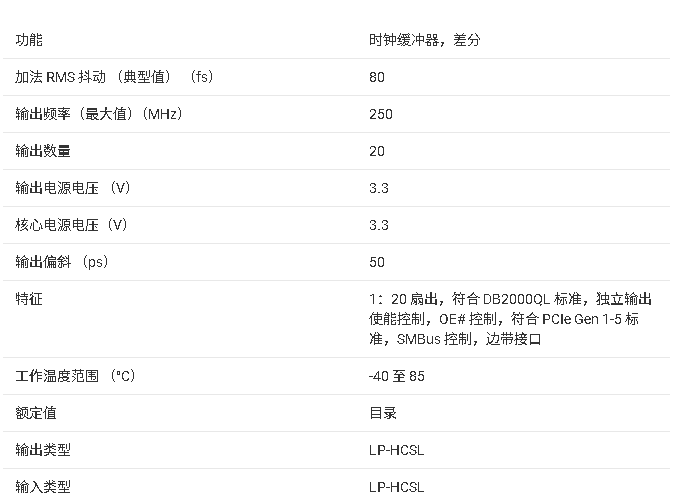

参数

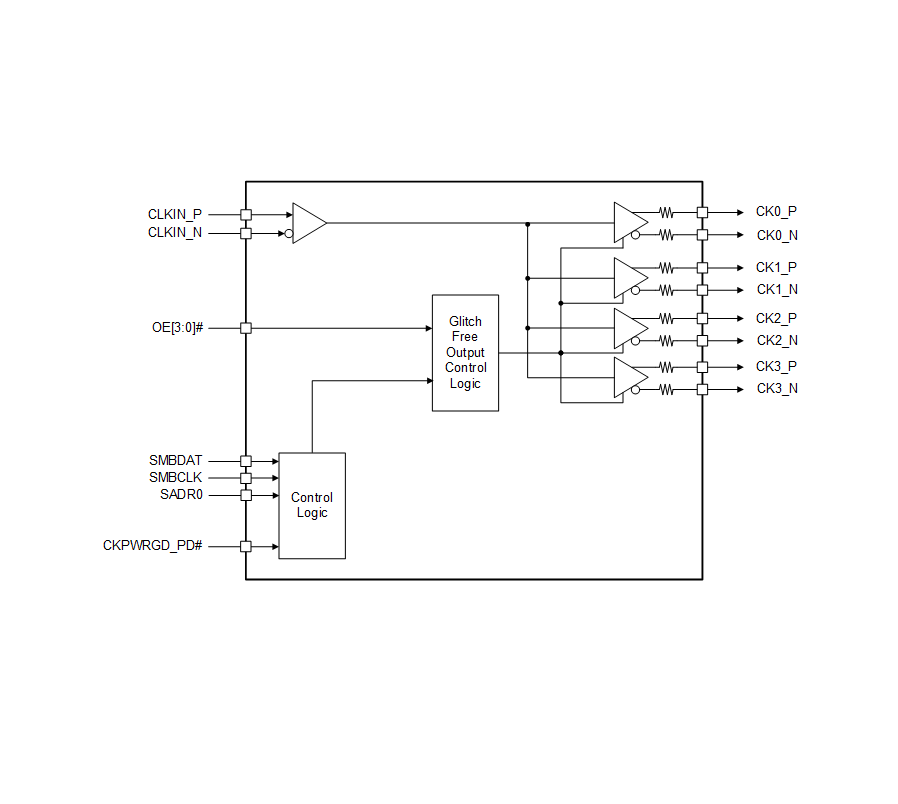

方框图

1. 产品概述

CDCDB400是一款符合DB800ZL规范的4输出LP-HCSL时钟缓冲器,专为PCIe Gen 1至Gen 7、QPI、UPI、SAS和SATA接口设计。其核心特性包括:

- 输出配置:4路LP-HCSL输出,支持可编程集成85Ω(默认)或100Ω差分终端阻抗。

- 低抖动性能:

- PCIe Gen 7滤波后加性相位抖动:11.3fs(最大值,RMS)

- PCIe Gen 6滤波后加性相位抖动:16.1fs(最大值,RMS)

- 支持CC(公共时钟)和IR(独立参考)架构,兼容扩频时钟。

- 控制接口:通过SMBus和4个硬件输出使能(OE#)引脚实现独立通道控制。

- 封装:5mm × 5mm 32引脚VQFN封装。

2. 关键特性

- 电气性能:

- 输入频率范围:50–250MHz

- 输出至输出偏移:<50ps

- 输入至输出延迟:<3ns

- 3.3V核心和I/O供电电压,最大功耗46mA。

- 应用场景:

3. 功能描述

- 输出控制:通过OE#引脚或SMBus寄存器独立启用/禁用各输出通道。

- SMBus编程:支持3个可选的SMBus地址,配置输出阻抗(85Ω/100Ω)及输出摆率控制。

- 失效保护输入:支持输入信号在供电前驱动,避免器件损坏。

4. 寄存器与编程

- 核心寄存器:

- OECR1/OECR2:控制输出通道使能状态。

- OUTSET:全局设置输出阻抗(85Ω/100Ω)和断电状态。

- CAPTRIM:调节输出摆率,适应不同布线长度需求。

- SMBus协议:兼容SMBus 2.0,支持字节/块读写操作。

5. 应用设计建议

6. 文档支持

- 提供TICS Pro工具用于寄存器配置生成,参考设计文档包括《CDCDB800/803时钟缓冲器应用指南》。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

接口

+关注

关注

33文章

9591浏览量

157598 -

时钟缓冲器

+关注

关注

2文章

273浏览量

51954 -

封装

+关注

关注

128文章

9321浏览量

149028 -

PCIe

+关注

关注

16文章

1474浏览量

88898

发布评论请先 登录

相关推荐

热点推荐

CDCDB400 HCSL时钟作为输入是否支持?缓冲器的输出是否支持HCSL的设备?

我正在使用CDCDB400作为PCIE时钟扩展,但是我的输入时钟信号是HCSL,默认要连接的设备也是HCSL的,在这种情况下应该怎样设计电路?

发表于 11-11 07:29

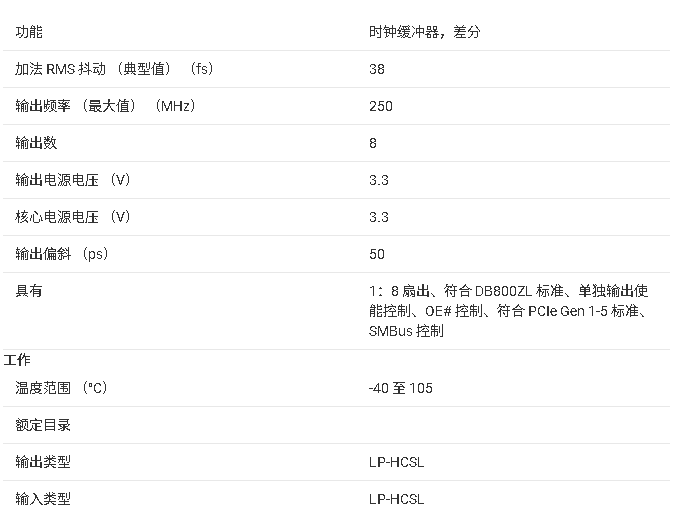

CDCDB800适用于第1代到第6代PCIe、符合DB800ZL标准的8输出时钟缓冲器数据表

电子发烧友网站提供《CDCDB800适用于第1代到第6代PCIe、符合DB800ZL标准的8输出时钟缓冲器数据表.pdf》资料免费下载

发表于 08-20 09:40

•0次下载

CDCDB400适用于第1代到第6代PCIe、符合DB800ZL标准的4输出时钟缓冲器数据表

电子发烧友网站提供《CDCDB400适用于第1代到第6代PCIe、符合DB800ZL标准的4输出时钟缓冲器数据表.pdf》资料免费下载

发表于 08-20 09:42

•0次下载

CDCDB800/803超低附加抖动、8路输出PCIe Gen1至Gen5时钟缓冲器

电子发烧友网站提供《CDCDB800/803超低附加抖动、8路输出PCIe Gen1至Gen5时钟缓冲器.pdf》资料免费下载

发表于 11-26 14:36

•0次下载

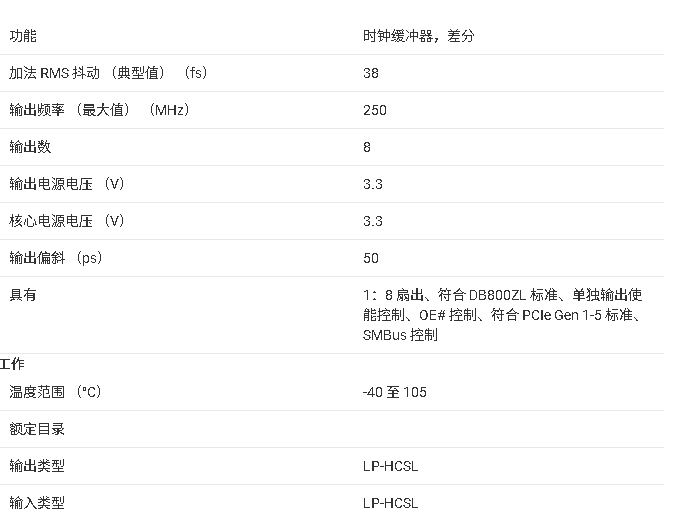

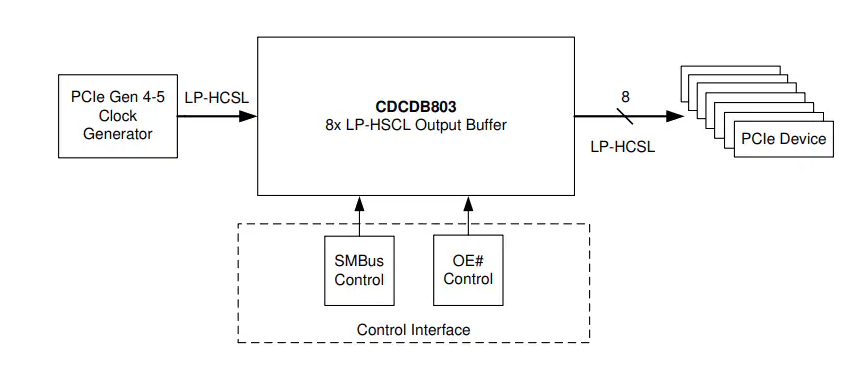

CDCDB803 8输出时钟缓冲器技术文档总结

该CDCDB803是一款符合DB800ZL标准的 8 输出 LP-HCSL 时钟缓冲器,能够为 PCIe Gen 1-6、QuickPath 互连 (QPI)、UPI、SAS 和 SA

CDCDB800 8输出时钟缓冲器技术文档总结

该CDCDB800是一款符合 DB800ZL 标准的 8 输出 LP-HCSL 时钟缓冲器,能够为 PCIe Gen 1-7、QuickPath 互连 (QPI)、UPI、SAS 和

CDCDB2000 20输出时钟缓冲器技术文档总结

该CDCDB2000是一款 20 输出 LP-HCSL,符合 DB2000QL 标准,时钟缓冲器,能够为 PCIe Gen 1-7、QuickPath 互连 (QPI)、UPI、SAS

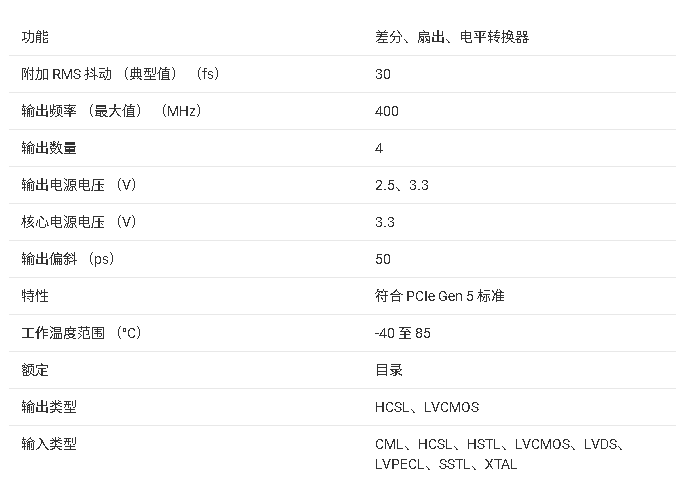

LMK00334四输出时钟缓冲器与电平转换器技术文档总结

LMK00334器件是一款4输出HCSL扇出缓冲器,用于高频、低抖动时钟、数据分配和电平转换。该器件能够为 ADC、DAC、多千兆以太网、XAUI、光纤通道、SATA/SAS、SONE

Texas Instruments CDCDB803用于PCIe®第1代至第5代的8输出时钟缓冲器数据手册

Texas Instruments用于PCIe^®^ Gen 1至Gen 5的CDCDB803 8输出时钟缓冲器是符合DB800ZL标准的时钟

德州仪器CDCDB400:PCIe时钟缓冲器的理想之选

德州仪器CDCDB400:PCIe时钟缓冲器的理想之选 在电子设计领域,时钟缓冲器对于确保系统时钟

探索CDCDB803:PCIe时钟缓冲的理想之选

专为PCIe Gen 1至Gen 6设计的8输出时钟缓冲器。 文件下载: cdcdb803.pdf 一、CDCDB803 核心特性 1.1

电子工程师必看:CDCDB800时钟缓冲器深度解读

)的CDCDB800,一款专为PCIe Gen 1至Gen 7设计的8输出时钟缓冲器。 文件下载: cdcdb800.pdf 一、

CDCDB2000:PCIe时钟缓冲器的卓越之选

CDCDB2000:PCIe时钟缓冲器的卓越之选 在当今高速发展的电子领域,PCIe技术不断演进,对时钟

CDCDB400 4输出时钟缓冲器技术文档总结

CDCDB400 4输出时钟缓冲器技术文档总结

评论