【博主简介】本人“爱在七夕时”,系一名半导体行业质量管理从业者,旨在业余时间不定期的分享半导体行业中的:产品质量、失效分析、可靠性分析和产品基础应用等相关知识。常言:真知不问出处,所分享的内容如有雷同或是不当之处,还请大家海涵。当前在各网络平台上均以此昵称为ID跟大家一起交流学习!

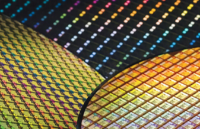

晶圆背面金属化工艺(以下简称“背金工艺”)是一种与其他物理和化学工艺相结合的综合技术。也是降低功率器件的功率损耗,提高电子产品的功率利用率是一项重要技术。它还为新产品(例如太阳能电池,微计算机处理(MEMS))奠定了基础。

目前,军事,航空,航天等领域的电路中的许多模块要求芯片和其他基本电子部件的背面具有可焊接性,以满足焊接和组装后的高可靠性要求。晶圆背面金属化技术在中国已经相当成熟,但仍处于单芯片开发阶段。那具体来讲,晶圆背金工艺技术到底是个啥,对芯片的制造有哪些用处和影响等等,这就是本章节我要跟大家分享的主题了。

一、背金工艺技术的介绍

背金,英文全称:Backside Metallization,简称:BSM,部分场景也会称作:BM,中文全称:背面金属化。而背金工艺是晶圆背面淀积金属化过程的一种工艺技术,晶圆经过减薄后,用PVD的方法(溅射和蒸镀)在晶圆的背面镀上金属。它的主要目的在于通过金属层的特性提升芯片的散热性能、机械稳定性以及与外部电路的连接能力,从而确保芯片的可靠性与工作效率。

二、背金(BSM)的金属组成

为实现良好附着、防止扩散及优化焊接,背金(BSM)层通常采用多层结构,每层功能各异。一般会有黏附层、阻挡层和防氧化层(焊接层)三层金属组成,其中:

1、黏附层:通常是A,T或C等金属,主要是为了与S片背面有良好的结合力,并且降低欧姆接触的阻值。如果T与硅的结合力不好,会造成金属层剥离与阻抗四上升等问题。

2、阻挡层:是位于黏附层之上,通常是纯Ni或NiV合金,作用是防止金属的扩散,避免因扩散形成的高阻化合物影响器件性能。

3、防氧化层(焊接层):作为最外层,通常是Ag,Au,需具备良好的导电导热性、抗氧化性以及与焊料的润湿性,该层直接参与后续的芯片焊接或粘接过程。常见的组合有:

a. MOSFET需求的钛(20-200nm)/镍(200-400nm)/银 (100-2000nm),即:Ti/NiV/Ag

b. IGBT需求的铝/钛/镍钒/银,即:(AI/Ti/NiV/Ag)等等。

在一些高端应用中,背金(BSM)结构可能更为复杂,包含种子层或多层组合,以适应高温、高功率等苛刻工作条件。

三、背金(BSM)工艺流程

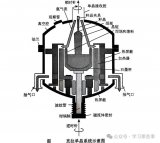

完整的背金(BSM)工艺包含一系列精密步骤,确保金属层与硅基底牢固结合并发挥预期功能。所以,总结归纳其主要流程有如下四个:

如上图,步骤为: Tape → Grinding → Si Etch → Detape → Pre-Treatment → Back Metal 即:贴胶纸→减薄→硅刻蚀→撕胶纸→预处理→背面金属化;

1、Tape(贴胶纸)

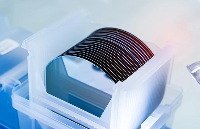

在晶圆正面贴上下图所示的蓝色胶带,保护晶圆正面的图形。

加工完产品后,需要逐片检查贴膜质量,要求整张膜下面都没有气泡,贴膜在硅片表面的颜色要均匀、一致,硅片边缘的膜要切割整齐、光滑,膜的边缘和硅片边缘一致,上述任何一项不满足, 都要撕掉膜,重新贴膜。

2、Grinding(减薄)

将硅片背面研磨,减薄到适宜厚度,采用机械抛光的方法;

表面研磨的目的是利用物理原理将晶片表面改善,使之变得更光滑、更平整,以减少背金后造成的缺陷,提高金属覆盖层的稳定性及可靠性,洁净表面也会有助于金属的真空贴装及准备工作。

3、Si Etch(硅刻蚀)

在背面减薄之后,硅片背面会有很多缺陷,并且有硅粉残留。此时wafer内部应力很大,容易碎片,硅腐蚀可以消除其内部应力,并且使其表面粗糙度更大,金属更容易在其上淀积。

常用硝酸和氢氟酸进行刻蚀处理,方程式为:

Si+HNO3+6HF=H2SiF6+H2NO2+H2O+H2;

4、Detape(撕胶纸)

此工序就比较简单了,在此就不过多赘述了;

5、Pre-Treatment(预处理)

硅片背面的清洁度对种子层金属与Si的结合力影响很大,因此要保证足够的清洁,一般用BOE洗去硅表面的自然氧化层。此步骤对保证金属与硅的结合强度至关重要。

6、Back Metal(背面金属化)

背面金属化这是核心步骤,通常采用物理气相沉积法,如电子束蒸发或磁控溅射两种方法,在真空腔体内,依次沉积多层金属薄膜。

最常见的是用电子束蒸发的方法,将被蒸镀的晶片内部的金属原料以特定的方式热镀至晶片的表面,以形成一层薄膜覆盖;金属的镀膜厚度通常介于10~30微米之间。

以Ti/Ni/Au(Ag)为例,当前我曾见过的对应的金属厚度为:

Ti1kÅ,Ni3.5kÅ,Au(Ag)1kÅ(6kÅ),当然厚度可以根据具体的场景而不同。

其实,严格来讲,在做完Back Metal(背面金属化)后,是还有一道叫“转染”的工序,它的主要作用是清除金属覆盖层上的金属残渣,以避免在后续制程中晶片表面发生断裂及缺陷,也是比较重要的呢。

四、背金(BSM)工艺基础知识介绍

以下就是本章节主要跟大家分享的内容了,希望有兴趣的朋友或是同行可以一起交流学习:

因为本培训资料章节太多,完整版如有朋友有需要,可私信我邀请您加入我“知识星球”免费下载PDF版本。注意:此资料只可供自己学习,不可传阅,平台有下载记录,切记!欢迎加入后一起交流学习。

五、背金(BSM)工艺的优缺点

1、优点:

a. 散热性能提升

背面金属层(如银、金)具有高导热性,能快速导出芯片工作时产生的热量,降低热应力,尤其适用于高功率器件(如CPU、IGBT)和LED封装。

b. 机械稳定性增强

金属层可加固减薄后的晶圆,减少后续加工或使用中的破碎风险,提高封装整体可靠性。

c. 优化电学连接

金属层(如钛)与硅形成良好的欧姆接触,降低接触电阻,同时为焊接或导电胶提供稳定界面,提升电气连接性能。

d. 抗环境干扰

金属覆盖层能保护芯片背面免受氧化、污染及电磁干扰,延长器件寿命。

e. 工艺兼容性高

多层金属结构(如Ti/Ni/Ag)设计灵活,可适配不同应用需求(如功率器件或太阳能电池)。

2、缺点

a. 成本高昂

需专用设备(如电子束蒸发台)和贵金属材料(如银、金),工艺复杂,对生产环境(真空度、清洁度)要求严苛。

b. 工艺控制难度大

易因清洁不彻底、真空泄漏等问题导致金属层剥离(Peeling)或溅源缺陷,影响良率。

c. 潜在性能影响

金属层可能吸收部分能量,对某些敏感电学参数(如高频信号)产生细微干扰。

d. 环境敏感性

金属层(如银)易氧化或受污染,需严格存储条件,否则可能出现黄斑、白斑等缺陷。

e. 厚度与均匀性挑战

金属层过薄或分布不均可能导致附着力不足,需精确控制参数(如预热温度、蒸发速率)。

背金(BSM)工艺虽在散热、机械强度和电学性能上优势显著,但其高成本和工艺复杂性限制了其在成本敏感型产品中的应用。未来发展方向可能聚焦于材料创新(如替代贵金属)和工艺优化(如减少缺陷率)。

六、晶圆背金(BSM)脱落品控标准

前面讲过,钛(Ti)在半导体封装中常用作黏附层,因为它与许多半导体材料和金属都有良好的结合力。对于Si和SiC,Ti通常都能形成稳定的亲和性很好的化合物,从而提供良好的黏附效果。

而SiC是一个比较硬的材料,具有更高的化学稳定性。这可能导致Ti与SiC的结合力略低于与Si的结合力,但差异可能不大,关键的评估指标通常是背金(BSM)层的剥离强度或脱落比例。

SiC 背金(BSM)金属体系较多,Ti是非常常见的黏附层,Ti/Ni/Ag或者其他金属都可以,其他的金属层如Ni和Ag也常用作导电层和焊接层。

通常会基于以下几点考虑:

a. 结合强度:确保背金(BSM)与SiC有良好的结合力;

b. 热和电性能:金属应该有良好的热和电导性;

c. 可靠性:考虑金属之间可能的扩散和反应,选择能够在所需的工作温度和环境中提供稳定性的金属体系。

所以,在背金(BSM)工艺中,脱落比例和脱落强度是衡量产品质量的重要指标:

1、脱落比例标准

在背金(BSM)工艺中,单个芯片镀层脱落的比例是一个关键的质量控制点,根据行业实践,单个芯片镀层脱落≥10%被视为不良。此外,整个圆片镀层脱落的比例也是一个考量因素,整个圆片镀层脱落≥5%同样被视为不良。

2、脱落强度标准

背金(BSM)工艺中,背面(BSM)金属与硅片背面的粘附性是至关重要的。在传统的背金(BSM)工艺中,由于超薄硅片的过度研磨、金属附着面的粗糙度不匹配、单层金属蒸镀等问题,直接降低了背面金属与硅片背面的粘附性,造成了硅片的早期失效。因此,提高背金(BSM)工艺的可靠性和良率是工艺优化的重要目标。

通过优化工艺,如背面粗糙化和背面金属蒸镀工艺,可以提高背面金属层的粘附性。例如,通过多层金属(Ti, Ni, Ag)的系统选择和工艺参数的重新设定,可以提高背面金属层的粘附性。这些标准和实践表明,背金(BSM)工艺中对脱落比例和脱落强度的控制是非常严格的,以确保半导体的产品的可靠性和性能。

七、芯片背金(BSM)脱落的影响(Impact of Peeling)

内行的朋友都知道:背金/背银层的主要作用是欧姆接触(导电)、散热通道以及共晶/粘贴附着界面。一旦发生脱落,会在晶圆减薄、划片(Dicing)、固晶(Die Attach)及最终使用阶段引发严重后果,具体带来的影响有如下几点:

1、电性能失效 (Electrical Failure)

接触电阻增大 (High Rdson/Vf): 对于垂直结构器件(如Power MOSFET, IGBT, 二极管),电流需要从芯片背面流出。背金(BSM)脱落会导致有效接触面积减小,接触电阻急剧上升,导致器件压降(Vf/Rdson)超标。

开路 (Open Circuit): 严重脱落会导致芯片与引线框架(Leadframe)完全断开,造成开路失效。

2、热性能失效 (Thermal Failure)

热阻增加 (Increased Rth): 背金(BSM)是热量传导的关键界面。脱落会导致芯片与基板之间产生空气隙(Air Gap),极大增加热阻。

过热烧毁: 在大功率工作下,热量无法及时导出,导致结温(Junction Temperature)过高,引发热击穿或烧毁。

3、封装工艺良率损失 (Process Yield Loss)

固晶失效 (Die Attach Failure): 在Die Bond工艺中,如果背金(BSM)附着力差,银浆或焊料无法润湿芯片背面,导致Die Shear(剪切力)强度不足,芯片在后续打线(Wire Bond)或模塑(Molding)过程中位移或飞出(Die Fly)。

划片崩缺 (Dicing Chipping): 附着力差的金属层在划片刀的高速切割下容易卷边、撕裂,甚至带动硅衬底崩缺。

4、可靠性风险 (Reliability Risks)

分层 (Delamination): 在回流焊(Reflow)或温度循环(TC)测试中,由于热膨胀系数(CTE)不匹配,微小的脱落会扩展为大面积分层,导致“爆米花效应”(Popcorn Effect)。

八、芯片背金(BSM)脱落不良的发生原因(Root Causes)

导致背金(BSM)脱落的原因通常涉及晶圆表面状态、沉积工艺和后续热处理三个方面:

1、晶圆表面处理不当 (Pre-treatment Issues)

a. 有机污染/氧化层

硅片背面在沉积金属前未清洗干净,残留的有机物、切削液、手指印或自然氧化层(Native Oxide)会阻隔金属原子与硅原子的结合。

b. 表面粗糙度 (Roughness)

(1). 过光滑: 经过过度抛光(Polishing)的硅表面缺乏机械互锁(Mechanical Interlocking)结构,物理附着力较差。

(2). 损伤层: 减薄(Back Grinding)后未有效去除损伤层(Damage Layer),导致金属层附着在松动的硅晶格上。

2、沉积工艺异常 (Deposition Process Issues)

a. 真空度不足

蒸发(Evaporation)或溅射(Sputtering)时真空度不够,导致残余气体(如氧气、水汽)掺入金属膜,形成氧化物夹杂,削弱附着力。

b. 温度控制

沉积时晶圆温度过低,金属原子动能不足,无法形成致密的薄膜;温度过高可能导致光刻胶(如有)碳化或应力过大。

c. 应力失配

沉积速率过快或膜厚设计不合理,导致金属内部积累巨大的内应力(Tensile or Compressive Stress),当应力超过附着力时即发生自发剥离。

d. 阻挡层缺失

对于金/银等不活泼金属,直接沉积在硅上附着力极差。如果没有钛(Ti)、铬(Cr)、镍(Ni)或钛钨(TiW)作为粘附层(Adhesion Layer),极易脱落。

3、后续工艺影响 (Post-Process Impact)

a. 合金化/烧结不足

沉积后的退火(Sintering/Alloying)温度或时间不足,未能形成牢固的金属硅化物(Silicide)合金层。

b. 划片水压过大

在划片清洗过程中,高压清洗水流直接冲击切口边缘,如果边缘附着力稍弱,会被冲起剥落。

九、芯片背金(BSM)脱落的失效机理(Mechanism)

背金(BSM)脱落的微观失效机理主要可以归纳为以下三大类:

1、界面结合力不足 (Weak Interface Bonding)

a. 范德华力失效

这是物理吸附的主要力量。当界面存在沾污时,金属原子无法靠近硅原子到足以产生强范德华力的距离。

b. 化学键缺失

理想的背金(BSM)工艺(如Ti/Ni/Ag)中,底层Ti会与Si反应生成TiSi₂(钛硅化物),形成极强的共价键化学锚定。如果界面有氧化硅(SiO₂)阻挡,无法形成硅化物,附着力将大幅下降。

2、应力释放 (Stress Relaxation)

金属薄膜与硅衬底的CTE(热膨胀系数)差异巨大(Si: ~2.6ppm/°C, Al: ~23ppm/°C, Au: ~14ppm/°C)。在经历冷热冲击时,界面产生巨大的剪切应力(Shear Stress)。当 剪切应力 > 界面结合强度 时,发生分层脱落。

3、柯肯达尔效应 (Kirkendall Effect) - 针对多层金属

在高温老化过程中,如果阻挡层(如Ni)失效,不同金属层之间扩散速率不同,会在界面处形成微空洞(Voids),导致机械强度变弱进而剥离。

十、芯片背金(BSM)脱落不良的检测与拦截(Detection & Screening)

其实,讲到如何在出货前拦截芯片背金(BSM)脱落不良的问题,应该说是仁者见仁,智者见智吧。因为每家半导体公司的制程工艺质量管理都有自己一套定律和手段的,在此,只能综合归纳一下现比较常见的检测与拦截方法:

1、在线监控 (In-line Monitor)

a. 百格测试 (Cross-Hatch Tape Test)

这是最经典的一种方法,在晶圆陪片(Dummy Wafer)或边缘区域用刀片划出网格,贴上3M 600或610胶带,迅速撕下,观察有无金属格脱落。(标准:ASTM D3359)

b. 划痕测试 (Scratch Test)

使用硬度计或专用探针在膜层表面施加压力划动,检测膜层破裂或剥离的临界载荷。

c. 外观检查 (Visual Inspection)

显微镜下观察金属层是否有起泡(Blistering)、变色或边缘卷起。

2、破坏性测试 (Destructive Test)

a. 煮沸实验 (Boiling Test)

将晶圆放入沸水中煮一定时间(如1小时),取出后做Tape Test。这是模拟恶劣环境下水汽侵入界面的能力。

b. Die Shear Test (固晶剪切力)

将芯片粘贴在基板上,推刀测试芯片受力脱落时的模式,若发生硅裂(Silicon fracture)或胶裂(Cohesive failure)即为合格,但如果发生金属层与硅面分离(Metal peeling from Si)即为不合格。

十一、芯片背金(BSM)脱落不良的验证方法 (Verification Methods)

当发生背金(BSM)脱落问题并导入改善措施后,需进行以下验证:

1、可靠性验证 (Reliability Qualification)

a. TC (Thermal Cycling):

-55°C ~ 150°C, 500-1000 cycles;

b. PCT (Pressure Cooker Test) / HAST

高温高湿高压下,加速水汽渗透,验证抗腐蚀和抗剥离能力;

c. HTS (High Temp Storage)

高温存储,验证金属间化合物扩散导致的空洞剥离;

2、微观结构分析 (FA)

a. SEM/EDX

观察剥离界面。如果剥离面上只有硅,说明金属完全没沾上;如果有金属残留,需分析断裂发生在哪一层(如Ti与Ni之间,还是Ti与Si之间);

b. FIB (聚焦离子束)

切片观察界面是否有氧化层、空洞或微裂纹;

c. AES/XPS

分析界面极薄的化学成分,检测是否有C(有机沾污)或O(氧化)元素富集。

十二、芯片背金(BSM)脱落不良的预防与改善对策 (Prevention & Improvement)

1、表面处理优化

a. 加强清洗

在蒸镀/溅射前,必须进行严格的化学清洗(如HF酸洗去除原生氧化层);

b. 原位反溅 (In-situ Sputter Etch)

在PVD机台真空腔体内,镀膜前先用氩气(Ar)等离子体轰击硅片表面,物理去除表面氧化层和吸附水,并活化表面(增加表面能)。这是解决背金脱落最有效的手段之一;

2、膜层结构设计

a. 引入粘附层

必须使用Ti、Cr、TiW等与硅亲和力强的金属打底。推荐结构:Ti/Ni/Ag 或 Cr/Ni/Au;

b. 优化厚度

粘附层不宜过厚(通常几百埃 Å),过厚会增加内应力;也不宜过薄,需保证覆盖率。

3、工艺参数调整

a. 基板加热

沉积过程中适当加热晶圆(如150°C-300°C),增加原子迁移率,促进界面合金化反应,形成牢固的键合;

b. 控制粗糙度

背面减薄工艺(Backgrinding)后,通过抛光或湿法腐蚀(Stress Relief Etch)控制在一个适宜的粗糙度范围(Ra 0.1~0.4μm 左右通常较好,具体视胶体和金属而定),既去除损伤层又保留一定的机械互锁能力;

4、烘烤与合金化

沉积后进行退火处理(Annealing),温度通常在400°C左右(视共晶点而定),使界面金属与硅相互扩散形成硅化物,这是将“物理吸附”转变为“化学键合”的关键步骤。

十三、背金(BSM)工艺的技术特点与应用领域

背金(BSM)工艺作为一项关键封装技术,具有鲜明的技术特点和广泛的应用前景,同时也面临一定的挑战。

该工艺的主要优点包括:显著提升芯片的散热能力,降低工作温度;增强芯片机械强度与封装整体可靠性;提供稳定、低阻的背面电学接触界面;保护芯片背面免受环境污染;有利于后续的真空贴装等工艺步骤。

然而,背金(BSM)工艺也存在一些缺点与挑战:工艺成本较高,涉及专用设备(如电子束蒸发台)和高端材料;工艺控制复杂,易受真空度、清洁度等因素影响,可能产生金属层剥离(Peeling)、溅源等缺陷;金属层的引入可能对某些极端敏感的电学参数产生细微影响。

目前,背金(BSM)工艺主要应用于以下领域:功率半导体器件,如电动车电机控制器、变频空调中的IGBT和MOSFET,这些器件发热量大,对散热要求极高;高端计算芯片,如CPU、GPU处理器,需要高效的散热和稳定的封装连接;LED封装,以提高散热效能和延长寿命;太阳能电池板,提升其转换效率和长期可靠性。

十四、写在最后面的话

总体来讲,芯片背金(BSM)工艺是晶圆后端封装的关键工序之一,核心是在晶圆背面(与器件面相对)沉积金属层(通常为 Ti/Ni/Au 或 Cr/Ni/Au 多层结构),作用是增强芯片与基板的导电性、散热性及粘接可靠性,常见于功率器件、高频芯片等对电气 / 热性能要求较高的产品。该工艺一般通过磁控溅射或蒸发镀膜实现,需严格控制金属层厚度、附着力及表面平整度,以适配后续的 Die Bond(芯片粘接)工序。

背金(BSM)脱落是该工艺的典型不良,核心诱因分为三类:

1、工艺制程缺陷

晶圆背面预处理(如去胶、清洗)不彻底,残留有机杂质 / 颗粒导致金属层与晶圆基底附着力不足;镀膜过程中真空度不足、温度波动大,造成金属层结晶不良、分层。

2、材料匹配性问题

背金(BSM)金属层与晶圆衬底(如 Si、SiC)的热膨胀系数差异过大,封装后温变循环中产生应力,引发界面剥离;塑封料与背金层的化学兼容性差,固化过程中释放的小分子腐蚀金属界面。

3、后段工序损伤

晶圆减薄、切割过程中机械应力过大,导致背金(BSM)层微裂纹;Die Bond 时压力不均、温度异常,破坏背金与芯片的结合界面。

解决背金(BSM)脱落需从全流程管控:优化背面清洗工艺(增加等离子清洗)、控制镀膜参数(稳定真空度与温度)、选用匹配性更优的金属层组合,同时规范后段机械加工的应力控制,配合附着力测试(如划格法)提前筛查风险,可有效降低不良率。

随着半导体技术向更高功率密度、更小尺寸和更高集成度发展,背金(BSM)工艺将持续高速演进,特别是在材料体系、工艺精度和集成方案上都会有不断的创新,以满足未来电子产品对性能与可靠性的严苛需求,所以对于背金(BSM)工艺当前存在的制程缺陷也在一步步提升和完善当中。

分享一份芯片背银/背金脱落失效模式及效应研究图表:

参考资料

1. 芯片制造中的背金工艺介绍; ——中国科学院半导体研究所;

2. 背金工艺的作用是什么? ——CSDN博客;

3. 道功率芯片背金工艺优化和缺陷改善; ——豆丁网;

4. 半导体的背金工艺简介以及脱落比例; ——梵易 Ryan;

5. 芯片背银_背金脱落(Backside Metallization Peeling)失效模式及效应研究; ——小马哥;

6. 半导体制程中“背金工艺”的详解; ——公众号 爱在七夕时;

免责声明

【我们尊重原创,也注重分享。文中的文字、图片版权归原作者所有,转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时私信联系,我们将第一时间跟踪核实并作处理,谢谢!】

审核编辑 黄宇

-

半导体晶圆

+关注

关注

0文章

49浏览量

5660

发布评论请先 登录

智测电子 TC Wafer 晶圆有线测温系统 半导体高精度多点测温方案

wafer晶圆厚度(THK)翘曲度(Warp)弯曲度(Bow)等数据测量的设备

瑞乐半导体——TC Wafer晶圆测温系统持久防脱专利解决测温点脱落的难题

半导体晶圆“背金(Backside Metallization)工艺”技术的详解;

半导体晶圆“背金(Backside Metallization)工艺”技术的详解;

评论