深度解析ADC3668/3669:高性能ADC的卓越之选

在电子设计领域,模拟到数字转换器(ADC)的性能往往直接影响着整个系统的表现。今天,我们就来深入剖析一款备受关注的ADC产品——德州仪器(TI)的ADC3668和ADC3669。

文件下载:adc3669.pdf

一、产品概述

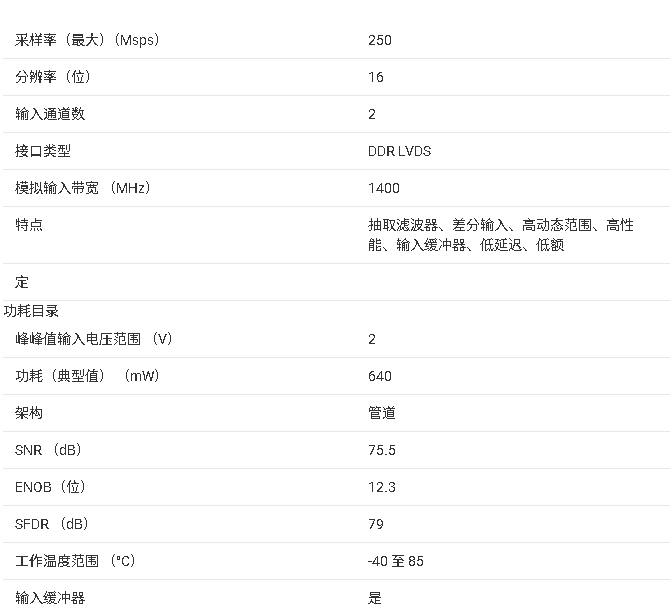

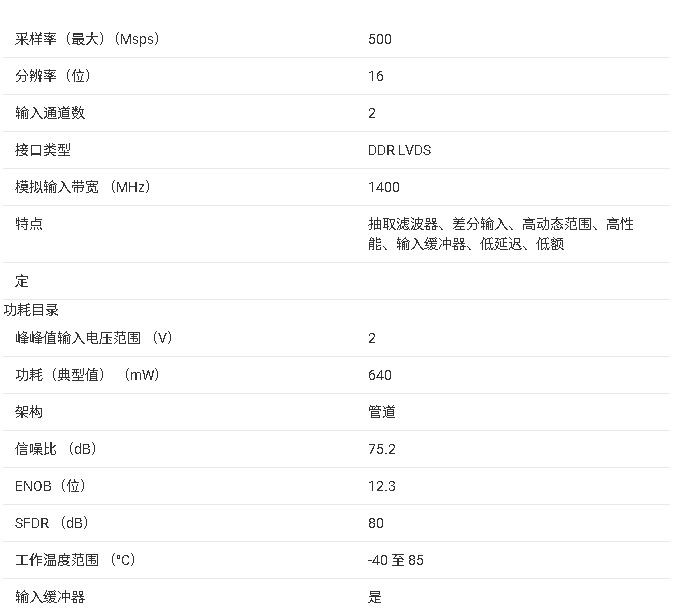

ADC3668和ADC3669(统称ADC366x)是16位、双通道的ADC,采样率分别可达250MSPS和500MSPS。这两款产品专为实现高信噪比(SNR)而设计,噪声频谱密度低至 -160dBFS/Hz,在同类产品中表现卓越。其采用单核心(非交错)ADC架构,孔径抖动仅为75fs,为高精度信号转换提供了有力保障。

二、关键特性

2.1 模拟输入特性

- 可编程输入阻抗:模拟输入具有内部缓冲器,可将采样电容的毛刺噪声与外部输入电路隔离开来。输入阻抗可通过SPI寄存器编程设置为100Ω或200Ω的差分终端,输入满量程为2Vpp,共模电压 (V_{CM}) 为1.4V。

- 宽输入带宽:全功率输入带宽(-3dB)达到1.4GHz,能够处理高频信号,适用于多种应用场景。

- Nyquist区选择:内置数字误差校正功能,可根据感兴趣信号所在的Nyquist区进行优化。通过SPI寄存器选择正确的输入频率范围和Nyquist区,可实现最佳性能。

- 模拟前端设计建议:为优化ADC的SNR和HD3性能,建议在模拟输入前端添加RCR电路。当输入频率低于或高于500MHz时,RCR电路的参数有所不同。若ADC由外部放大器驱动,则可能无需RCR电路。

2.2 采样时钟输入

- 差分输入设计:采样时钟输入采用差分驱动方式,需外部交流耦合和终端匹配。ADC内部提供共模电压偏置,内部采样时钟路径设计旨在降低残余相位噪声。

- 时钟噪声特性:内部残余时钟噪声由相位噪声和幅度噪声两部分组成。相位噪声随输入频率和采样率变化,而幅度噪声则保持相对稳定。时钟的幅度也会影响内部残余时钟噪声,因此在设计时需要选择合适的时钟幅度。

2.3 多芯片同步

- 不同模式下的同步方式:在DDC旁路模式下,设备本身具有确定性延迟,可通过匹配各设备的时钟走线实现外部多芯片同步。同时,可使用SYSREF信号重置内部RAMP测试模式。在DDC模式下,使用SYSREF信号将与抽取滤波器相关的内部模块(如时钟分频器、NCO相位等)重置为确定性状态,并通过匹配时钟和SYSREF信号走线实现外部多芯片同步。

- SYSREF监控:设备内部设有SYSREF监控电路,用于检测SYSREF信号在采样瞬间附近的逻辑电平亚稳态,以避免设备间的对齐误差。该电路可检测SYSREF逻辑状态转换是否在采样时钟上升沿的 -60ps至 +140ps范围内,并相应地触发SYSREF XOR标志。

2.4 时间戳功能

ADC366x具备时间戳功能,可在DDC旁路模式下对模拟输入的特定样本进行标记。通过SPI使能该功能后,GPIO/SYSREF引脚的逻辑低到高转换将在采样时钟的上升沿被记录,并在DOUT0(LSB)通道输出时间戳信号,但该信号与输出数据的延迟不匹配。

2.5 过范围指示

当信号超出可表示的数字范围(最大代码)时,设备会触发过范围指示。过范围输出可通过寄存器配置,指示方式有两种:一是通过GPIO引脚,每个通道可使用一个GPIO OVR引脚,或使用一个GPIO引脚将两个ADC的OVR信号进行OR运算;二是在LSB数据中,OVR信号可替代每个通道输出数据的LSB。

2.6 外部电压参考

为实现高精度和低温度漂移,可通过GPIO1引脚为ADC提供外部1.2V电压参考。建议在GPIO1和AGND引脚之间连接10µF和0.1µF的陶瓷旁路电容器,并尽量靠近引脚放置。

2.7 数字增益

设备为两个通道都提供了可编程数字增益,可通过寄存器0x15B(CHA)和0x15C(CHB)进行设置。8位寄存器字段包含7位数据和1位符号位(2的补码),实际增益(dB)计算公式为:20 x log (1 + (7位增益 / 128))。

2.8 抽取滤波器

- 多通道配置:ADC366x最多可提供四个数字下变频器(DDC),通过交叉点开关和SPI寄存器设置,可将任意DDC连接到任意ADC或2x AVG模块的输出。双频段模式(2个DDC)支持 /2 至 /32768的抽取,而4个DDC模式下最小抽取比为 /4。

- 不同抽取方式:支持实抽取(单频段)和复抽取,实抽取的通带约为40%,复抽取的通带约为80%。抽取功能可通过设置SPI寄存器(0x169, D3 - D0)来启用,默认设置为实抽取,复抽取出通过寄存器

(0x162, D2) 启用。 - 非均匀抽取比:DDC可被编程为具有不等的、独立的抽取比,输出数据速率基于抽取滤波器中最低的抽取比。抽取比高的DDC输出样本会在输出数据流中相应重复。

- 抽取滤波器响应:复滤波器的通带约为80%(-1dB),阻带抑制至少为85dB。文档中提供了不同抽取比下的滤波器响应曲线,展示了滤波器的通带、过渡带和阻带特性。

- 抽取滤波器配置:数字抽取滤波器的操作可通过寄存器0x163至0x169控制,NCO频率映射到寄存器0x200至0x2DF。通过一系列寄存器设置,可配置DDC以实现不同的工作模式,如固定NCO频率或慢变化NCO频率的静态工作模式。

2.9 数字接口

- DDR LVDS接口:在DDC旁路模式下,使用16位宽的DDR LVDS接口输出数据,利用输出时钟的上升沿和下降沿进行传输。输出数据的ChA/ChB通道的DOUT0/1/2可被过范围输出OVR、PRBS位或时间戳信号替代,具体配置可通过寄存器实现。

- 串行LVDS(SLVDS)接口:在使用实抽取或复抽取时,输出数据被序列化并通过较少的LVDS发射器传输。帧时钟(FCLK)标记样本的开始和结束,数据位在数据时钟(DCLK)的上升沿和下降沿输出。输出接口映射默认从DOUT15开始,输出通道数量和数据速率可根据相关参数计算。

- 输出数据格式和分辨率:输出数据格式可通过SPI寄存器设置为二进制补码(默认)或偏移二进制格式。ADC366x支持16位和32位输出分辨率,对于较高的抽取比(实抽取 /16 或更高、复抽取 /32 或更高),建议使用32位输出分辨率以避免因量化噪声限制导致的SNR下降。

- 输出扰码器和MUX:设备包含一个可选的输出扰码器,内部PRBS生成器生成的PRBS模式与每个数据位进行XOR运算,扰码后的数据通过并行或串行LVDS传输,同时PRBS位可替代输出数据的LSB、LSB - 1或LSB - 2。LVDS输出接口还包括一个输出MUX,可将任何内部数字通道重新路由到任何LVDS输出通道,提供通道映射的灵活性,可用于链路冗余或修复。

- 测试模式:设备内置测试模式发生器,用于简化LVDS输出的调试和校准。启用测试模式发生器后,会替代当前所有输出数据样本,测试模式对所有通道相同,可通过寄存器配置为不同的模式,如具有自定义步长的斜坡模式。

三、电气特性

3.1 绝对最大额定值和ESD等级

文档给出了ADC366x在不同工作条件下的绝对最大额定值,包括电源电压范围、输入引脚电压范围、峰值RF输入功率、结温、存储温度等。同时,还给出了ESD等级,包括人体模型(HBM)和带电器件模型(CDM)的ESD耐受电压。

3.2 推荐工作条件和热信息

列出了推荐的工作条件,包括电源电压、工作环境温度、工作结温等。热信息部分给出了各项热指标,如结到环境的热阻、结到顶部的热阻、结到电路板的热阻等,为散热设计提供了重要参考。

3.3 电气特性 - 功耗、直流和交流规格

详细给出了不同采样率下的功耗、直流规格和交流规格。功耗方面,展示了不同电源电压下的供电电流和功耗,以及全局断电模式下的功耗。直流规格包括无缺失码、差分非线性(DNL)、积分非线性(INL)、失调误差、失调漂移、增益误差、增益漂移等。交流规格包括噪声频谱密度、噪声系数、信噪比(SNR)、信号与噪声和失真比(SINAD)、有效位数(ENOB)、总谐波失真(THD)、二次谐波失真(HD2)、三次谐波失真(HD3)、无杂散动态范围(SFDR)、双音互调失真(IMD3)等。

3.4 典型特性曲线

提供了大量的典型特性曲线,展示了ADC3668和ADC3669在不同工作条件下的性能表现。这些曲线包括不同输入频率下的频谱、AC性能与输入频率、采样率、时钟占空比、电源电压、共模电压、环境温度等参数的关系,以及DNL、INL、直流偏移直方图、脉冲响应等特性。

四、应用与实现

4.1 应用领域

ADC366x适用于多种应用领域,包括雷达、频域数字化仪、频谱分析仪、测试和通信设备以及软件定义无线电(SDR)等。

4.2 典型应用 - 宽带频谱分析仪

详细介绍了宽带频谱分析仪的典型配置,包括输入信号路径、时钟设计和详细的设计步骤。输入信号路径需要使用适当的带限滤波器来抑制不需要的频率,使用平衡变压器将单端RF输入转换为差分输入,并进行交流耦合。时钟输入必须进行交流耦合,时钟源应具有低抖动,可使用带通滤波器去除部分宽带时钟噪声。在多通道系统中,SYSREF信号可使用LMK04828或LMK04832设备生成。

4.3 详细设计步骤

- 采样时钟:为了最大化ADC的SNR性能,需要一个低抖动(< 75fs)的采样时钟。文档展示了SNR与输入频率、外部时钟抖动和时钟幅度的关系曲线,同时说明了在使用平均和/或抽取时,需要先估计单个ADC核心的SNR,再考虑内部平均和/或抽取带来的SNR改善。

- 初始化设置:上电后,需要通过在RESET引脚施加高脉冲来对内部寄存器进行硬件复位,将其初始化为默认值。文档给出了详细的上电时序和寄存器初始化步骤,以及在需要时使用SPI对内部寄存器进行编程的方法。

4.4 电源供应建议和布局

- 电源供应:ADC需要四种不同的电源供应,AVDD18和AVDD12为内部模拟和时钟电路供电,DVDD18和DVDD12为数字逻辑和LVDS数字接口供电。电源序列需要按照特定顺序进行,并且电源需要低噪声以实现数据手册中的性能。建议使用高效降压开关稳压器和低噪声LDO进行两级稳压,同时在引脚附近放置去耦电容。

- 布局:在电路板设计中,对于模拟输入和时钟信号、数字LVDS输出接口以及电源和接地连接有特定的布局要求。模拟输入和时钟信号的走线应尽量短,避免过孔,采用松散耦合的100Ω差分走线,并尽量匹配差分走线长度。数字LVDS输出接口应采用紧密耦合的100Ω差分走线。电源和接地连接应提供低电阻路径,使用电源和接地平面,避免窄的、孤立的路径。

五、总结

ADC3668和ADC3669凭借其卓越的性能、丰富的功能和灵活的配置,为电子工程师在设计高性能数据采集系统时提供了一个强大的选择。无论是在雷达、通信、测试测量还是其他领域,这两款ADC都有望发挥重要作用。在实际应用中,工程师需要根据具体需求,合理设计输入电路、时钟电路、电源电路和布局,以充分发挥ADC的性能优势。同时,通过对文档中提供的各种数据和曲线的分析,工程师可以更好地理解ADC的工作特性,为系统设计提供有力支持。大家在使用过程中有遇到什么问题,或者有更好的应用经验,欢迎在评论区分享交流。

-

电子设计

+关注

关注

42文章

2870浏览量

49916

发布评论请先 登录

ADC3668/ADC3669 数据手册总结

ADC3669 产品技术文档总结

深度解析ADC3668/3669:高性能ADC的卓越之选

深度解析ADC3668/3669:高性能ADC的卓越之选

评论