特性描述

FZH171(深圳市方中禾科技)是256点内存映象和多功能的LCD驱动专用芯片,FZH171的软件配置特性使它适用于多种LCD应用场合,包括:LCD模块和显示子系统。用于连接主控制器和FZH171的管脚只有4或5条,FZH171还有一个节电命令用于降低系统功耗。本产品性能优良、质量可靠。

功能特点

Ø工作电压2.4~5.2V

Ø内置32 KHz RC振荡器

Ø可外接32KHz频率源作为时钟输入

Ø内置时基频率源

Ø内置蜂鸣器输出驱动,有两种输出频率可选(2 KHz或者4 KHz)

Ø内置节电模式,可用于减少功耗

Ø内置时基发生器和看门狗(WDT)输出

Ø内置32ⅹ8位显示寄存器,32个SEG,8个COM输出驱动

Ø四线串行接口

Ø提供VLCD管脚用于调整LCD操作电压

Ø三种数据访问模式

Ø八个时基/看门狗定时器时钟源

Ø数据模式和命令模式指令

Ø四种封装形式可选:QFP44,LQFP44,QFP52,LQFP64

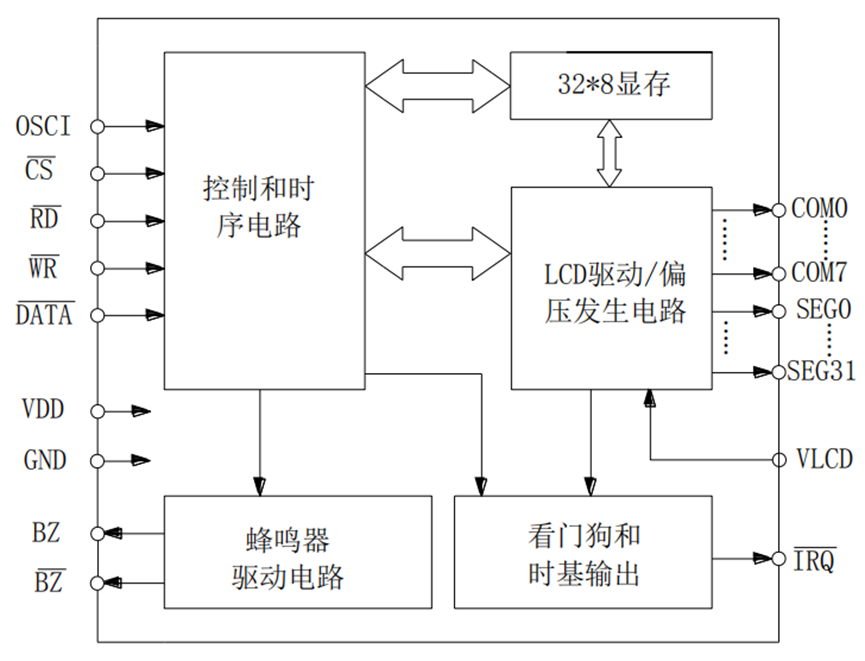

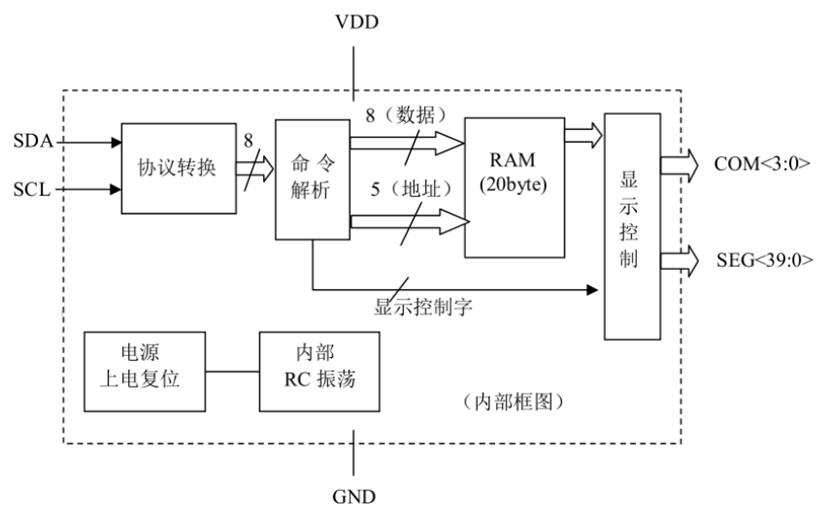

内部结构框图

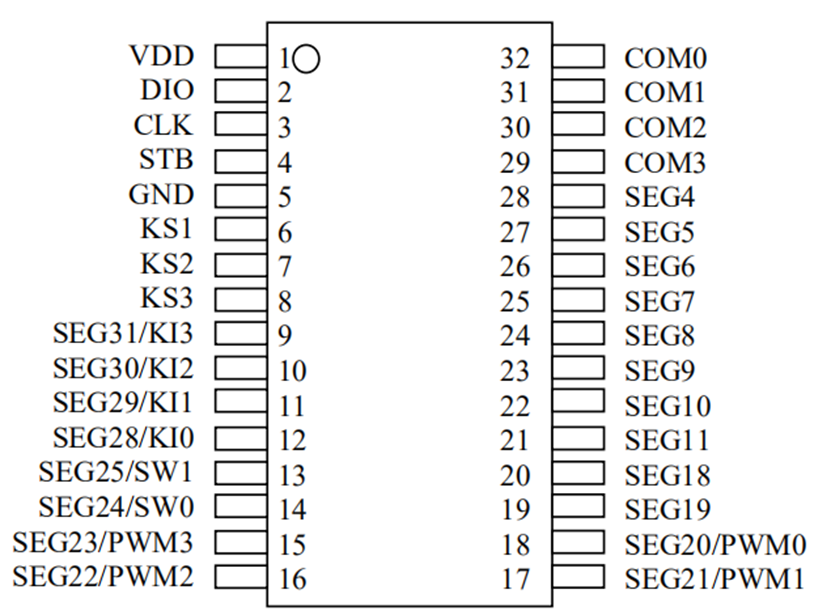

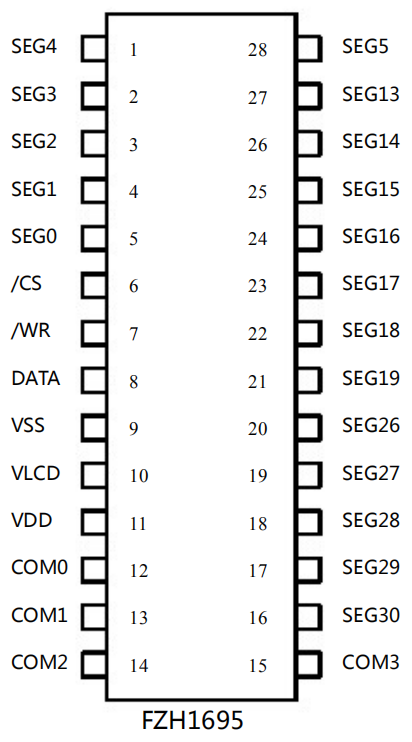

管脚排列

管脚功能

*备注:上表中的管脚序号,以 LQFP64封装为例。不同的封装,脚位有所不一样,详情请参考管脚排列图。

输入输出等效电路

集成电路系静电敏感器件,在干燥季节或者干燥环境使用容易产生大量静电,静电放电可能会损坏集成电路,建议采取一切适当的集成电路预防处理措施,不正当的操作焊接, 可能会造成ESD损坏或者性能下降,芯片无法正常工作。

极限参数

(1)芯片长时间工作在上述极限参数条件下,可能造成器件可靠性降低或永久性损坏,不建议实际使用时任何一项参数达到或超过这些极限值。

(2)所有电压值均相对于系统地测试。

推荐工作条件

DC电气特性

应用信息

说明:

1、上图给出的简图以LQFP64封装的芯片为例。

2、VLCD的电压必须小于或者等于VDD的电压。

3、VLCD的上拉可调电阻用来调节LCD的控制电压,当VDD=5.0V,Vlcd=4.0V,则VR=15K±20%。

4、如不需要读取FZH171的显存数据,RD可以不连接到MCU。

5、VDD对GND的电容可以滤掉芯片VDD 上的产生的纹波,所以此电容不能省掉,并在PCB布板时,尽 量接近芯片。

6、芯片时钟可选片内RC和外部时钟。如果使用内部RC振荡,OSCI脚必须保持浮空状态,*32KHz的时 钟必须撤离,否则芯片可能不能正常工作。。

7、FZH171开LCD显示后,COM口循环输出阶梯波,这一特性使得FZH171可以驱动2COM,4COM,8COM的LCD。

8、如果不使用时基/WDT功能, IRQ与 MCU的连线可以不连接。由于 IRQ为 Nmos开漏输出,所以如果 使用时基/WDT功能, IRQ必须接一 10K上拉电阻,否则 IRQ将不能输出高电平。

功能描述

1:显示内存(RAM)

静态显示内存包含 32×8位的格式来存储需要显示的数据,RAM的数据直接映像到 LCD显示驱 动器,也可以通过 READ,WRITE,和 READ-MODIFY-WRITE命令进行读写操作,下图给出的为 RAM映像图

2:时基和看门狗输出(WDT)

时基发生器和看门狗输出(WDT)共用相同的(÷256)分频电路, TIMER EN/DIS/CLR, WDT EN/DIS/CLR分别作用于时基发生器和看门狗电路。下图给出了示意图。

开启 WDT后,一旦 WDT超时,IRQ 将被拉低,并一直保持低电平状态直到执行 CLR WDT或者执行 IRQ DIS命令后,才会关断IRQ的输出,此时IRQ输出高阻状态,被外部上拉电阻强制拉为高电平状态。

如果选择外部时钟作为系统频率源时,SYS DIS命令无效,系统也不能进入省电模式。FZH171在断电或者撤消外部时钟前,一直保持工作状态。

3:蜂鸣器驱动输出

FZH171内置了一个简单的声音发生器,可以在BZ和BZ脚输出一对差动驱动信号,用于驱动蜂鸣器产生一个单音。执行TONE2K和TONE4K命令后,可以输出2KHz和4KHz频率驱动蜂鸣器发出两种不同的声音;TONEOFF命令可以用于关闭声音输出。当系统失效或者执行了TONGOFF命令后,BZ和 BZ将保持低电平输出状态。

4:命令模式

FZH171 可以用软件配置,两种模式的命令可以配置FZH171和读写显存的数据,FZH171的配置模式称为命令模式,对芯片显存进行操作模式,称为数据模式,下表中给出了数据和命令模式的类型码表:

模式命令应该在数据或者命令传送前发送。如果要传送的连续命令,命令模式类型码 100只能发送 一次,后续紧跟着的命令不同命令的命令代码。在不连续命令模式或者不连续地址的数据模式下每次发 完一个命令或者一个数据指令后, CS应该先置“1”,保证当前的的操作模式复位。 CS管脚置“0”后,应该先发送新的操作模式类型码。

5:通讯端口

FZH171 只有四个管脚用于与MCU的通讯,管脚 CS用于初始化串行接口电路和结束指令数据的传 送。CS置“1”时,FZH171 不接受任何MCU发送的命令和数据并且初始化串行接口。在不同的操作 类型码之间,CS必须用一个高电平初始化FZH171的串行接口,否则传送的命令或者数据会出错。 管脚 DATA是串行数据输入/输出脚,读/写数据可以通过 DATA与 RD , WR之间的配合来完成。管脚 RD是读显存时钟输入脚,在 RD信号的下降沿时,显存内的数据会被输出到芯片 DATA寄存器里面,在 RD的上升沿和下一个下降沿之间,DATA寄存器里面的数据会被读出到 DATA脚上。管脚 WR是写时钟输 入,在WR信号上沿,管脚DATA上的数据,地址,命令将被写入到FZH171。可选的管脚IRQ ,可用 作MCU与FZH171的通讯接口,IRQ 可以通过软件设置作为时基定时器输出或者WDT溢出标志位输出, MCU与FZH171的IRQ相连后,可以实现时基或者WDT功能的应用。IRQ由于是Nmos 开漏输出,使 用过程中必须加 10k上拉电阻。如果不需要使用时基或者 WDT功能, IRQ可以浮空。

读写时序图

READ 模式(命令代码:110)

READ模式(读连续地址)

WRITE模式(命令代码:101)

WRITE模式(写连续地址)

READ-MODIFY-WRITE 模式(命令代码:101)

READ-MODIFY-WRITE 模式(访问连续地址)

命令模式(命令代码:100)

数据和命令模式

备注:MCU应该在 RD的上升沿和下一个下降沿之间读取 DATA上的数据,且 RD和 WR 的波形不能 有交叉,即同一时刻,只允许单独对 RD或者 WR 进行操作。

命令概述表

注:

1:X不关心,建议写“0”。

2:A5~A0显存地址。

3:D0~D4显存数据。

4:D/C数据/命令模式。

5:上电复位后缺省:上电复位后芯片默认的状态 所有的粗体数字:即110,101,100为模式命令类型码。100为命令模式类型码,如果给FZH171发送连续的命令,除第一个命令外,其他的命令不能再发100类型码。声音频率源和时基/WDT时钟频率源由片内的32KHzRC振荡器或者外部的32KHz频率源提供。输出频率计算详见前文中系统描述章节的时基和看门狗输出(WDT)和上表中关于时基/WDT频率输出频率设置指令F0~F128。建议在上电复位后,用MCU初始化FZH171因为如果上电复位失败后,FZH171将不能正常工作。

TEST 指令(100 1110-0000-X),用户在正常使用过程中不得给芯片发送,否则芯片将进入测试模式,而不能正常执行MCU发送的其他命令和数据。

封装示意图(QFP44 10mm*10mm)

封装示意图(LQFP44 10mm*10mm)

封装示意图(QFP52 14mm*14mm)

封装示意图(LQFP64 7mm*7mm)

封装示意图(LQFP64 14mm*14mm,脚长 0.6mm)

封装示意图(LQFP64 14mm*14mm,脚长 0.85mm)

审核编辑 黄宇

-

芯片

+关注

关注

463文章

54463浏览量

469619 -

lcd

+关注

关注

36文章

4632浏览量

178050

发布评论请先 登录

LCD驱动芯片FZH171,应用开发相关数据技术手册

LCD驱动芯片FZH171,应用开发相关数据技术手册

评论