VCU编码帧率

最近有客户反馈VCU编码4K NV12 视频时, 帧率只能达到42FPS。

Vivado设计检查

通过检查Vivado设计,发现以下设计可能影响帧率,做了改进。

1. VCU与DDR连接的AXI Interconnect的位宽是32-bit。 建议改为64-bit或者128-bit。

2. VCU的AXI Master连接到了DDR的同一个Slave port。 建议同时运行的模块的AXI Master,连接到DDR的不同的Slave port,防止拥塞,充分利用带宽。

3. VCU Coding type 被设置成Intra Frame Only, 导致VCU Encode buffer为0。 建议设置为Intra & Inter Frame ,并设置Motion Vector Range为 medium,得到更大的VCU Encode buffer。

4. 使能VCU Encode buffer。

软件设计检查

1. 软件设置CacheLevel2为True,使用VCU Encode buffer。

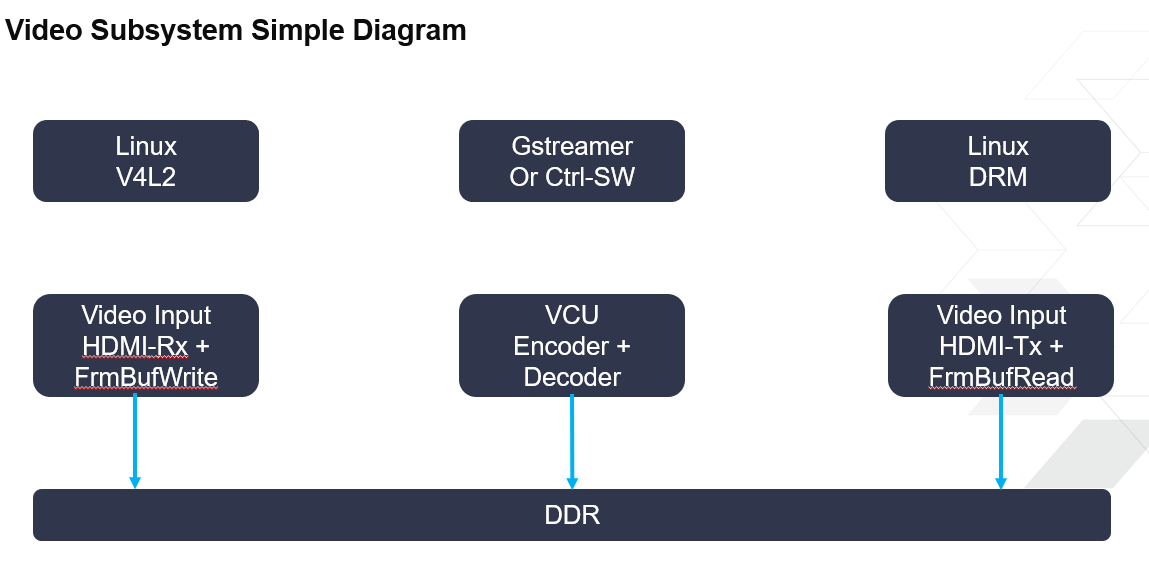

2. 使用HDMI-Rx等Live Vidoe,不使用filesrc,避免数据拷贝。

结论

经过以上改进后, 帧率可以达到64FPS。

VCU延时

客户使用在gst命令前添加GST_DEBUG="GST_TRACER:7" GST_TRACERS="latency" GST_DEBUG_FILE="/run/latency.txt"来测量VCU延时,发现解码延时达到5秒钟。 这是错误的结果。 单板没有足够的内存保存5秒钟的原始视频,甚至没有足够的内存保存2秒钟的原始视频。

建议使用 GST_DEBUG=omx:6 GST_DEBUG_FILE="/run/latency.txt"来测试VCU延时。在记录文件里搜索“retrieved latency”,可以看到各个模块的延时。

普通情况下的延时数据, 编码延时18ms,解码延时200ms。

0:00:00.408347321 4876 0xaaab00dce770 DEBUG omxvideoenc gstomxvideoenc.c:2659:gst_omx_video_enc_set_latency: retrieved latency of 18 ms

0:00:00.506572825 4876 0xaaab00e5c770 DEBUG omxvideodec gstomxvideodec.c:2481:gst_omx_video_dec_set_latency: retrieved latency of 200 ms

Low-Latency情况下的延时数据, 编码延时4ms,解码延时17ms。

0:00:00.422535568 8048 0xaaaae02f2770 DEBUG omxvideoenc gstomxvideoenc.c:2659:gst_omx_video_enc_set_latency: retrieved latency of 4 ms

0:00:00.521424529 8048 0xaaaae0382770 DEBUG omxvideodec gstomxvideodec.c:2481:gst_omx_video_dec_set_latency: retrieved latency of 17 ms

Low-Latency情况下的延时数据, 编码延时4ms,解码延时17ms。

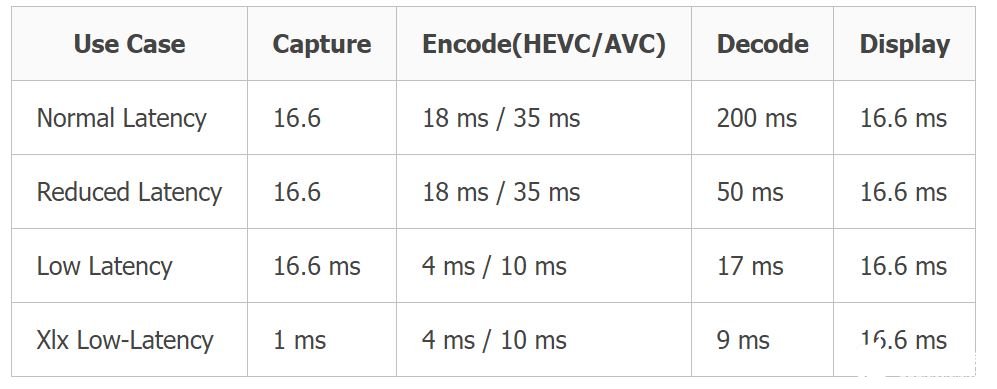

PG252中的Glass-to-Glass延时数据

Table 69: Glass-to-Glass Latency

审核编辑:汤梓红

-

amd

+关注

关注

25文章

5647浏览量

138998 -

Xilinx

+关注

关注

73文章

2192浏览量

129882 -

编码

+关注

关注

6文章

1015浏览量

56644 -

AXI

+关注

关注

1文章

143浏览量

17782

发布评论请先 登录

什么是Xilinx ZynqUltraScale+ MPSoC技术?

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

Xilinx Zynq UltraScale MPSoC可扩展电源设计

Xilinx UltraScale+ FPGA和MPSoC互连宽度的使用

Xilinx的Xa Zynq UltraScale MPSOC数据手册免费下载

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

简述MPSoC VCU调试方法和调试流程

MPSoC VCU调试方法和调试流程

MPSoC VCU Ctrl-SW 2020.2编码不同Stride的YUV文件

AMD-Xilinx MPSoC的Watchdog在Linux中使用的简明教程

适用于Xilinx Zynq UltraScale+ MPSoC应用的电源参考设计

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件

AMD Xilinx MPSoC VCU使用要点

AMD Xilinx MPSoC VCU使用要点

评论