在电子工程师的日常工作中,A/D转换器是实现模拟信号数字化的关键组件。今天,我们将深入探讨德州仪器(TI)的ADC10321,这是一款10位、20MSPS、低功耗的A/D转换器,具有内部采样保持功能,广泛应用于数字视频通信、医疗成像等多个领域。

文件下载:adc10321.pdf

一、ADC10321概述

ADC10321是一款低功耗、高性能的CMOS A/D转换器,能够以高达25Msps的采样率将信号数字化为10位分辨率,典型功耗仅为98mW,采用单5V电源供电。其独特的两级架构在10MHz输入信号和20MHz时钟频率下可实现9.2有效位,输出格式为直接二进制编码。

1.1 特性亮点

- 内部采样保持:内置采样保持放大器(SHA),降低输入电容,减少外部组件需求,提升动态性能。

- 单+5V供电:简化电源设计,降低系统复杂度。

- 低功耗待机模式:通过拉高PD(Power Down)引脚,可使转换器进入低功耗待机状态,典型功耗小于4mW。

- 无失码保证:在整个工作温度范围内确保无失码,保证转换精度。

- 逻辑兼容性:TTL/CMOS或3V逻辑输入/输出兼容,方便与不同系统接口。

1.2 应用领域

- 数字视频通信:满足高速视频信号的数字化需求。

- 医疗成像:为医疗设备提供高精度的信号转换。

- 文档扫描、CCD成像等:广泛应用于图像采集和处理系统。

二、关键规格参数

| 参数 | 数值 |

|---|---|

| 分辨率 | 10位 |

| 转换速率 | 20Msps |

| ENOB@10MHz输入 | 9.2位(典型值) |

| DNL | ±0.35 LSB(典型值) |

| 转换延迟 | 2个时钟周期 |

| PSRR | 56dB |

| 功耗 | 98mW(典型值) |

| 低功耗待机模式 | <4mW(典型值) |

这些参数反映了ADC10321在分辨率、速度、精度和功耗等方面的优异性能,为工程师在不同应用场景下的设计提供了有力支持。

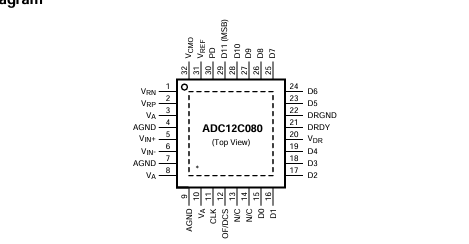

三、引脚描述与等效电路

ADC10321的引脚功能丰富,涵盖了模拟输入、参考输入、时钟输入等关键信号。以下是部分重要引脚的描述:

- VIN(引脚30):待转换的模拟输入信号,转换范围为VREF'S至VREFS。

- VREF'F(引脚31):连接到ADC参考梯形网络高端的模拟输入,电压应使VRE* S在2.3V至4.0V范围内。

- VREF'S(引脚32):用于感应ADC参考梯形网络顶部附近电压的模拟输出。

- CLK(引脚9):转换器的数字时钟输入,Vin在CLK输入的下降沿采样。

了解这些引脚的功能和特性,对于正确连接和使用ADC10321至关重要。

四、电气特性分析

4.1 静态特性

- INL(积分非线性):典型值为±0.45 LSB(最大值为±1.0 LSB),反映了每个代码与理想直线的偏差。

- DNL(差分非线性):典型值为±0.35 LSB(最大值为±0.85 LSB),衡量了与理想步长1 LSB的最大偏差。

- 分辨率:无失码分辨率为10位,确保了转换的准确性。

4.2 动态特性

- ENOB(有效位数):在不同输入频率下表现出色,如在10MHz输入时典型值为9.2位。

- S/(N+D)(信噪加失真比):在10MHz输入时典型值为57dB(最小值为56dB)。

- SNR(信噪比):在10MHz输入时典型值为58dB(最小值为58dB)。

- THD(总谐波失真):在10MHz输入时典型值为 - 66dB(最小值为 - 59dB)。

这些动态特性表明ADC10321在处理高频信号时具有良好的性能,能够有效抑制噪声和失真。

4.3 参考和模拟输入特性

- VIN(模拟输入范围):1.3V至4.0V。

- CIN(模拟VIN输入电容):典型值为5pF。

- IIN(输入泄漏电流):典型值为10μA。

这些特性对于选择合适的驱动电路和确保输入信号的稳定性非常重要。

五、应用设计要点

5.1 模拟输入设计

ADC10321的模拟输入由开关(传输门)和开关电容放大器组成,输入电容随时钟电平变化。为了获得最佳性能,应选择合适的驱动器件,如LMH6702,它具有低电压能力、宽带宽、低失真和最小的差分增益和差分相位。同时,要注意避免数字噪声进入模拟输入电路,可采用隔离和滤波措施。

5.2 参考输入设计

参考输入对于保证ADC的精度至关重要。在设计参考电路时,要考虑热漂移和电阻容差等因素。可采用简单的参考偏置方案,但可能存在热漂移问题;也可使用更复杂的电路,如添加运算放大器来精确控制参考电压。例如,使用LMC6082可获得较低的失调电压和轨到轨能力。同时,要确保参考引脚的电压在规定范围内,并能提供足够的电流。

5.3 电源供应考虑

A/D转换器需要足够的旁路电容来避免瞬态电流对电源的干扰。建议在A/D电源引脚附近放置10μF至50μF的钽或铝电解电容和0.1μF的陶瓷芯片电容。同时,模拟和数字电源应使用同一电压源,但要与其他数字电路的电源分开,以减少干扰。

5.4 时钟设计

ADC10321通常能在1MHz至25MHz的时钟频率下工作,最佳性能要求时钟上升和下降时间在5ns以内。时钟信号的占空比会影响A/D转换器的性能,该器件设计为在45%至55%的占空比范围内保持性能。为了确保时钟信号的质量,时钟线应在源端进行串联端接,并采用合适的布线技术,如带状线或微带线。

5.5 布局和接地

正确的信号布线和接地技术是确保准确转换的关键。需要使用单独的模拟和数字接地平面,模拟接地平面应低阻抗且无噪声。旁路电容应尽可能靠近转换器引脚,并通过短走线连接到引脚和相应的接地平面。模拟输入应与噪声信号走线隔离,以避免杂散信号耦合到输入。

六、常见应用陷阱及解决方法

6.1 输入超出电源轨

驱动输入(模拟或数字)超出电源轨会导致故障或不稳定的操作。为了避免这种情况,所有输入不应超过电源引脚300mV。对于可能出现下冲的高速数字电路,可在数字输入串联50至100Ω的电阻。

6.2 输入过驱动

使用超出ADC10321电源范围的设备驱动输入会导致转换不准确甚至设备损坏。在设计时,要确保驱动设备的电源在ADC10321的电源范围内。

6.3 驱动高电容数据总线

驱动高电容数字数据总线会增加瞬时数字电流需求,导致动态性能下降。可采用足够的旁路电容、分离模拟和数字接地平面,必要时对数字数据输出进行缓冲,并在每个数字输出添加47Ω的串联电阻。

6.4 参考引脚驱动不足

驱动VREF+F或VREF - F引脚的设备无法提供所需电流会导致转换器输出噪声过大。要确保驱动设备能够提供足够的电流,以保持引脚电压稳定。

6.5 时钟抖动过大

使用抖动过大的时钟源会导致采样间隔变化,增加输出噪声并降低SNR性能。应选择低抖动的时钟源,简单的带RC定时的门电路通常不够。

七、总结

ADC10321以其低功耗、高性能和丰富的特性,成为众多应用领域的理想选择。在设计过程中,工程师需要充分考虑其电气特性、引脚功能和应用要点,避免常见的应用陷阱。通过合理的电路设计、布局和接地技术,能够充分发挥ADC10321的优势,实现高质量的模拟信号数字化转换。希望本文能为电子工程师在使用ADC10321进行设计时提供有益的参考。

大家在使用ADC10321的过程中遇到过哪些问题呢?又是如何解决的?欢迎在评论区分享你的经验和见解。

-

A/D转换器

+关注

关注

1文章

170浏览量

11614 -

时钟频率

+关注

关注

0文章

72浏览量

20999 -

模拟信号

+关注

关注

8文章

1225浏览量

54432 -

数字化

+关注

关注

8文章

10370浏览量

66666

发布评论请先 登录

ADC10321,pdf datasheet (10-Bit

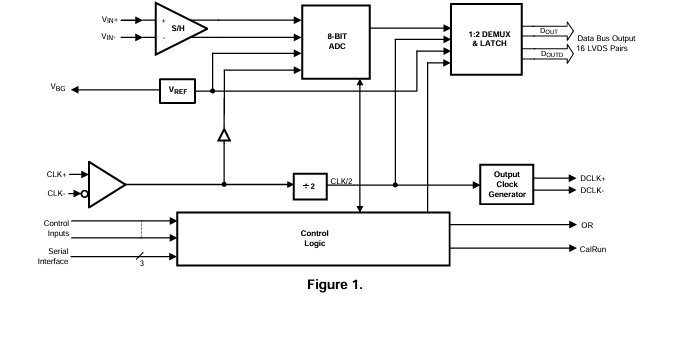

深入剖析ADC08500:高性能8位500 MSPS A/D转换器的设计与应用

深入剖析ADC12DL080:高性能12位A/D转换器的设计与应用

深入剖析ADC121S625:高性能12位A/D转换器的卓越之选

深入剖析ADC12010:12位、10 MSPS A/D转换器的卓越性能与应用指南

深入剖析ADC10D040:高性能10位A/D转换器的技术解析

深入剖析ADC10321:高性能10位A/D转换器的设计与应用

深入剖析ADC10321:高性能10位A/D转换器的设计与应用

评论