【博主简介】本人“爱在七夕时”,系一名半导体行业质量管理从业者,旨在业余时间不定期的分享半导体行业中的:产品质量、失效分析、可靠性分析和产品基础应用等相关知识。常言:真知不问出处,所分享的内容如有雷同或是不当之处,还请大家海涵。当前在各网络平台上均以此昵称为ID跟大家一起交流学习!

随着电子技术在工业、交通、消费、医疗等领域的蓬勃发展,当代社会对电力电子设备的要求也越来越高,功率半导体就是影响这些电力电子设备成本和效率的直接因素之一。自从二十世纪五十年代真空管被固态器件代替以来,以硅(Si)材料为主的功率半导体器件就一直扮演着重要的角色,功率MOSFET是其中最典型的代表。

MOSFET的中文全称是金属-氧化物半导体场效应晶体管。它的基本机构如下图所示:P型半导体作为衬底,其两端各有一个重掺杂N+,分别作为源极(SOURCE,S)和漏极(DRAIN, D),在P型半导体表面涂上一层sio2绝缘层并在绝缘层上引出一端,作为栅极(GATE, G)。

当栅源两端电压为零时,不论漏源之间的电压是正偏还是反偏,半导体中始终有反向偏置的PN结致使器件无法导通。当栅源两端加上一个正向电压且VGS上升到阈值时,P区形成一个反型层,为栅极和漏极之间创造了通路,此时MOS管导通。

为了增加MOS的耐压能力,常在P区和漏极的N+之间增加一段漂移区,承受器件在反向耐压状态下的高电压。漂移区的掺杂浓度也决定了器件的大部分电阻,此即为LDMOS的基本结构。

除了横向结构以外,还存在一种纵向结构模式,称为VDMOS。在VDMOS结构中,漏端和源端、栅端不在同一平面(如下图所示)。但与LDMOS相同的是,VDMOS的耐压和导通电阻同样主要由漂移区决定。所以提高漂移区掺杂浓度自然成为降低功率MOS导通电阻的方法之一。

在这样的背景下,为了得到大功率低损耗的功率器件,有学者提出,可以通过设置交替的PN条来提高器件漂移区的掺杂浓度进而实现低导通电阻,此即SUPER JUNCTION MOSFET(SJ MOS)。所以以下就是今天我要跟大家分享的关于半导体超结MOSFET及其发展的相关知识,希望有兴趣的朋友可以一起多交流学习。

一、超结MOSFET的定义

半导体超级结 MOSFET (SJ-MOS),英文名称:Super Junction MOSFET。为了解决额定电压提高而导通电阻增加的问题,超结结构MOSFET在D端和S端排列多个垂直pn结的结构,其结果是在保持高电压的同时实现了低导通电阻。超级结的存在大大突破了硅的理论极限,而且额定电压越高,导通电阻的下降越明显。

以下图为例,超结在S端和D端增加了长长的柱子,形成垂直的PN结,交替排列。N层和P层在漂移层中设置垂直沟槽,当施加电压时耗尽层水平扩展,很快合并形成与沟槽深度相等的耗尽层。耗尽层仅扩展至沟槽间距的一半,因此形成厚度等于沟槽深度的耗尽层。耗尽层的膨胀小且良好,允许漂移层杂质浓度增加约5倍,从而可以降低RDS(ON)。

超级结的性能提升方法:使沟槽和沟槽间距尽可能小和深。SJ-MOS 可以设计为具有较低电阻的 N 层,从而实现低导通电阻产品。

超级结存在的问题:本质上超级结MOSFET比平面MOSFET具有更大的pn结面积,因此trr比平面MOSFET快,但更大的irr流动。内部二极管的反向电流irr和反向恢复时间trr会影响晶体管关断开关特性。

二、超结MOSFET的结构

高压的功率MOSFET的外延层对总的导通电阻起主导作用,要想保证高压的功率MOSFET具有足够的击穿电压,同时,降低导通电阻,最直观的方法就是:在器件关断时,让低掺杂的外延层保证要求的耐压等级,同时,在器件导通时,形成一个高掺杂N+区,作为功率MOSFET导通时的电流通路,也就是将反向阻断电压与导通电阻功能分开,分别设计在不同的区域,就可以实现上述的要求。

基于超结SuperJunction的内建横向电场的高压功率MOSFET就是基本这种想法设计出的一种新型器件。内建横向电场的高压MOSFET的剖面结构及高阻断电压低导通电阻的示意图如图3所示。Infineon最先将这种结构生产出来,并为这种结构的MOSFET设计了一种商标CoolMOS,这种结构从学术上来说,通常称为超结型功率MOSFET。

垂直导电N+区夹在两边的P区中间,当MOS关断时,形成两个反向偏置的PN结:P和垂直导电N+、P+和外延epi层N-。栅极下面的的P区不能形成反型层产生导电沟道,P和垂直导电N+形成PN结反向偏置,PN结耗尽层增大,并建立横向水平电场;同时,P+和外延层N-形成PN结也是反向偏置形,产生宽的耗尽层,并建立垂直电场。

由于垂直导电N+区掺杂浓度高于外延区N-的掺杂浓度,而且垂直导电N+区两边都产生横向水平电场,这样垂直导电的N+区整个区域基本上全部都变成耗尽层,即由N+变为N-,这样的耗尽层具有非常高的纵向的阻断电压,因此,器件的耐压就取决于高掺杂P+区与低掺杂外延层N-区的耐压。

当MOS导通时,栅极和源极的电场将栅极下的P区反型,在栅极下面的P区产生N型导电沟道,同时,源极区的电子通过导电沟道进入垂直的N+区,中和N+区的正电荷空穴,从而恢复被耗尽的N+型特性,因此导电沟道形成,垂直N+区掺杂浓度高,具有较低的电阻率,因此导通电阻低。

比较平面结构和沟槽结构的功率MOSFET,可以发现,超结型结构实际是综合了平面型和沟槽型结构两者的特点,是在平面型结构中开一个低阻抗电流通路的沟槽,因此具有平面型结构的高耐压和沟槽型结构低电阻的特性。

内建横向电场的高压超结型结构与平面型结构相比较,同样面积的硅片可以设计更低的导通电阻,因此具有更大的额定电流值和雪崩能量。

由于要开出N+沟槽,它的生产工艺比较复杂,目前N+沟槽主要有两种方法直接制作:通过一层一层的外延生长得到N+沟槽和直接开沟槽。前者工艺相对的容易控制,但工艺的程序多,成本高;后者成本低,但不容易保证沟槽内性能的一致性。

三、超结MOSFET的工作原理

1、关断状态

从下图中可以看到,垂直导电N+区夹在两边的P区中间,当MOS关断时,也就是G极的电压为0时,横向形成两个反向偏置的PN结:P和垂直导电N+、P+和外延epi层N-。

栅极下面的的P区不能形成反型层产生导电沟道,左边P和中间垂直导电N+形成PN结反向偏置,右边P和中间垂直导电N+形成PN结反向偏置,PN结耗尽层增大,并建立横向水平电场。

当中间的N+的渗杂浓度和宽度控制得合适,就可以将中间的N+完全耗尽,如下图b所示,这样在中间的N+就没有自由电荷,相当于本征半导体,中间的横向电场极高,只有外部电压大于内部的横向电场,才能将此区域击穿,所以,这个区域的耐压极高,远大于外延层的耐压,功率MOSFET管的耐压主要由外延层来决定。

注意到,P+和外延层N-形成PN结也是反向偏置形,有利于产生更宽的耗尽层,增加垂直电场。

2、开通状态

当G极加上驱动电压时,在G极的表面将积累正电荷,同时,吸引P区的电子到表面,将P区表面空穴中和,在栅极下面形成耗尽层,如图5示。

随着G极的电压提高,栅极表面正电荷增强,进一步吸引P区电子到表面,这样,在G极下面的P型的沟道区中,积累负电荷,形成N型的反型层,同时,由于更多负电荷在P型表面积累,一些负电荷将扩散进入原来完全耗尽的垂直的 N+,横向的耗尽层越来越减小,横向的电场也越来越小。

G极的电压进一步提高,P区更宽范围形成N型的反型层,最后,N+区域回到原来的高渗杂的状态,这样,就形成的低导通电阻的电流路径,如下图所示。

四、传统MOS管的瓶颈

下面,我就跟大家分享一下传统MOS管的瓶颈:

五、超结MOSFET的缺点和改进

当然,超结理论在现实应用中也并不是完美的,那具体有哪些缺点和可以改善的地方呢?

六、超结MOSFET的优点

超结MOSFET与传统的VDMOS相比,具有导通电阻低、开关速度快、芯片体积小、发热低的特点。一般来说,相同电流、电压规格的超结MOSFET导通电阻仅为传统VDMOS的一半左右,器件开通和关断速度较传统VDMOS下降30%以上。这些特点可以使超结MOSFET在替代传统VDMOS时具有更好的温升和效率表现,一般来说,使用超结MOSFET后,电源效率可以上升1~2百分点。同时超结MOSFET也完全可以与驱动IC一起进行集成封装,大幅度降低产品体积。

超级结具有更小的结电容,对超级结器件而言,电阻的减小会带来明显的好处,例如在相同RDS(on)下的更低导通损耗或更小管芯。另外,芯片面积的减小会导致更低的结电容以及栅极和输出电荷,这可减小动态损耗。在低压沟槽式或平面式MOS管中,通常需要考虑以更高结电容为让步条件来降低RDS(on)。在超级结技术情况下,让步程度是最小的。电荷平衡机制可同时减小RDS(on)和器件结电容,使之成为一种双赢解决方案。

七、超结MOSFET的主要作用

1、降低导通电阻

相较于传统VDMOS,相同电流、电压规格的超结MOSFET的导通电阻仅为传统VDMOS的一半左右。这得益于其特殊的芯片内部结构设计,使得在相同的芯片面积下,超结MOS的内阻更低。

2、提高开关速度

超结MOSFET的开通和关断速度较传统VDMOS快30%以上,这有助于降低动态损耗,提高电源系统的效率。

3、减小芯片体积

由于超结MOS的内阻低,可以在保证性能的同时减小芯片面积,从而有利于设计更小体积的电源电路,降低产品成本。

4、降低发热

较低的导通电阻和开关速度意味着更低的损耗,进而减少了发热量,这对于对温度要求高的产品如充电头等尤为重要。

5、提升效率

使用超结MOSFET后,电源效率可以上升1~2个百分点,这对于提高整体能源利用效率具有重要意义。

6、易于集成封装

超结MOSFET可以与驱动IC一起进行集成封装,进一步降低产品体积和成本。

7、适用领域广泛

超结MOSFET以其优异的性能被广泛应用于电源、电机

写在最后面的话

超结MOS作为一种创新的半导体器件技术,通过其独特的超结结构设计,在降低导通电阻、提高开关速度、减小芯片体积、降低发热和提升效率等方面展现出显著优势。这些特点使得超结MOS在高压、高频、高效率的电力电子应用中具有广阔的前景。

免责声明

【我们尊重原创,也注重分享。文中的文字、图片版权归原作者所有,转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时私信联系,我们将第一时间跟踪核实并作处理,谢谢!】

审核编辑 黄宇

-

MOSFET

+关注

关注

150文章

9428浏览量

229678 -

半导体

+关注

关注

336文章

29991浏览量

258389

发布评论请先 登录

功率半导体“超结MOS”基础知识的详解;

龙腾半导体650V 99mΩ超结MOSFET重磅发布

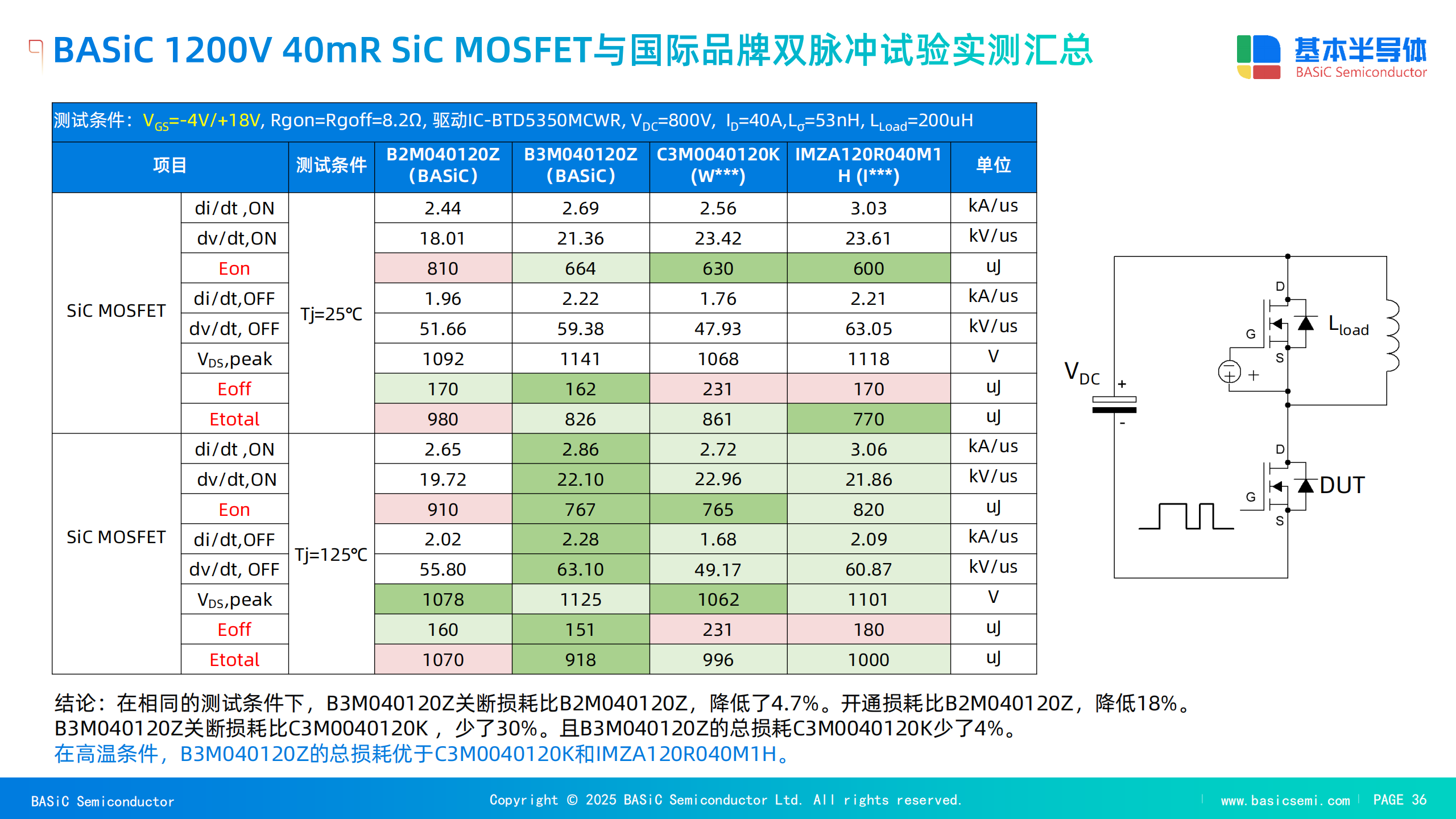

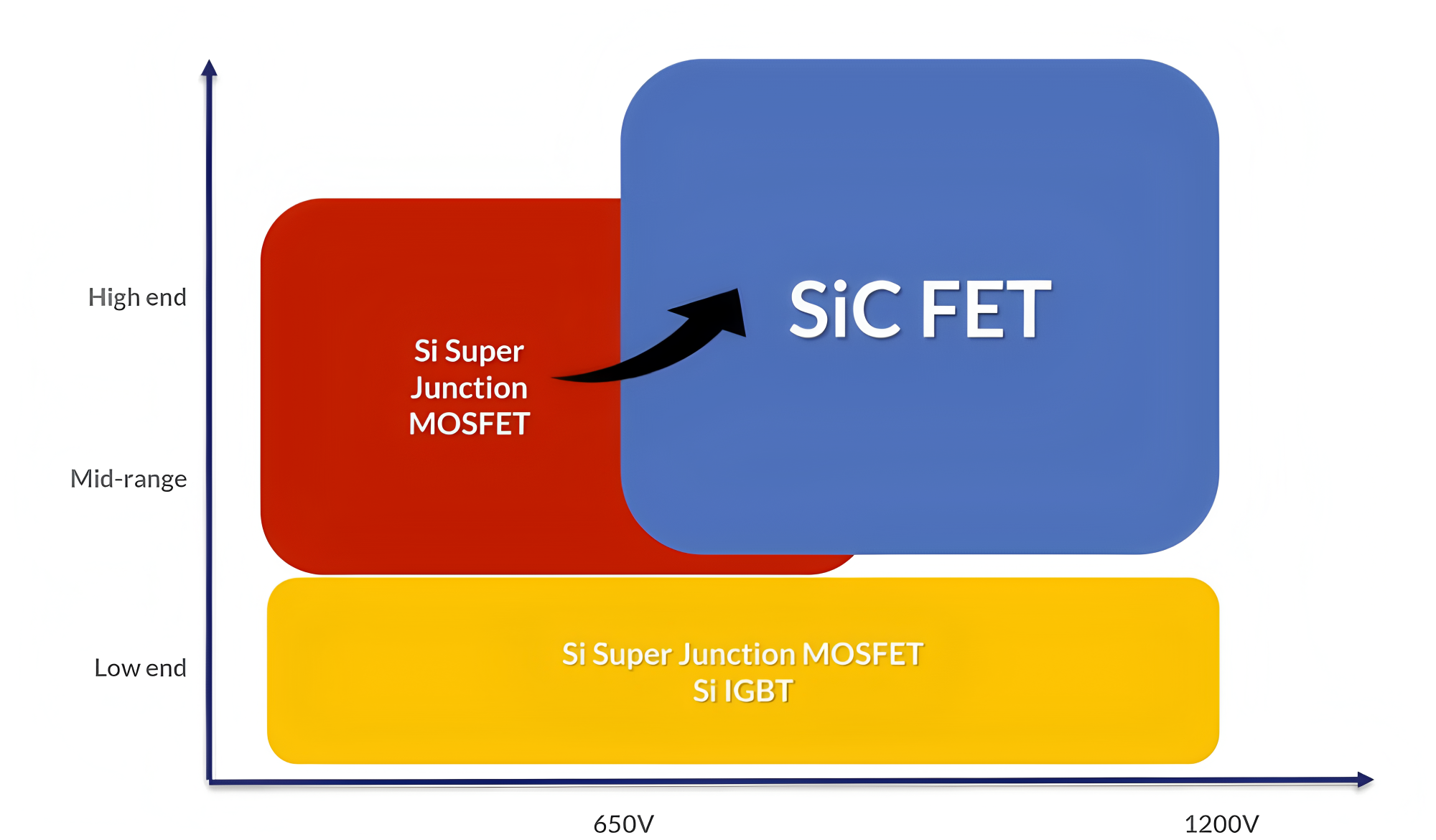

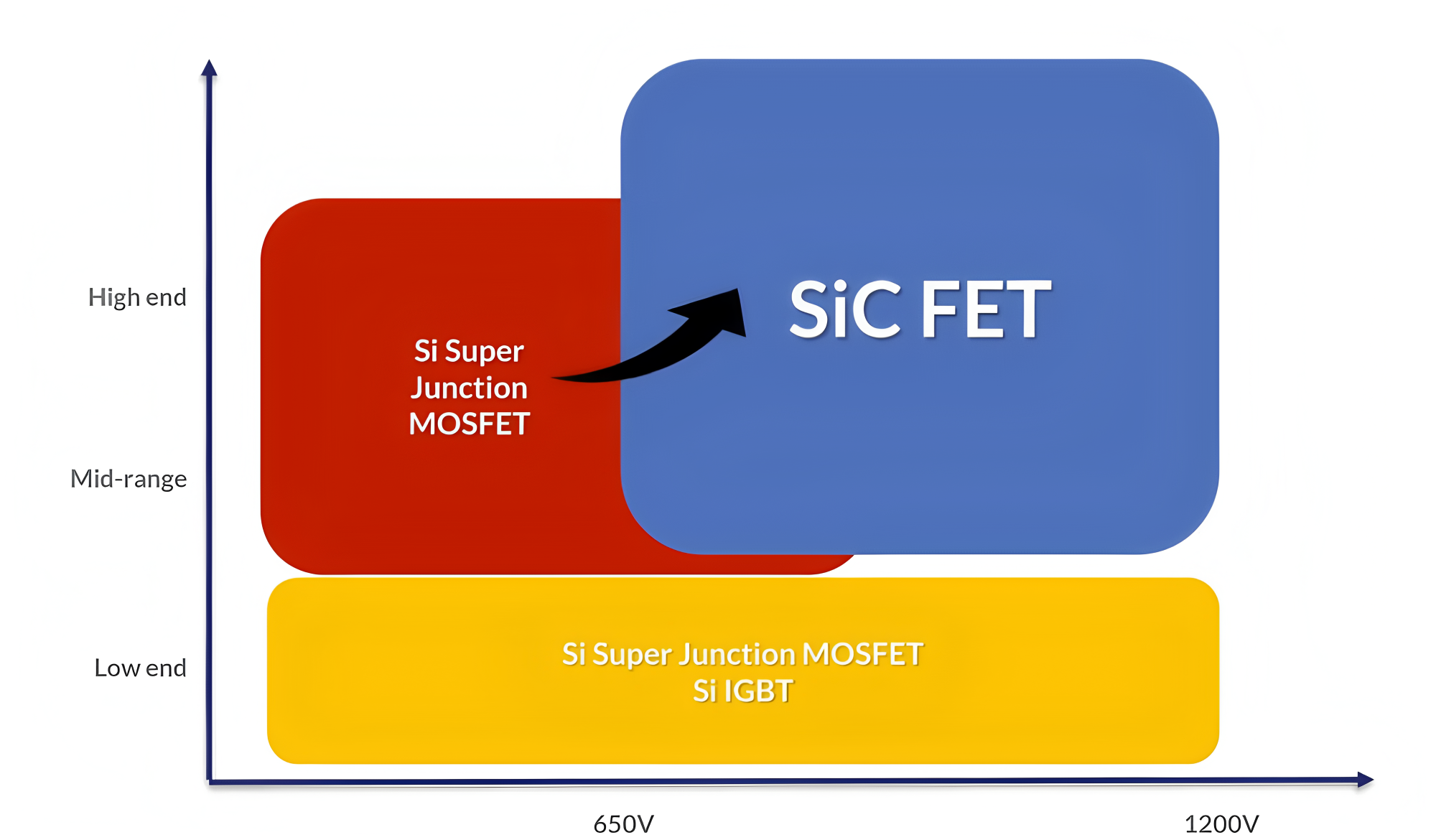

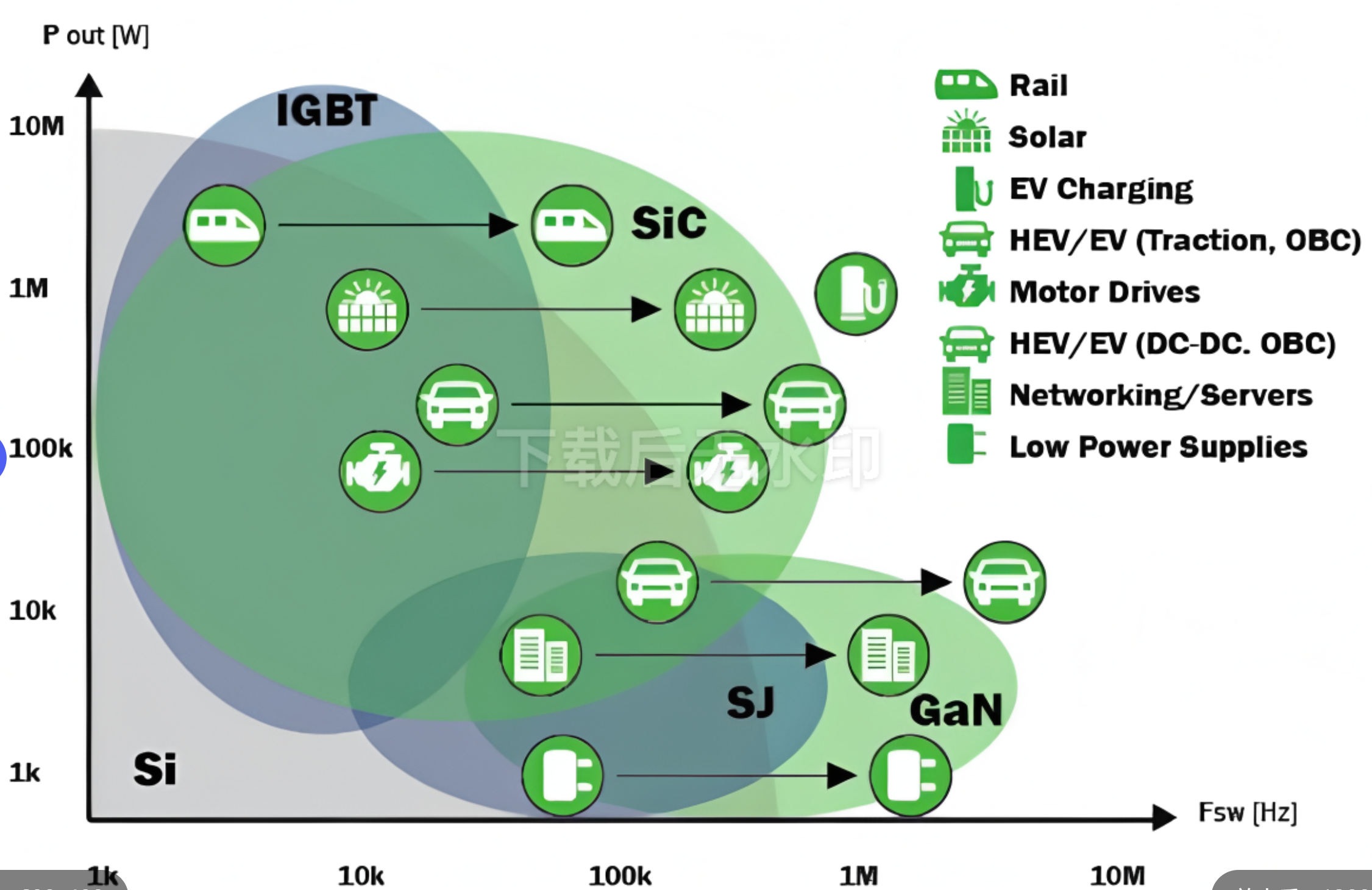

SiC碳化硅MOSFET在LLC应用中取代超结MOSFET的优势和逻辑

现代集成电路半导体器件

浮思特 | 一文读懂何为超结MOSFET (Super Junction MOSFET)

基本半导体碳化硅 MOSFET 的 Eoff 特性及其在电力电子领域的应用

瑞能半导体第三代超结MOSFET技术解析(1)

伯恩半导体新品推荐 | 超结MOS管在TV电视上的应用

新洁能Gen.4超结MOSFET 800V和900V产品介绍

从陈星弼院士无奈卖出超结MOSFET专利到碳化硅功率半导体中国龙崛起

超结MOSFET升级至650V碳化硅MOSFET的根本驱动力分析

关于半导体“超结MOSFET”及其发展的详解;

关于半导体“超结MOSFET”及其发展的详解;

评论