在电子设计领域,高速、高效的模拟 - 数字转换器(ADC)至关重要。TI的ADC08B200就是这样一款高性能的8位、200 MSPS A/D转换器,它集成了捕获缓冲器,适用于多种高速数据采集应用。今天,我们就来深入探讨这款芯片的特性、应用以及设计要点。

文件下载:adc08b200-q1.pdf

芯片特性概述

高性能核心

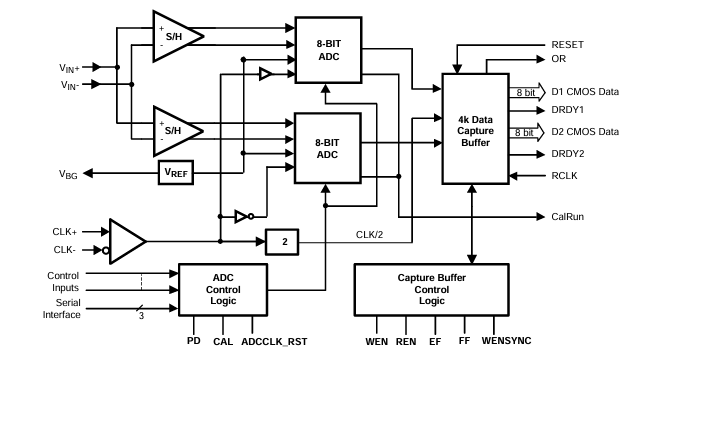

ADC08B200基于成熟的ADC08200架构,采用8位、200 MSPS的A/D核心,集成了跟踪保持电路,优化了低功耗设计。它的输入为单端输入,并且捕获缓冲器的大小可选择,最大可达1024字节,这使得它能够快速捕获输入信号,并以较慢的速率读出数据。

丰富的功能特性

- 时钟PLL电路:片上时钟PLL电路可实现时钟速率倍增,提供高速采样时钟。

- 参考梯级访问:参考梯级的顶部和底部可访问,为输入信号提供了更广泛的可能性。

- 线性功率缩放:功率消耗与采样率呈线性关系,有效控制功耗。

- FPGA训练模式:支持FPGA训练模式,方便系统集成。

- 汽车级认证:ADC08B200Q符合AEC - Q100 2级标准,适用于汽车电子应用。

应用领域

ADC08B200具有抗闩锁特性,输出具有短路保护功能,数字输出与TTL/CMOS兼容,适用于多种应用场景,如激光测距、雷达系统和脉冲捕获等。

关键规格参数

| 参数 | 详情 |

|---|---|

| 分辨率 | 8位 |

| 最大采样频率 | 200 MSPS(最小) |

| 差分非线性(DNL) | ±0.4 LSB(典型) |

| 有效位数(ENOB) | 7.2位(典型,$f_{IN}=49 MHz$) |

| 总谐波失真(THD) | -53 dBc(典型,$f_{IN}=49 MHz$) |

| 功耗 - 工作(50 MHz输入) | 2 mW / Msps(典型) |

| 功耗 - 掉电模式 | 2.15 mW(典型) |

引脚配置与功能

引脚配置

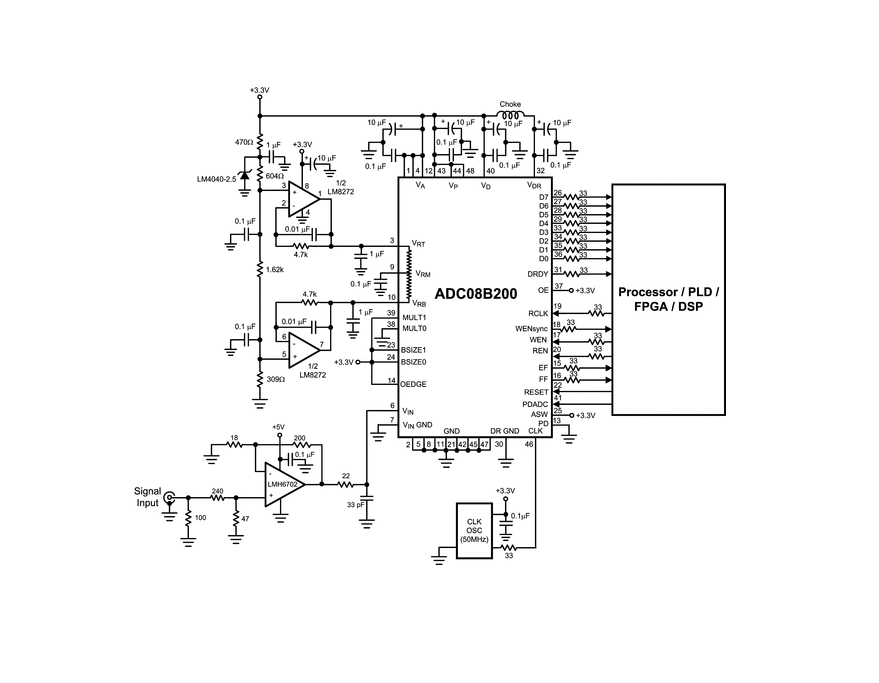

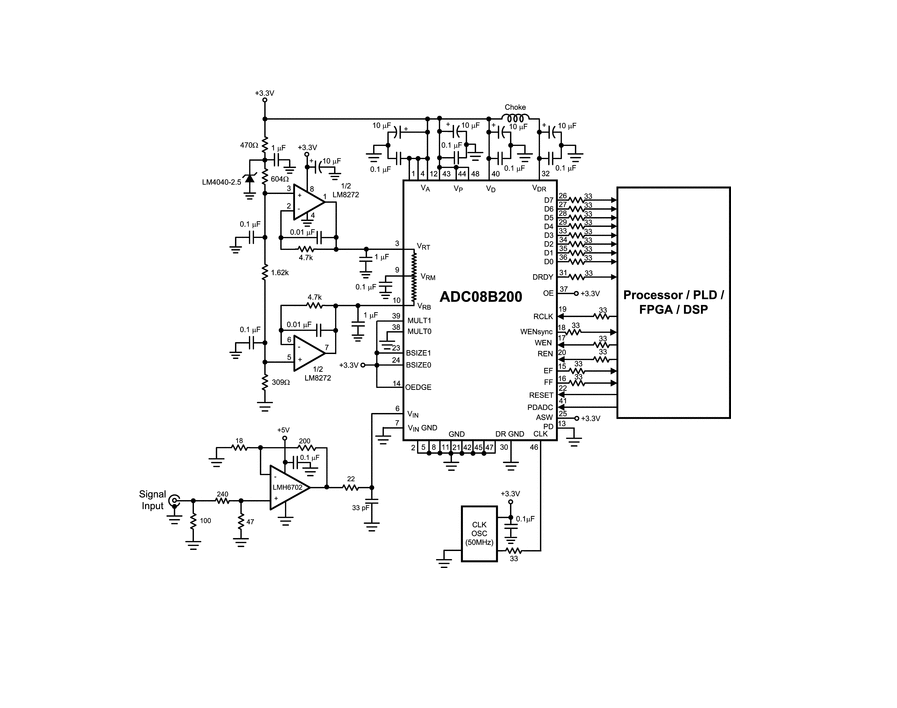

ADC08B200采用48引脚塑料封装(TQFP),引脚配置涵盖了模拟输入、参考输入、电源、时钟、控制和数字输出等多种功能。

引脚功能详解

- 模拟输入与参考引脚:$VIN$为模拟信号输入,转换范围由$VRT$和$VRB$定义;$VRT$和$VRB$分别为参考梯级的高端和低端输入,$VRM$为参考梯级的中点输入。

- 电源与掉电引脚:$PD$为芯片掉电输入,$PDADC$为ADC掉电输入,可实现不同级别的功耗控制。

- 时钟与控制引脚:$CLK$为数字时钟输入,$RCLK$为缓冲器读取时钟输入,$WEN$为写使能输入,$REN$为读使能输入,$RESET$为设备复位输入,$OE$为输出使能输入。

- 状态标志引脚:$FF$为缓冲器满标志,$EF$为缓冲器空标志,$DRDY$为数据准备好输出,$WENSYNC$为同步写使能输出。

电气特性与性能

直流精度

ADC08B200在直流精度方面表现出色,积分非线性(INL)最大为±1.3 LSB,差分非线性(DNL)最大为±0.9 LSB,无丢失码。

模拟输入与参考特性

输入电压范围为$VRB$到$VRT$,输入电容在时钟低电平时为3 pF,高电平时为4 pF,模拟输入电阻大于1 MΩ,全功率带宽为500 MHz。

数字输入特性

逻辑高输入电压($VIH$)和逻辑低输入电压($VIL$)在不同引脚有不同的要求,以确保正确的逻辑电平识别。

电源特性

不同电源的电流消耗在不同输入条件下有所不同,如模拟电源电流($IA$)在直流输入时为72.5 mA,$f_{IN}=50 MHz$时为76.8 mA(最大88.3 mA)。

谐波与失真特性

在不同输入频率和幅度下,ADC08B200的总谐波失真(THD)和互调失真(IMD)表现良好,如在$f_{IN}=49 MHz$,$VIN=FS - 0.25 dB$时,THD为 - 63 dBc。

时钟与定时特性

时钟选项

ADC08B200的PLL可实现时钟倍增,用户可根据需要选择不同的时钟倍增因子,也可选择旁路PLL。

定时特性

时钟的最大和最小输入速率、高低电平时间等都有严格的要求,以确保ADC的正常工作。例如,最小$CLK$低电平时间和高电平时间均为1.7 ns(最小)。

功能描述与操作模式

数据采集与处理

数据在采样时钟的上升沿采集,在缓冲器旁路模式下,数字数据在6个时钟周期加$t_{OD}$后在输出引脚可用。当缓冲器启用时,转换后的数据写入缓冲器,并可通过$RCLK$信号读出。

缓冲器控制

缓冲器的读写操作由$WEN$和$REN$控制,且不能同时进行。缓冲器有满标志($FF$)和空标志($EF$),可用于管理缓冲器的状态。

操作模式

ADC08B200有多种操作模式,包括关机模式、缓冲器活动 - ADC关机模式、数据读取模式和数据捕获模式等,可通过不同的引脚组合实现。

应用设计要点

参考输入设计

参考输入$VRT$和$VRB$的电压应在规定范围内,外部驱动设备应能提供足够的电流。可采用低阻抗源驱动参考引脚,以提高参考电压的精度。

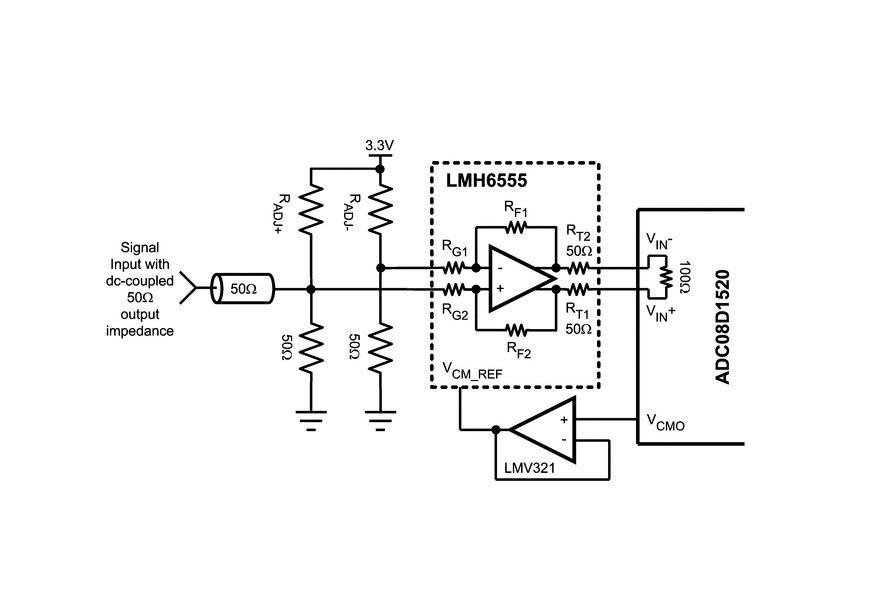

模拟输入设计

模拟输入为开关加积分器结构,输入电容随时钟电平变化。为减少输入电压尖峰对驱动放大器的影响,可在放大器和ADC输入之间使用单极RC滤波器。

电源设计

电源设计至关重要,每个电源引脚应使用适当的旁路电容,以降低电源噪声。建议使用相邻的电源和接地平面,以降低电源分配系统的阻抗。

时钟设计

时钟信号应尽量短且远离其他信号,以减少时钟抖动。时钟输入线应根据长度进行适当的终端匹配,以确保信号完整性。

常见应用陷阱与解决方法

- 输入电压超出范围:所有输入电压不应超过电源引脚电压±300 mV,可在数字输入串联47Ω电阻解决过冲问题。

- 驱动高电容数据总线:输出驱动电容过大可能影响动态性能,可缓冲数字数据输出或在数字输出添加12Ω - 27Ω串联电阻。

- 使用不当的放大器:应选择能够快速响应输入电压尖峰的放大器,并使用单极RC滤波器确保放大器稳定性。

- 参考引脚驱动不足:确保驱动设备能为$VRT$和$VRB$提供足够的电流,以保证参考引脚的稳定性。

- 时钟信号问题:避免使用抖动过大的时钟源,保持时钟线短且远离其他信号。

总结

ADC08B200是一款功能强大、性能优越的高速8位A/D转换器。在设计应用时,我们需要充分考虑其电气特性、引脚功能、时钟与定时要求以及各种应用设计要点,以确保系统的稳定性和可靠性。希望本文能为电子工程师们在使用ADC08B200进行设计时提供有价值的参考。

你在使用ADC08B200的过程中遇到过哪些问题?又是如何解决的呢?欢迎在评论区分享你的经验和见解。

-

缓冲器

+关注

关注

6文章

2215浏览量

48680 -

adc

+关注

关注

100文章

7407浏览量

553809 -

数字转换器

+关注

关注

0文章

342浏览量

28631 -

输入信号

+关注

关注

0文章

555浏览量

13107 -

PLL电路

+关注

关注

0文章

94浏览量

7023

发布评论请先 登录

ADC08B200/ADC08B200Q,pdf datas

深入解析ADC08B3000:高性能8位3GSPS A/D转换器的技术奥秘

ADC08B200:高速8位A/D转换器的全方位解析

深入解析ADC08D500:高性能低功耗8位500 MSPS A/D转换器

ADC08B200:高速8位A/D转换器的设计与应用指南

ADC08B200:高速8位A/D转换器的设计与应用指南

评论