在电子工程师的设计领域中,A/D转换器一直是至关重要的组件。今天,我们将深入探讨TI公司的ADC14L020这款14位、20 MSPS的A/D转换器,为大家详细解析它的特性、参数、应用以及设计过程中需要注意的关键要点。

文件下载:adc14l020.pdf

一、产品概述

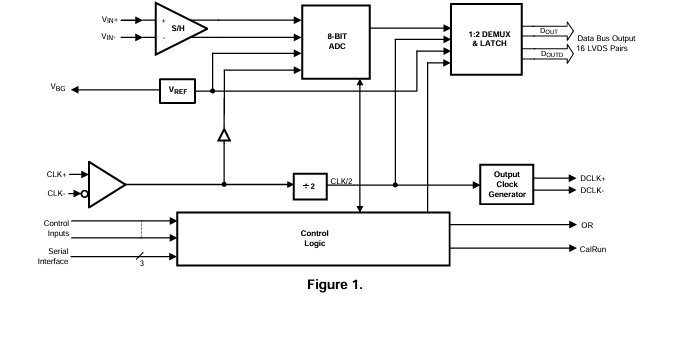

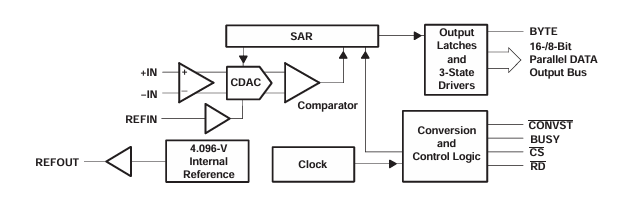

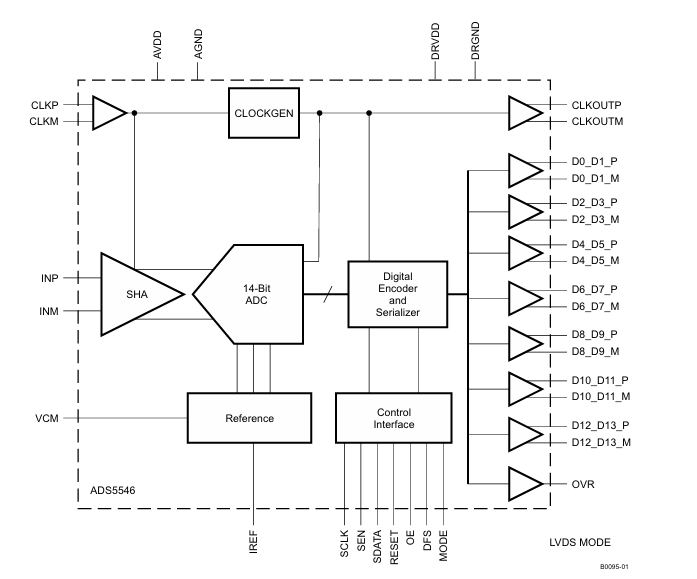

ADC14L020是一款低功耗的单芯片CMOS模拟 - 数字转换器,能够以每秒20兆采样 (MSPS) 的速率将模拟输入信号转换为14位数字字。它采用了差分流水线架构,并配备数字误差校正和片上采样保持电路,在降低功耗的同时,还能提供出色的动态性能和150 MHz的全功率带宽。这款转换器仅需单一的 +3.3V电源供电,在奈奎斯特频率下可实现12.0的有效位数,在20 MSPS的采样率下功耗仅为150 mW,并且具备掉电模式,可将功耗降低至15 mW。

二、产品特性

(一)电源与内部结构

- 单一电源供电:仅需 +3.3V电源,简化了电源设计。

- 内部采样保持:片上集成采样保持电路,减少了外部元件的使用。

-

内部参考输出:参考输出电压范围为2.4V至3.6V,兼容多种应用。

(二)性能优势

- 低功耗:正常工作模式下功耗为150 mW,掉电模式下仅为15 mW。

- 高分辨率:分辨率达到14位,无丢失码。

- 优秀的动态性能:SNR($f{IN}=10 MHz$)典型值为74 dB,SFDR($f{IN}=10 MHz$)典型值为93 dB。

三、关键参数

(一)静态参数

| 参数 | 典型值 | 极限值 | 单位 |

|---|---|---|---|

| 分辨率 | 14 | Bits (min) | |

| 积分非线性 (INL) | ±1.4 | ±3.8 | LSB (max) |

| 差分非线性 (DNL) | ±0.5 | ±1.0 | LSB (max) |

| 正增益误差 (PGE) | ±0.3 | - | %FS (max) |

| 负增益误差 (NGE) | ±0.3 | - | %FS (max) |

| 增益误差温度系数 (TC GE) | - | - | ppm/°C |

| 偏移误差 (VoFF) | 0.85 | - | %FS (max) |

| 偏移误差温度系数 (TC VoFF) | - | - | ppm/°C |

(二)动态参数

| 参数 | 条件 | 典型值 | 极限值 | 单位 |

|---|---|---|---|---|

| 全功率带宽 (FPBW) | 0dBFS输入,输出 -3 dB | 150 | - | MHz |

| 信噪比 (SNR) | $f_{IN}=1 MHz$ | 74 | - | dBc |

| $f_{IN}=10 MHz$ | 74 | 72.3 | dBc | |

| 无杂散动态范围 (SFDR) | $f_{IN}=1 MHz$ | 93 | - | dBc |

| $f_{IN}=10 MHz$ | 93 | 81 | dBc |

四、应用领域

ADC14L020凭借其出色的性能,广泛应用于以下领域:

五、设计要点

(一)电源设计

- 电源旁路:电源引脚需要用10 µF电容和0.1 µF陶瓷芯片电容进行旁路,且靠近每个电源引脚。优先选择无引线芯片电容,因为它们的串联电感较低。

-

电源噪声:模拟电源引脚的噪声应保持在100 mVP - P以下,以确保转换器的性能。

(二)输入设计

- 参考输入:VREF引脚可选择内部参考或提供外部参考。使用外部参考时,VREF引脚需用0.1 µF电容旁路至地。

-

模拟输入:采用差分输入时,ADC14L020性能最佳。单端输入不推荐,但在必要时,可将一个模拟输入连接到驱动输入的直流中点电压。输入信号的峰值不应超过2.6V,共模输入电压$V_{CM}$应在0.5V至2.0V范围内。

(三)时钟设计

- 时钟信号:CLK信号应使用稳定、低抖动的时钟源驱动,上升和下降时间应小于2 ns。时钟线应尽可能短,避免与其他信号线交叉。

- 时钟终止:时钟线应在源端以其特性阻抗进行端接,确保整个线路的时钟线阻抗恒定。

-

时钟占空比:ADC14L020具有占空比稳定器,可在20%至80%的时钟占空比范围内保持性能。

(四)输出设计

- 输出负载:输出负载电容应控制在15 pF/pin以内,以避免$t_{OD}$增加,影响数据锁存。

- 输出缓冲:可使用缓冲器(如74ACQ541)连接在ADC输出和其他电路之间,减少输出负载电流。

-

输出电阻:在数字输出端靠近ADC引脚处插入约33Ω的串联电阻,可隔离输出与线路和其他电路电容,限制输出电流。

(五)布局与接地

- 分区设计:电路板应保持模拟和数字区域分开,ADC14L020置于两者之间,以减少干扰。

- 接地隔离:数据输出的接地返回(DR GND)不应与ADC14L020的其他接地引脚在靠近的位置连接到系统接地。

- 信号隔离:模拟电路和数字电路应分开布局,时钟线应尽可能短,避免与其他信号线交叉。

六、常见应用误区及解决方法

(一)输入电压超出范围

输入电压不应超过电源轨100 mV,否则可能导致故障或不稳定运行。可在有问题的数字输入信号源附近串联一个47Ω至100Ω的电阻来解决。

(二)驱动高电容数字数据总线

高电容负载会导致动态性能下降和$t_{OD}$增加。可通过适当的旁路、保持模拟和数字区域分开、缓冲数字数据输出以及在数字输出端添加串联电阻来解决。

(三)使用不合适的放大器驱动模拟输入

输入电容会随时钟相位变化,需要使用能够应对动态负载的放大器。如放大器出现过冲、振铃或不稳定现象,可在放大器输出端添加小串联电阻,并在模拟输入端添加电容来改善性能。

(四)参考引脚超出范围

使用外部参考时,$V_{REF}$应在0.8V至1.2V范围内,否则可能导致性能下降。

(五)时钟源问题

时钟源的抖动、过长的时钟信号走线或其他信号耦合到时钟信号走线,会导致采样间隔变化,降低SNR和SINAD性能。应使用低抖动的时钟源,缩短时钟线长度,并避免与其他信号耦合。

七、总结

ADC14L020作为一款高性能的A/D转换器,在低功耗、高分辨率和优秀的动态性能方面表现出色。然而,在设计过程中,我们需要注意电源、输入、时钟、输出、布局和接地等多个方面的要点,避免常见的应用误区。只有这样,才能充分发挥ADC14L020的性能,为我们的设计带来更可靠、更高效的解决方案。希望本文能为电子工程师在使用ADC14L020进行设计时提供有价值的参考。

你在设计过程中是否遇到过类似A/D转换器的其他问题呢?欢迎在评论区分享你的经验和见解。

-

MSPS

+关注

关注

0文章

562浏览量

28770 -

输出电压

+关注

关注

2文章

2036浏览量

40753 -

A/D转换器

+关注

关注

1文章

142浏览量

11593 -

数字转换器

+关注

关注

0文章

331浏览量

28624 -

输入信号

+关注

关注

0文章

549浏览量

13105

发布评论请先 登录

ADC14L020数据转换器,Vrm引脚在连接滑动变阻器后,电压无法调节怎么解决?

ADC14L020,pdf datasheet (14-Bi

深入剖析ADC08500:高性能8位500 MSPS A/D转换器的设计与应用

深入剖析ADC124S101:高性能12位A/D转换器的卓越之选

剖析ADC12L080:12位高速A/D转换器的卓越性能与应用指南

深入解析ADC12020:12位、20 MSPS A/D转换器的卓越性能与应用指南

探索 ADC12D040:双 12 位、40 MSPS A/D 转换器的卓越性能与应用

深入剖析ADC14L020:14位、20 MSPS A/D转换器的卓越性能与设计要点

深入剖析ADC14L020:14位、20 MSPS A/D转换器的卓越性能与设计要点

评论