怎样把TOP面的器件、shape、via、走线一起mirror到BTO层?

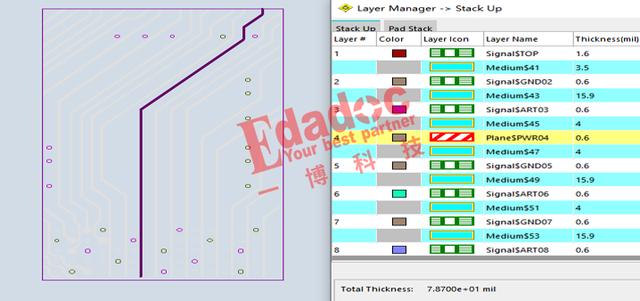

解答:用16.3以上版本可以轻松做到将需要mirror的部分建成一个模块复用文件,然后再复用它,复用时可以在放置过程中右键选择整体mirror。

以一个中心点MIRROR器件并移到旁边(用IX多少),然后以那个中心点复制孔-右键-MIRROR GEOMRTRY再移到IX多少和器件一个距离就好了

用placement edit的模式, 然后再框选要mirror的器件之后,再点击右键选择 place replicate create 创建一个MDD文件就可以复用了

奈因科技--专注于高速高密度PCB板设计

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

BTO

+关注

关注

0文章

7浏览量

8949 -

Mirror

+关注

关注

0文章

5浏览量

9494 -

TOP

+关注

关注

0文章

37浏览量

33343

原文标题:怎样把TOP面的器件、shape、via、走线一起mirror到BTO层?

文章出处:【微信号:Line_pcblayout,微信公众号:Line_pcblayout】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

03. 如何把 PCB 板上的线变成铜皮?| 芯巧Allegro PCB 设计小诀窍

图形的描述是矢量的,而有很多软件对大块图形的描述是线性的,这就导致这类图形导入到Allegro PCB之后,图形是由一条条的线组成的,这时就需要把线构成的图形转换成

发表于 04-03 16:40

如何使用 Python 将 I2C LCD 与 VIsionFive 一起使用?

我刚刚发布了一篇关于将 I2C LCD 与 VisionFive 一起使用的新文章。你可以检查一下。

注意:这是基于 libgpiod 库,我已经在使用这个库。您可

发表于 03-30 06:52

PCB板双面布局的DDR表底走线居然不一样

的想法,所以前面的一些走线长度和阻抗的优化调整意见给到他们的时候,他们也能够接受,并且表示赞同。当我们提出最后一项优化方案后,他们就表示出了深深的不太理解了。

这

发表于 12-11 10:43

EXCUSE ME,表层的AC耦合电容和PCB内层的高速线会有串扰?

线在L3层,中间L2层是地平面的这种情况。那就回到了题目和摘要说的问题了,根据电磁场理论,电容在表层,走

发表于 12-10 10:00

PCB设计中的走线宽度与电流管理

工程师在设计的时候,很容易忽略走线宽度的问题,因为在数字设计时,走线宽度不在 考虑范围里面。通常情况下,都会尝试用最小的线宽去设计走线,这时,在大电流时,将会导致很严重的问题。下

聊聊怎么把 SAW 滤波器量“准”:VNA、S 参数和群时延那些坑

太低,容差过大

PCB 走线长、转折多,耦合严重

测试环境周边有较强干扰源

5.3 和数据手册完全对不上

可以把以下资料打包发给原厂或代理技术支持一起看:

VNA 型号、校准方式、扫频参数

测试板照片

发表于 11-19 17:38

到底DDR走线能不能参考电源层啊?

。就像下面这个3D仿真模型展示的一样。

要不。。。我们还是首先来看看如果是L3层的这根地址信号上下都是地平面的常规情况的结果吧,也就是把上面的

发表于 11-11 17:46

sc-1和sc-2可以一起用吗

SC-1和SC-2可以一起使用,但需遵循特定的顺序和工艺条件。以下是其协同应用的具体说明:分步实施的逻辑基础SC-1的核心作用:由氨水(NH₄OH)、过氧化氢(H₂O₂)和水组成,主要去除硅片表面的

技术资讯 I Allegro 设计中的走线约束设计

本文要点在进行时序等长布线操作的时候,在布线操作的时候不管你是走蛇形线还是走折线,约束管理器会自动帮你计算长度、标偏差,通过精确控制走线长度,来实现信号的时序匹配。约束设计就是

光纤能与电线一起走吗

光纤与电线在特定条件下可以一起布线,但需严格遵守安全规范和物理隔离要求,以下是详细分析: 一、光纤与电线的物理特性差异 光纤 传输介质:以光信号传输数据,不导电,因此不受电磁干扰(EMI

AD7792电流源输出在走线时,如果走线过长,且走线很细10mil,会导致电流源大小衰减吗?

AD7792电流源输出在走线时,如果走线过长,且走线很细10mil,会导致电流源大小衰减吗?

发表于 06-11 07:22

怎样把TOP面的器件、shape、via、走线一起mirror到BTO层

怎样把TOP面的器件、shape、via、走线一起mirror到BTO层

评论