倾佳电子深度解析SiC MOSFET负压关断的串扰抑制机理与-5V工作电压的技术意义——暨主流厂商关断策略横向对比

倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,并提供包括IGBT、SiC MOSFET、GaN等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

报告摘要

倾佳电子系统性地阐明,碳化硅(SiC)MOSFET的负压关断(Negative Gate Turn-off, NGT)是抑制高开关瞬态(高 $dV/dt$)下寄生导通串扰(Parasitic Turn-on Crosstalk)的决定性技术手段。然而,这一策略并非没有代价,它在系统设计中引入了关于栅极氧化物可靠性(特别是负偏压温度不稳定性,NBTI)、驱动电路复杂性和体二极管损耗的深刻权衡。

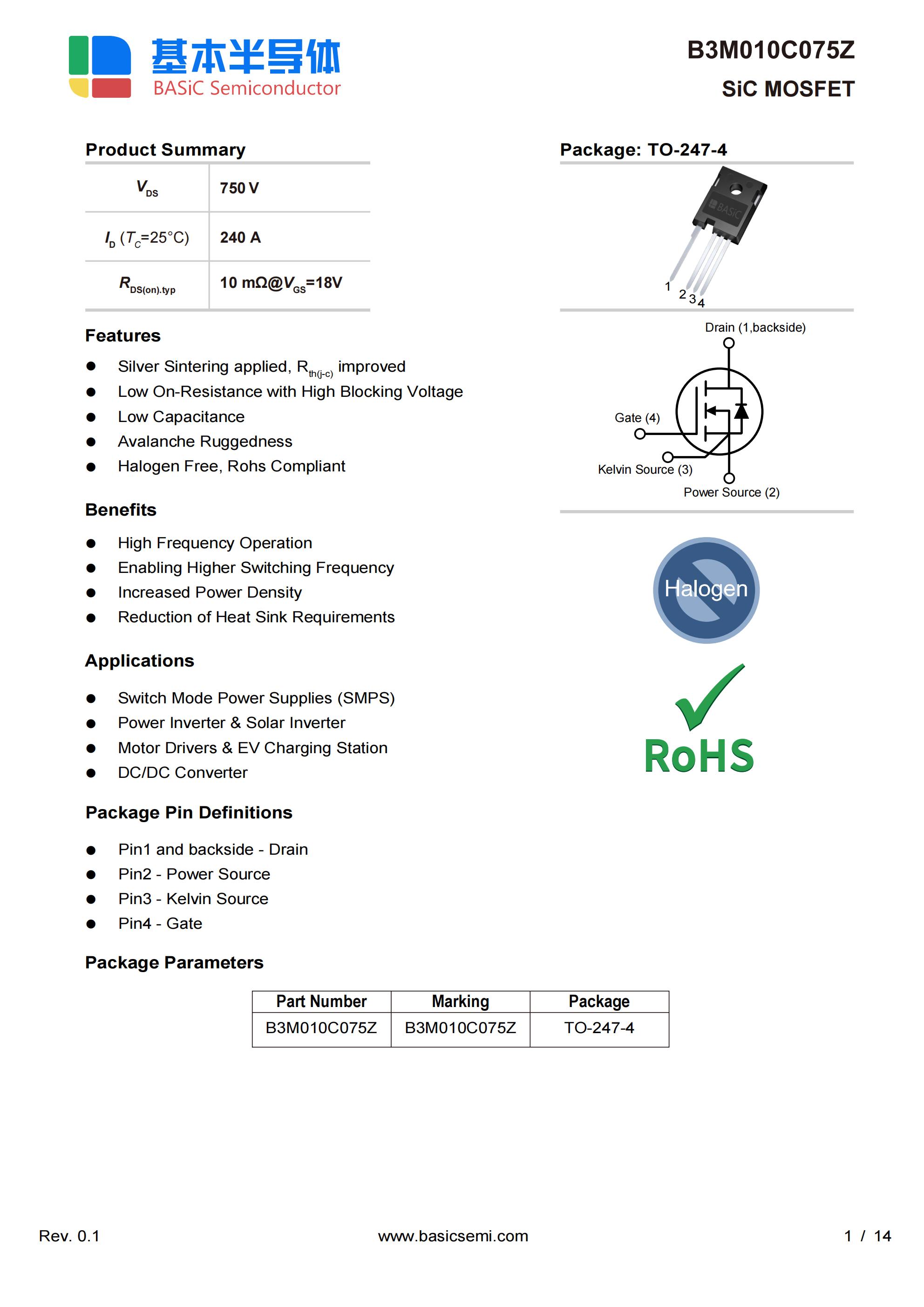

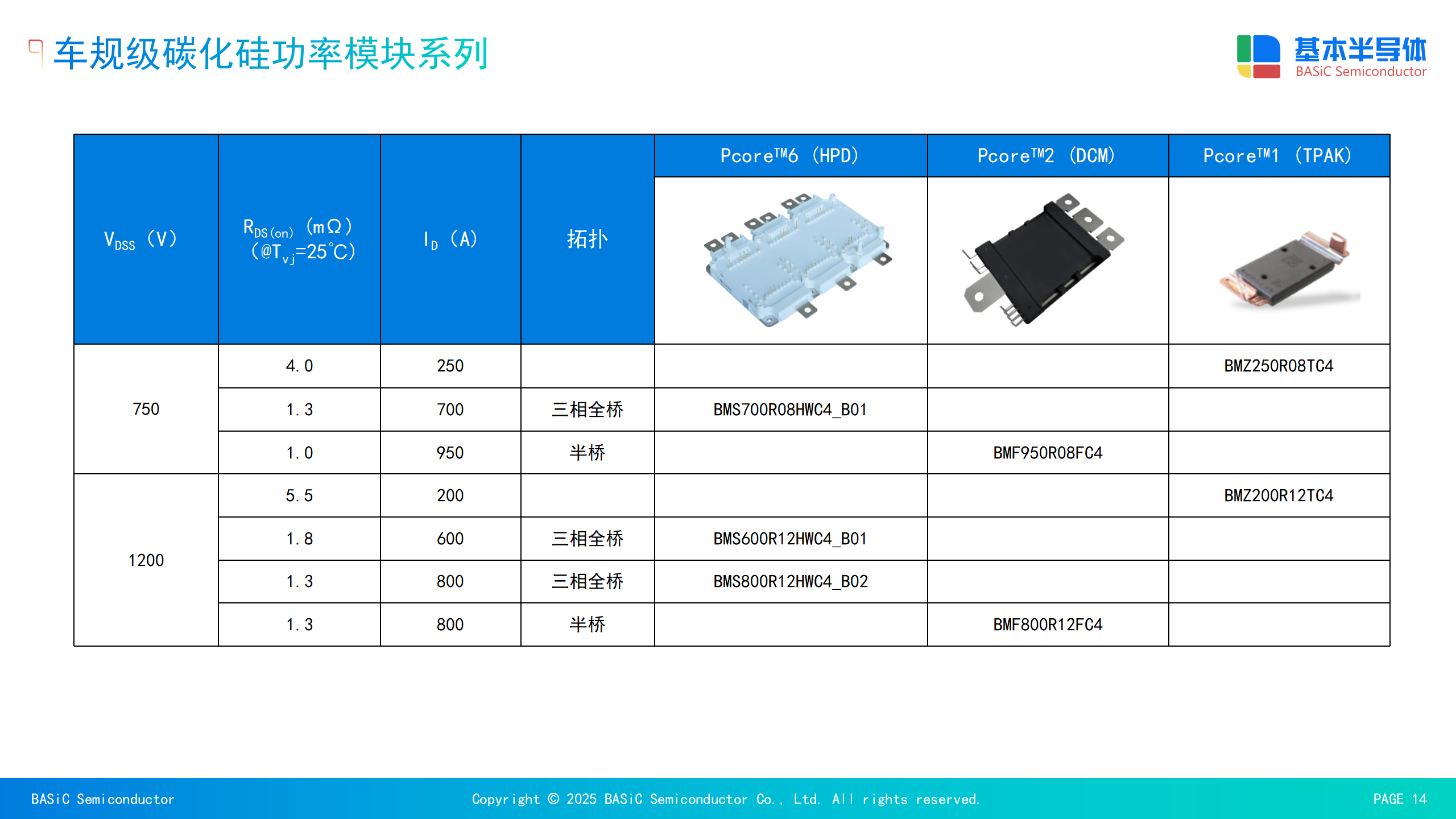

基本半导体(BASIC Semiconductor)在其第三代SiC MOSFET平台 上,明确推荐-5V的推荐工作电压($V_{GSop}$)。鉴于其器件约2.7V的典型栅极阈值电压($V_{GS(th)}$),此举是一种“稳健性优先”的战略选择。它旨在为系统提供绝对的串扰免疫裕量。其更深层的“技术意义”在于:这是一种对其栅氧工艺在长期-5V偏压下,抵抗NBTI效应挑战的可靠性自信的宣告。

倾佳电子的横向对比将揭示,当前市场主流厂商的关断策略以$V_{GS(th)}$为分界线,呈现出两大阵营:

高 $V_{GS(th)}$ 阵营 (Infineon): 凭借约4.5V以上的高阈值电压 ,正积极推动“0V关断”的简洁设计方案 。

中低 $V_{GS(th)}$ 阵营 (BASiC Semi, ONSEMI, STMicroelectronics): 凭借约2.3V至3.0V的阈值电压 ,依赖-4V至-5V的负压关断来确保严苛工况下的动态可靠性。

倾佳电子将为系统架构师在器件选型、驱动设计和可靠性评估之间进行知情决策,提供关键的物理依据和市场数据。

第一章:SiC MOSFET高dV/dt串扰的物理根源

1.1 寄生导通的“风暴三角”:$dV/dt$、米勒电容与栅极阈值

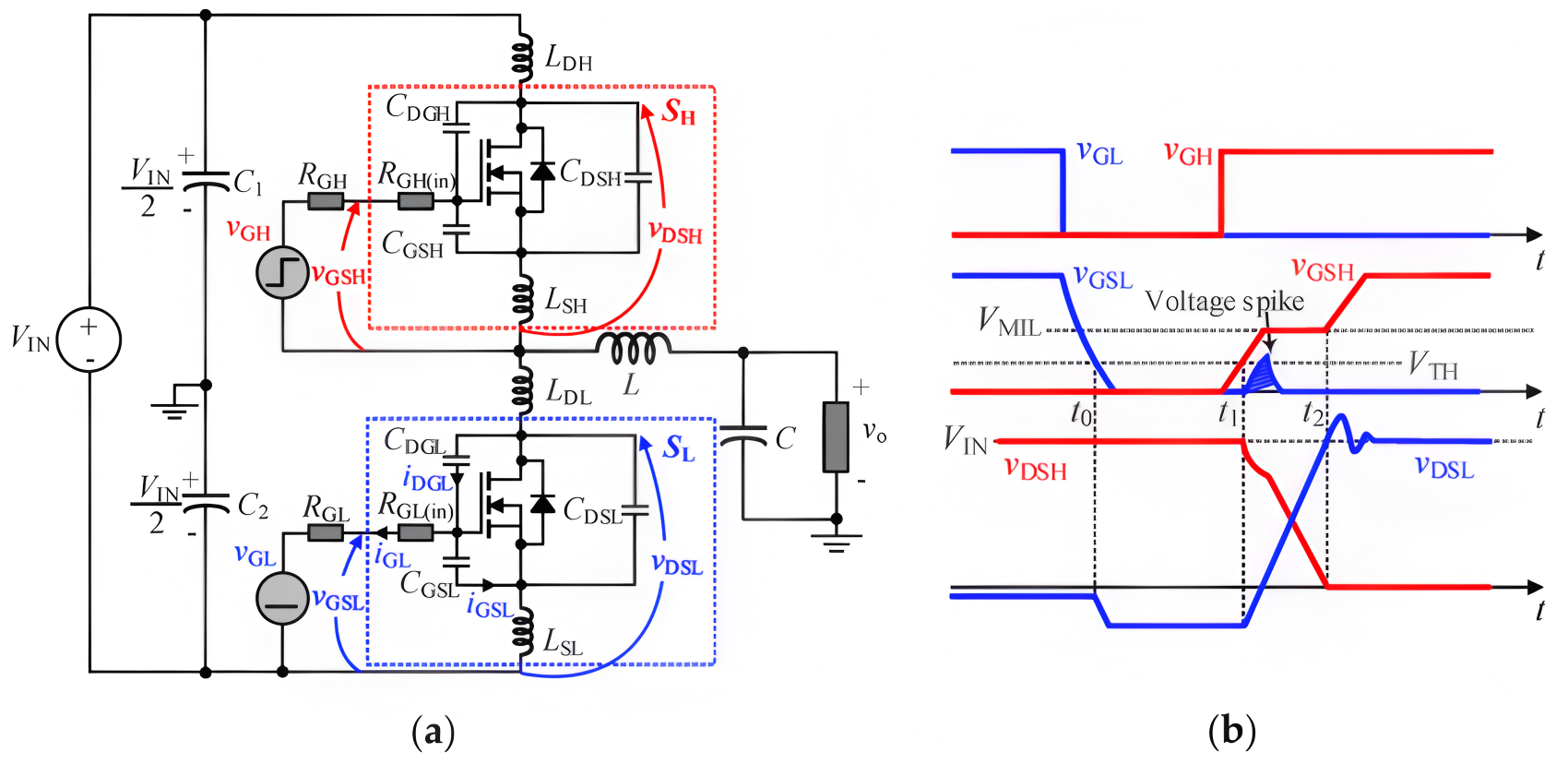

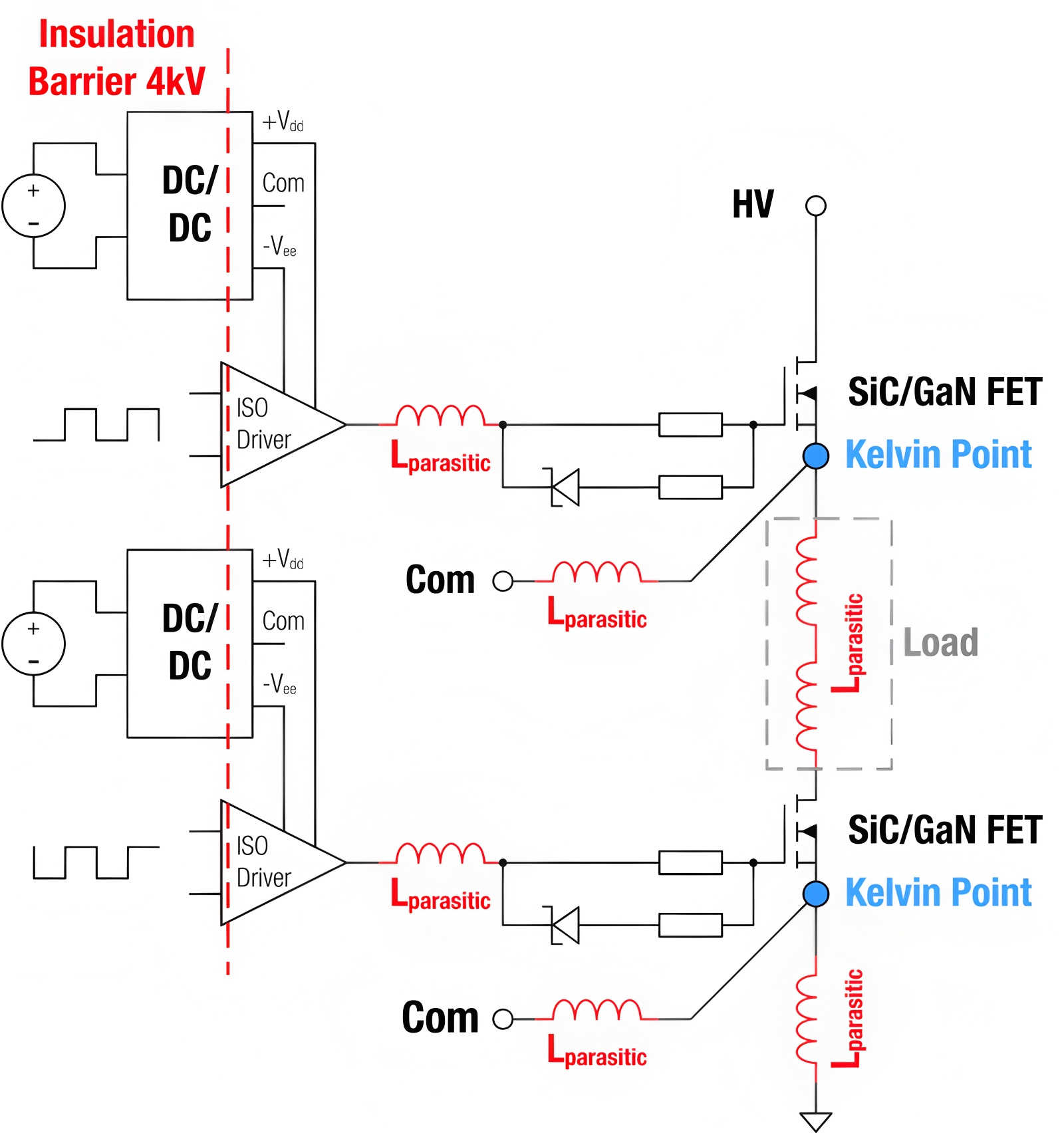

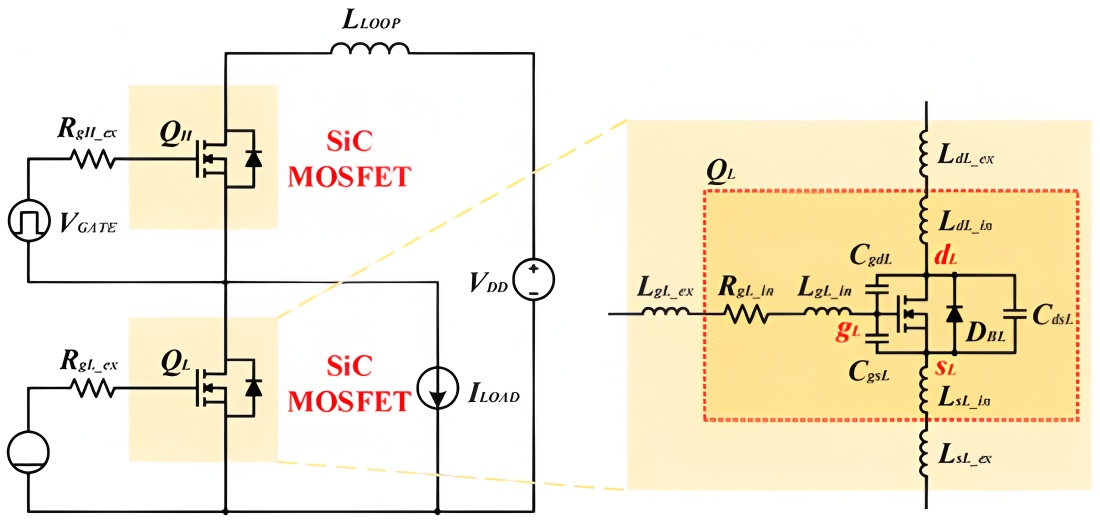

在电力电子系统中,特别是在如图腾柱(Totem-pole)或半桥(Half-bridge)的拓扑结构中,串扰是导致系统失效的关键隐患 。串扰的发生,源于器件高速开关时三个物理要素的瞬态耦合。

以一个典型的半桥下管(Low-Side, LS)S2为例,其寄生导通发生在对管(High-Side, HS)S1开通的瞬间 。此时,S2处于关断状态,但S1的开通会导致S2的漏源极电压($V_{DS}$)经历一次极高($dV/dt$)的电压爬升 12。对于SiC MOSFET,由于其极快的开关速度,这个$dV/dt$值可轻易超过 50 V/ns 甚至 100 V/ns。

这个高$dV/dt$通过S2器件内部的寄生电容,特别是栅极-漏极电容($C_{gd}$),即米勒电容($C_{rss}$),耦合到栅极 。在基本半导体的B3M010C075Z(750V)和B3M013C120Z(1200V)器件手册中,其$C_{rss}$的典型值分别为19 pF 和 14 pF 。这个瞬态电压变化率会产生一个位移电流,即米勒电流:

$$I_{Miller} = C_{gd} times frac{dV}{dt}$$

这个电流的方向是从S2的漏极(高电位)灌入栅极(低电位)。

1.2 栅极电荷的动态竞争:米勒电流($I_{Miller}$)与栅极电阻($R_G$)的放电路径

当$I_{Miller}$电流被注入S2的栅极节点时,它面临两条竞争路径 :

充电路径: 对栅源电容 $C_{gs}$(即输入电容$C_{iss}$的主要组成部分)进行充电。

放电路径: 通过栅极关断回路(包括外部栅极电阻$R_{G,ext}$、内部栅极电阻$R_{G,int}$,以及栅极驱动器IC的下拉通道)流向源极(地)。

基本半导体的器件内部栅极电阻$R_{G(int)}$典型值分别为 1.7 $Omega$ 2 和 1.4 $Omega$ 。$I_{Miller}$在关断回路的总电阻($R_{G,total}$)上产生一个瞬时的正向电压尖峰($V_{GS,spike}$):

$$V_{GS,spike} approx I_{Miller} times R_{G,total}$$

如果这个$V_{GS,spike}$的峰值超过了MOSFET的栅极阈值电压 $V_{GS(th)}$,S2将瞬间被错误地(寄生)导通 。这会导致上下桥臂在短时间内同时导通,形成“直通”(Shoot-through),急剧增加开关损耗,并可能导致器件永久性损坏 。

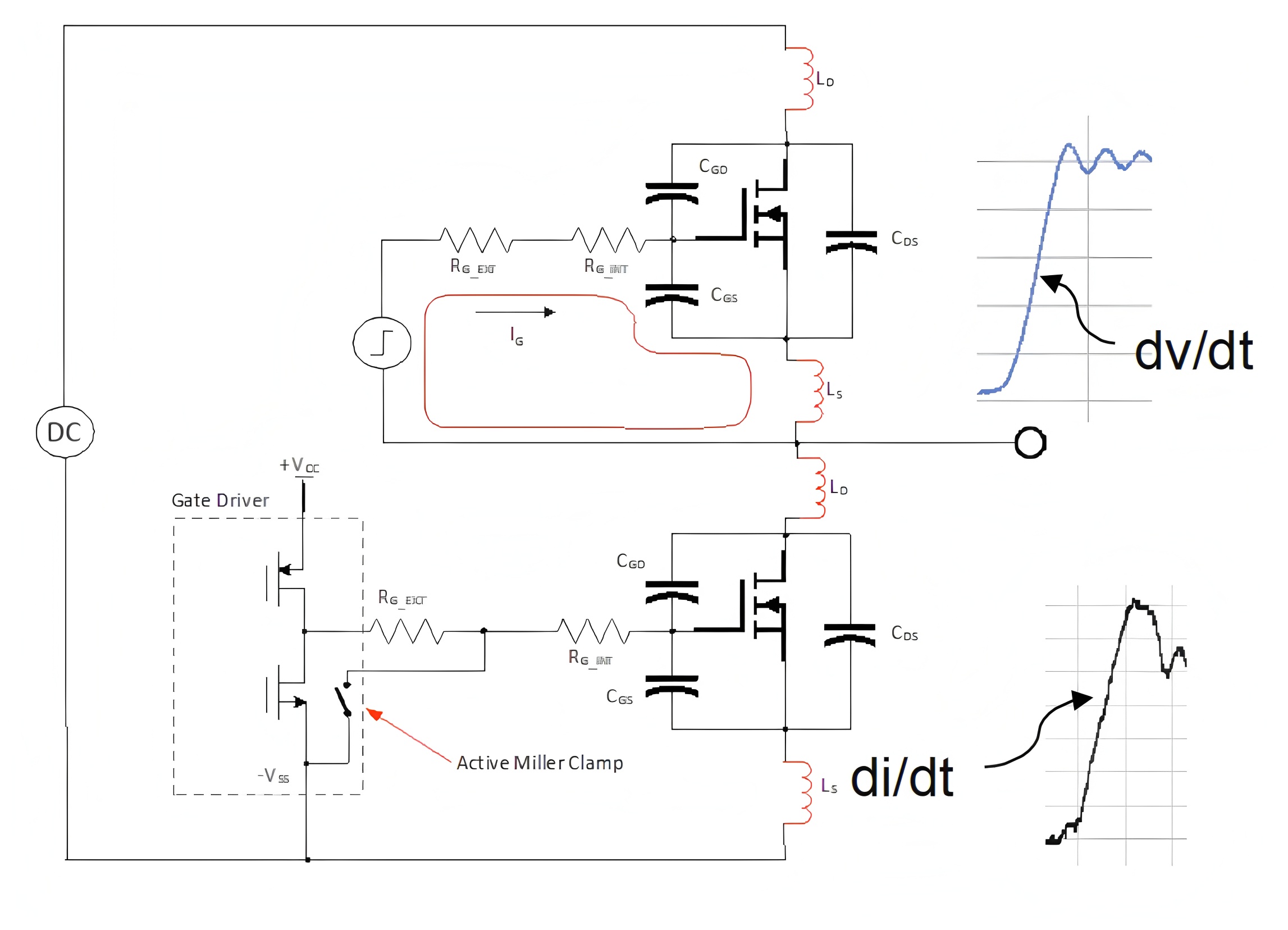

1.3 为什么SiC MOSFET比Si MOSFET更易串扰?——器件特性与开关速度的必然代价

串扰问题在SiC MOSFET应用中远比传统的硅(Si)IGBT或Si MOSFET中更为突出。这并非因为SiC器件“脆弱”,而是其核心性能优势所伴随的必然物理结果 。

SiC MOSFET的核心价值在于其极低的开关损耗和高功率密度,这使其能够工作在比Si器件高得多的开关频率下 。SiC实现这一优势的关键在于其极低的栅极电荷($Q_G$)。低$Q_G$意味着可以用更小的驱动功率实现更快的开关瞬态 。

这种“快”直接导致了极高($dV/dt$)和($di/dt$)的产生 。根据1.1节的公式,高$dV/dt$直接导致了高$I_{Miller}$。与此同时,许多SiC MOSFET(特别是早期几代产品)的$V_{GS(th)}$设计得相对较低,以确保在+18V驱动下能获得足够低的导通电阻$R_{DS(on)}$ 。

因此,SiC的“低$Q_G$”(优势)导致了“高$dV/dt$”(目标),“高$dV/dt$”导致了“高$I_{Miller}$”(物理现实),而“低$V_{GS(th)}$”(特性)使得“高$I_{Miller}$”更容易触发“寄生导通” 。串扰,正是SiC追求高速性能所必须应对的“B面”挑战。

第二章:负压关断(NGT)对串扰的决定性抑制机理

为了应对第一章所描述的串扰风险,采用负栅极关断电压(NGT)成为SiC MOSFET驱动设计中的关键技术手段。NGT的抑制作用是决定性的,其机理体现在三个层面:

2.1 裕量倍增:负偏压如何构建“安全护城河”

NGT最直接、最核心的作用,是极大地增加了栅极的“噪声裕量”(Noise Margin)。噪声裕量定义为栅极阈值电压与栅极关断电压之间的差值:

$$Margin = V_{GS(th)} - V_{GS(off)}$$

以基本半导体的B3M013C120Z为例,其典型$V_{GS(th)}$为2.7V 。

在0V关断(ZVT)方案下:

$Margin_{0V} = 2.7V - 0V = 2.7V$

在-5V关断(NGT)方案下:

$Margin_{-5V} = 2.7V - (-5V) = 7.7V$

通过施加-5V负压,栅极的噪声裕量被倍增至7.7V,相较于0V关断方案提升了285%。这意味着$I_{Miller}$所引起的$V_{GS,spike}$必须爬升一个高达7.7V的电压门槛,才能触发寄生导通 。在合理的电路布局(低寄生电感)和栅极电阻设计下,这几乎是不可能的,从而从根本上“决定性地抑制”了串扰的发生。

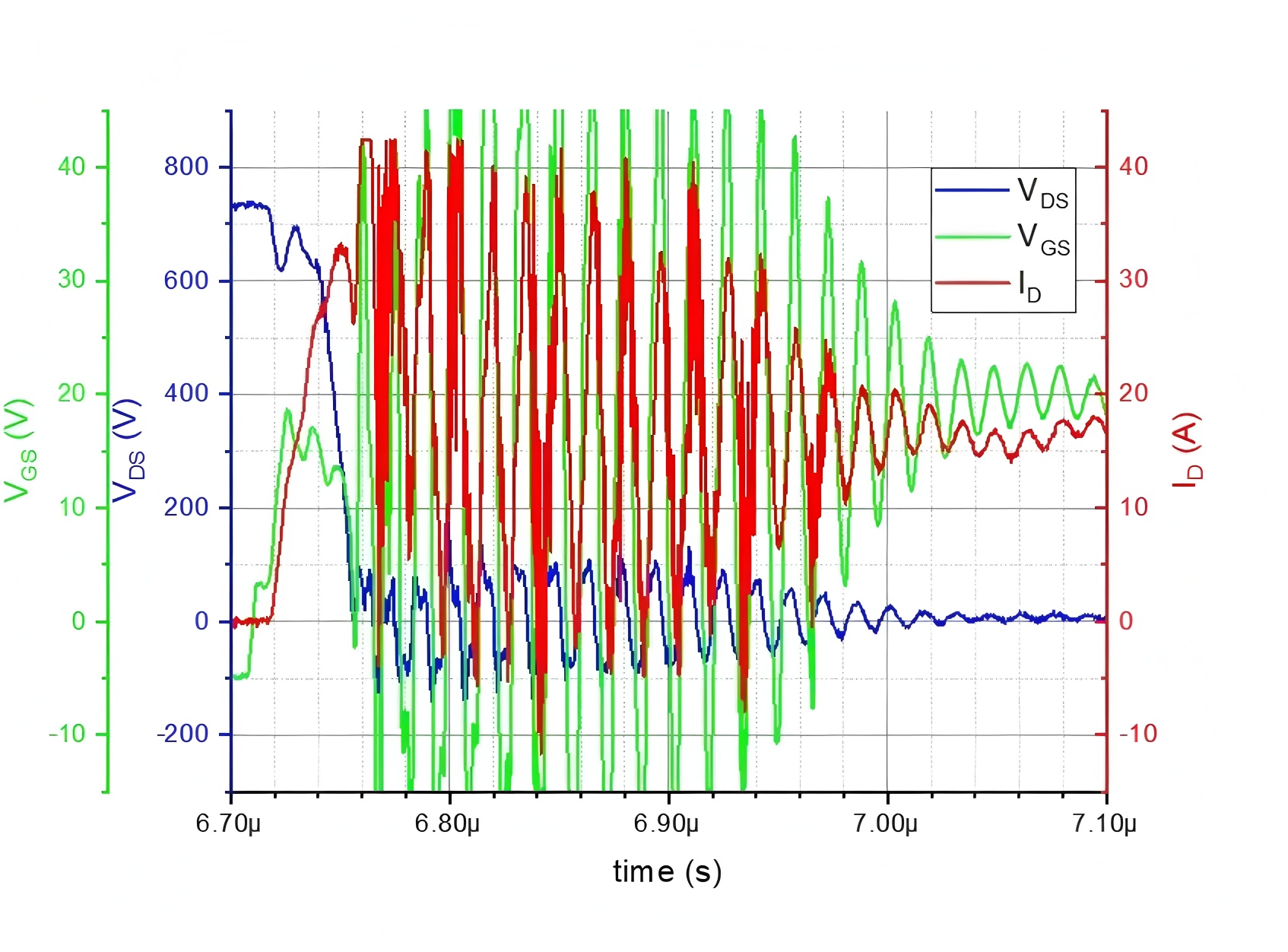

2.2 动力学分析:-5V关断电压下米勒电流的瞬态响应

NGT的意义不仅在于静态的“电压裕量”,更在于动态的“能量吸收”机制。

在0V关断时,$I_{Miller}$(正电流)注入栅极后,立即开始对$C_{gs}$进行正向充电,使$V_{GS}$从0V向$V_{GS(th)}$(2.7V)爬升。

在-5V关断时,$I_{Miller}$注入栅极后,必须首先**中和**掉$C_{gs}$上存储的负电荷(即将其栅压从-5V“拉”回0V),然后才能**继续**进行正向充电,使其向$V_{GS(th)}$(2.7V)爬升 。

这个-5V的“电荷空穴”或“能量缓冲区”,为栅极提供了一个吸收瞬态米勒电流能量的缓冲垫。$I_{Miller}$是一个时间极短的脉冲,其所携带的总电荷($Q_{Miller}$)是有限的。在-5V方案下,这股能量脉冲在还未将栅压提升到0V之前,可能就已经结束了,$V_{GS,spike}$的峰值因此被极大削弱。

2.3 超越串扰:负压关断对开关损耗($E_{off}$)的潜在优化作用

除了提升可靠性,NGT还对开关性能(特别是关断损耗$E_{off}$)有积极的优化作用 。栅极关断速度取决于驱动器将栅极电荷($Q_G$)从栅极“抽取”出来的能力。

0V关断: 驱动电压摆幅(Driving Swing)为 $V_{GS(on)}$ 到 0V (例如 +18V 到 0V,摆幅18V)。

-5V关断: 驱动电压摆幅为 $V_{GS(on)}$ 到 -5V (例如 +18V 到 -5V,摆幅23V)。

-5V的关断电压提供了更大的电压摆幅,这意味着在关断瞬间,栅极驱动器提供了比0V关断时更强的“负向拉力”(Pull-down Strength)。这种更强的拉力导致$Q_G$以更快的速度被抽走 ,从而缩短关断延迟时间($t_{d(off)}$)和下降时间($t_f$)。

更快的关断瞬态意味着漏极电压($V_{DS}$)上升和漏极电流($I_D$)下降的交叠时间更短,这直接转化为更低的关断损耗($E_{off}$)。实验数据也证实了这一点,与双极性(-3V/18V)驱动相比,单极性(0V/18V)驱动的$E_{off}$通常更高 。因此,NGT不仅是**可靠性**(抗串扰)的需求,也是**性能**(降低$E_{off}$)的优化手段。

第三章:深度解码:基本半导体-5V推荐工作电压($V_{GSop}$)的战略意义

基本半导体在其器件数据手册中的规格定义,清晰地传达了其设计哲学和技术定位。分析其-5V $V_{GSop}$ 的意义,必须结合其器件特性与可靠性权衡。

3.1 规格解读:-5V作为“推荐工作电压”而非“绝对最大额定值”的信号

在基本半导体B3M010C075Z和B3M013C120Z的数据手册“最大额定值”(Maximum Ratings)表中,有两个关键的栅压参数 :

$V_{GSmax}$ (Gate-Source Voltage): -10V / +22V。这是器件的“绝对最大额定值”,是栅极氧化物的物理“红线”,任何瞬态或静态操作都不能逾越。

$V_{GSop}$ (Recommend Gate-Source Voltage): -5V / +18V。这是“推荐工作电压”,是厂家推荐的、用于实现数据手册中标称性能的持续工作范围。

将-5V写入$V_{GSop}$,是一个极其重要的工程指令。它意味着基本半导体期望系统设计师在-5V下操作该器件。事实上,其数据手册中所有关键的动态特性,如栅极电荷$Q_G$ 、开关特性($t_d(on), t_r, t_d(off), t_f$)2 和开关损耗($E_{on}, E_{off}$)2,均是在 $V_{GS}=-5V/+18V$ 的摆幅下测试和表征的。

结合其2.7V的典型$V_{GS(th)}$ ,此举表明基本半导体认为2.7V的噪声裕量(在0V关断时)在高速应用中风险过高。因此,-5V的$V_{GSop}$是其实现数据手册所承诺的低开关损耗和高动态可靠性(无串扰)的必要条件。

3.2 核心权衡(The Core Trade-off):NBTI与栅氧可靠性挑战

然而,推荐-5V $V_{GSop}$ 是一个必须面对严苛可靠性挑战的“双刃剑”。栅极氧化物(Gate Oxide)的长期可靠性,特别是SiC/SiO2界面,是SiC MOSFET技术的核心难点 。

其中一个关键挑战是负偏压温度不稳定性(Negative Bias Temperature Instability, NBTI)。当MOSFET栅极在高温下(如150°C至175°C)长期承受负偏压(如-5V)时,会导致界面陷阱的产生 4 和氧化物陷阱中的空穴俘获 。

这些被俘获的正电荷(空穴)会永久性地改变栅极氧化物的电场分布,其宏观表现为MOSFET的$V_{GS(th)}$发生**负向漂移**(即$V_{GS(th)}$降低)。$V_{GS(th)}$的降低会使器件更接近导通,从而削弱抗串扰能力。

3.3 可靠性悖论:-5V负压的“恶性循环”

这就导出了一个严峻的“可靠性悖论”:

问题: 器件的 $V_{GS(th)}$ 较低(例如基本半导体的2.7V ),导致串扰风险高。

解决方案: 施加-5V $V_{GS(off)}$以获得7.7V的巨大噪声裕量 。

长期副作用: -5V $V_{GS(off)}$在高温下(SiC的常规工作温度)引起NBTI效应 。

NBTI的后果: $V_{GS(th)}$发生负向漂移,例如从2.7V降低至2.0V 。

新的问题: $V_{GS(th)}$的降低,导致用于抗串扰的噪声裕量($Margin = V_{GS(th)} - V_{GS(off)}$)也随之降低(从7.7V降至7.0V)。

这是一个潜在的“恶性循环”:用于解决低$V_{GS(th)}$问题的-5V负压,反过来又会随着时间的推移而进一步降低$V_{GS(th)}$,削弱器件的长期可靠性。相关研究明确指出,-5V负压比-3V负压会显著加速NBTI效应 。

3.4 技术宣言:-5V背后的工艺自信

基本半导体(作为专业的器件制造商)深刻理解3.3节中描述的NBTI风险。那么,他们为何敢于将-5V写入“推荐工作电压”?

答案在于其技术平台的进步。基本半导体在其第三代SiC MOSFET技术平台(B3M系列)的介绍中,明确提升提升可靠性” 。

因此,数据手册上 的“-5V” $V_{GSop}$ 不仅仅是一个驱动建议,它更是一个技术宣言。它在向市场宣告:基本半导体的“第三代技术平台”及其“优化的工艺” ,已经具备了足以承受-5V长期NBTI应力的工艺水平和可靠性。

基本半导体自信其器件在推荐的-5V关断电压下,通过严苛的高温栅极偏压(HTGB)可靠性测试(例如,在-10V $V_{GSmax}$ 和175°C下,或在-5V $V_{GSop}$ 和175°C下,持续1000小时),$V_{GS(th)}$的漂移被控制在极其微小和可接受的范围内,不会导致器件的长期失效。

第四章:主流SiC MOSFET厂商栅极关断电压策略横向对比

对主流SiC MOSFET制造商的关断策略进行横向对比,可以发现一个清晰的“分水岭”:器件的 $V_{GS(th)}$ 设计,直接决定了其推荐的 $V_{GS(off)}$ 策略。

4.1 零电压关断(0V-ZVT)阵营:技术演进的趋势(高 $V_{GS(th)}$)

这一阵营的厂商通过器件结构和工艺的革新,大幅提高了$V_{GS(th)}$,使其具备了使用0V关断的底气,旨在简化系统设计。

4.1.1 Infineon (英飞凌) (CoolSiC G2)

$V_{GS(th)}$: 典型值 4.5V (例如IMDQ75R016M2H, @25°C)。这是一个非常高的值,提供了天然的抗串扰能力。

$V_{GS(off)}$ 策略: 明确推荐0V关断 。英飞凌在其应用笔记中强调,其高$V_{GS(th)}$设计使其“完全免疫寄生导通”,使用0V关断可简化驱动电路、降低成本 。

策略分析: 尽管英飞凌推荐0V,但其G2器件的数据手册却将静态$V_{GS}$范围扩大到 -7V / +23V 。这是一个高明的市场兼容策略。它在传达:“我们的器件足够好,0V就行 ;但如果您的系统(为了兼容其他需要负压的厂商)已经设计了-5V驱动,我们的器件也能完美承受(-7V静态耐受),您可以无缝替换。”

4.2 传统负压(NGT)阵营:基于阈值电压的现实选择(中低 $V_{GS(th)}$)

这一阵营的厂商$V_{GS(th)}$处于中低水平,因此依赖NGT作为确保动态可靠性的标准实践。

4.2.1 onsemi (安森美) (EliteSiC M3S)

$V_{GS(th)}$: 典型值 4.0V (例如NTHL032N065M3S) 。这是一个中高水平。

$V_{GS(off)}$ 策略: 推荐 $V_{GSop}$ (Recommended Operating Conditions) 为 -5V...-3V 。其开关损耗数据也均在-3V 或-3V/-5V 38 条件下测得。

策略分析: onsemi的4.0V $V_{GS(th)}$ 37 理论上比ST和Wolfspeed更有条件实现0V关断。但onsemi 仍推荐-3V至-5V ,这表明其设计哲学极为保守和稳健。他们不愿在噪声裕量上妥协,宁愿牺牲驱动的简洁性,也要确保在最恶劣的工况下器件依然绝对可靠。

4.2.3 STMicroelectronics (意法半导体) (Gen 3)

$V_{GS(th)}$: 典型值 3.0V (例如SCT070W120G3-4) 。

$V_{GS(off)}$ 策略: $V_{GS}$ 推荐工作值为 -5V to +18V 。其应用笔记 明确指出,负压(-2V至-5V)是“最佳权衡”(best trade-off),用于在VGS(th)和负向AMR(绝对最大额定值)尖峰之间提供安全裕量 。

策略分析: ST的策略与基本半导体类似,其3.0V的$V_{GS(th)}$不足以(像Infineon那样)自信地推荐0V关断,因此负压是确保裕量的标准实践。

4.3 关键数据对比矩阵

下表总结了上述分析,直观地展示了$V_{GS(th)}$与$V_{GS(off)}$策略之间的强关联性。

表1:主流SiC MOSFET厂商关断电压 ($V_{GS(off)}$) 与栅极阈值电压 ($V_{GS(th)}$) 对比

| 厂商 (Manufacturer) | 产品世代 (Generation) | 典型 VGS(th) (@25°C) | 推荐 VGS(off) | 关键技术策略与数据来源 |

|---|---|---|---|---|

| 基本半导体 (BASIC Semi) | Gen 3 | 2.7 V (B3M013C120Z) | -5 V (VGSop) | 稳健性优先: 中低$V_{GS(th)}$,依赖-5V确保裕量。隐含对工艺抗NBTI的自信。 |

| Infineon (英飞凌) | CoolSiC G2 | 4.5 V (IMDQ75R016M2H) | 0 V (推荐) / -7V (兼容) | 性能与兼容并重: 高$V_{GS(th)}$ 支持0V ;-7V静态能力 确保对负压系统的“多源兼容性”。 |

| onsemi (安森美) | EliteSiC M3S | 4.0 V (NTHL032N065M3S) | -3 V to -5 V (VGSop) | 保守稳健派: 尽管$V_{GS(th)}$较高 ,仍推荐负压以保留最大设计裕量 。 |

| STMicroelectronics | Gen 3 | 3.0 V (SCT070W120G3-4) | -2 V to -5 V | 平衡权衡: 中低$V_{GS(th)}$ ,推荐-5V工作 9,视-2V至-5V为可靠性的“最佳权衡点” 。 |

| Wolfspeed | C3M (Gen 3) | 2.3 V (C3M0015065D) | -4 V (VGSop) | 刚$V_{GS(th)}$ 使负压关断成为保证可靠性的“必须”手段 。 |

第五章:系统应用设计的战略考量与结论

5.1 驱动设计的二元论:0V的简洁性 vs. -5V的强健性

基于第四章的分析,SiC MOSFET的驱动策略已明显分为两大流派,系统设计师必须根据应用需求做出战略选择。

5.1.1 0V ZVT (零电压关断) 方案 (Infineon)

优势: 极大简化了栅极驱动器的电源设计 。系统设计师不再需要昂贵、复杂、占空间的双极性(Bipolar)隔离电源(如 +/- Vcc),只需一个单极性(Unipolar)电源(如 0V/+18V)即可 。这对于成本和空间敏感的应用(如中低功率SMPS、光伏逆变器)是巨大的福音。

前提: 必须选用$V_{GS(th)}$足够高(>4.0V)的器件,如Infineon G2 。

5.1.2 -5V NGT (负压关断) 方案 (BASIC Semi, Wolfspeed, ST, onsemi)

优势:

强健性 (Robustness): 提供了无与伦比的抗串扰噪声裕量 ,是高$dV/dt$、高杂散电感、高可靠性要求的严苛应用(如储能变流器PCS,光伏逆变器、大功率工业电机)的首选。

性能 (Performance): 提供了更强的关断拉力,可实现更低的$E_{off}$ 。

代价 (Cons):

驱动复杂性: 必须设计和实现双极性隔离电源 ,增加了BOM成本和PCB面积。

可靠性风险: 必须信任器件制造商的栅氧工艺能终生(全寿命周期)承受-5V的NBTI应力 。

5.2 最终报告:基本半导体的市场定位与系统设计师的抉择

5.2.1 基本半导体(-5V)的定位:面向高可靠、高应力环境的“稳健型”解决方案

基本半导体通过-5V $V_{GSop}$ 和“优化工艺” 1的组合,向市场传递了一个清晰的信号:我们提供的是一个以动态性能和可靠性为最高优先级的解决方案。我们不追求0V驱动的噱头,而是通过-5V负压确保器件在最恶劣的瞬态下(2/2的开关特性均在-5V下表征)绝对稳定,同时我们用优化的工艺向您保证,这种负压不会损害器件的长期寿命(NBTI)。

5.2.2 Infineon(0V)的定位:面向高集成度、低成本的“革新型”解决方案

Infineon则代表了另一条技术路径:通过器件物理的革新(高$V_{GS(th)}$)来消除系统设计的痛点(负压驱动) 。它们的目标是降低SiC的使用门槛,使其像硅MOSFET一样易于驱动 ,从而加速其在成本敏感型应用中的普及。

深圳市倾佳电子有限公司(简称“倾佳电子”)是聚焦新能源与电力电子变革的核心推动者:

倾佳电子成立于2018年,总部位于深圳福田区,定位于功率半导体与新能源汽车连接器的专业分销商,业务聚焦三大方向:

新能源:覆盖光伏、储能、充电基础设施;

交通电动化:服务新能源汽车三电系统(电控、电池、电机)及高压平台升级;

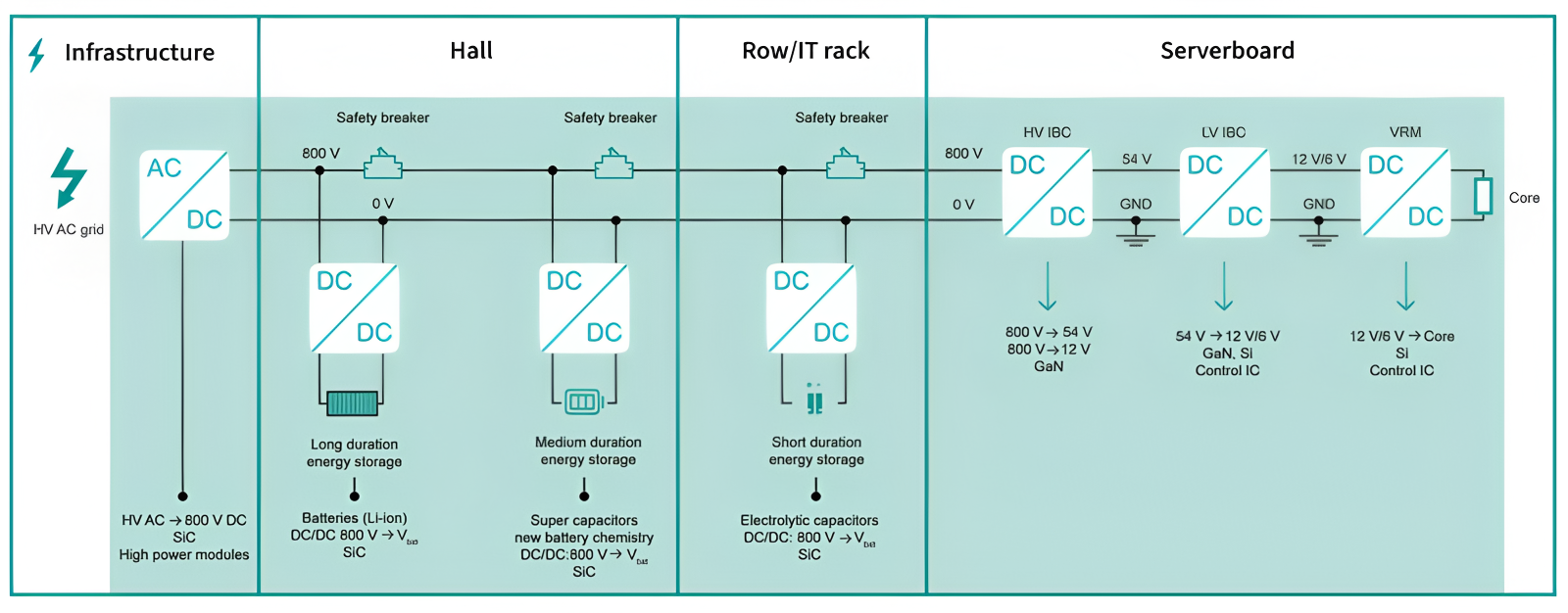

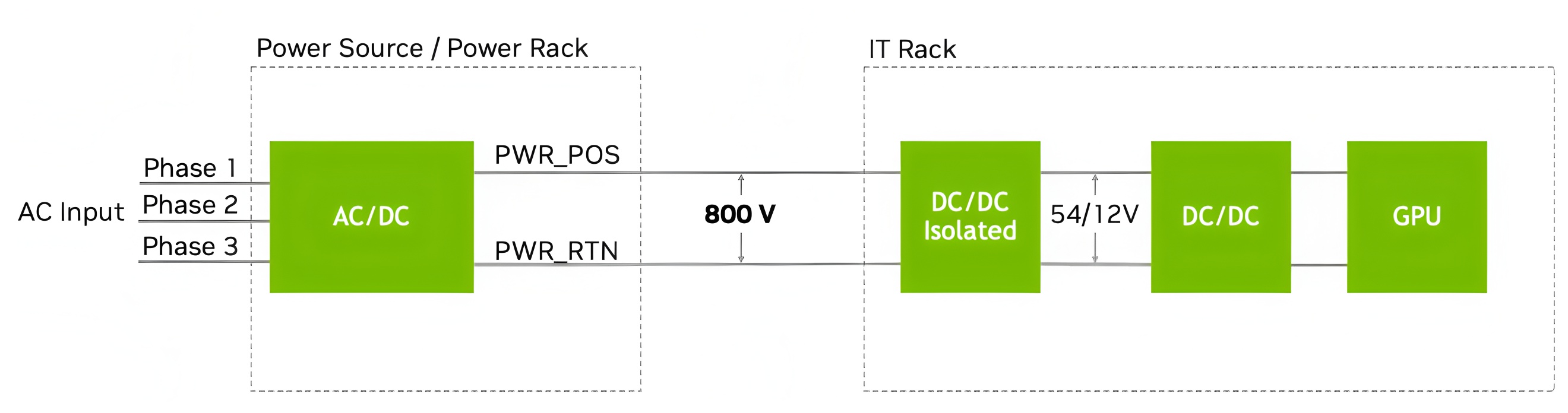

数字化转型:支持AI算力电源、数据中心等新型电力电子应用。

公司以“推动国产SiC替代进口、加速能源低碳转型”为使命,响应国家“双碳”政策(碳达峰、碳中和),致力于降低电力电子系统能耗。

需求SiC碳化硅MOSFET单管及功率模块,配套驱动板及驱动IC,请添加倾佳电子杨茜微芯(壹叁贰 陆陆陆陆 叁叁壹叁)

5.2.3 系统设计师的最终抉择

选择基本半导体 (-5V): 当应用(如大功率电机驱动、储能变流器PCS)具有极高的$dV/dt$、复杂的母线布局(高杂散电感),且可靠性是第一要素(不允许任何串扰引发的失效)时,基本半导体的-5V方案提供了一个经过厂家验证的、强健的“交钥匙”方案。系统必须为其配置一个-5V的驱动电源 ,并信任其NBTI可靠性 。

选择Infineon (0V): 当应用(如高密度OBC、SMPS)对成本、体积和驱动电路的简洁性有极致追求时 ,选用高$V_{GS(th)}$的器件并采用0V关断,是实现更高集成度和更低系统成本的最优路径。

结论: 负压关断并非过时技术,而是一种“保守”且“强效”的可靠性策略。基本半导体推荐-5V $V_{GSop}$,是其对器件$V_{GS(th)}$特性(2.7V)的诚实响应,也是对其第三代栅氧工艺平台(抗NBTI)可靠性的自信背书。

审核编辑 黄宇

-

功率半导体

+关注

关注

23文章

1507浏览量

45285 -

SiC MOSFET

+关注

关注

1文章

171浏览量

6818 -

基本半导体

+关注

关注

2文章

116浏览量

11367

发布评论请先 登录

倾佳电子深度解析SiC MOSFET负压关断的串扰抑制机理与-5V工作电压的技术意义——暨主流厂商关断策略横向对比

倾佳电子深度解析SiC MOSFET负压关断的串扰抑制机理与-5V工作电压的技术意义——暨主流厂商关断策略横向对比

评论