【博主简介】本人“爱在七夕时”,系一名半导体行业质量管理从业者,旨在业余时间不定期的分享半导体行业中的:产品质量、失效分析、可靠性分析和产品基础应用等相关知识。常言:真知不问出处,所分享的内容如有雷同或是不当之处,还请大家海涵。当前在各网络平台上均以此昵称为ID跟大家一起交流学习!

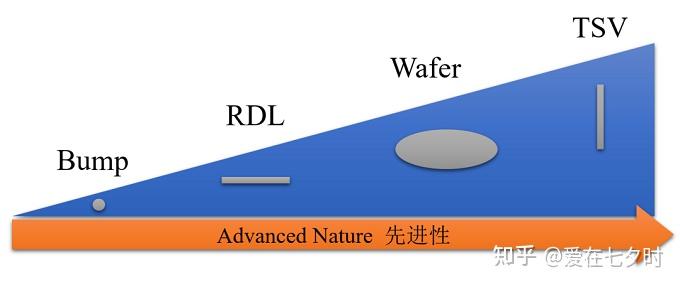

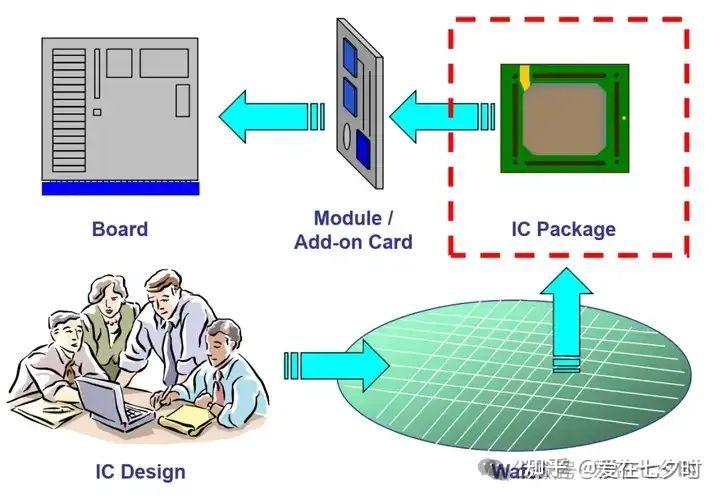

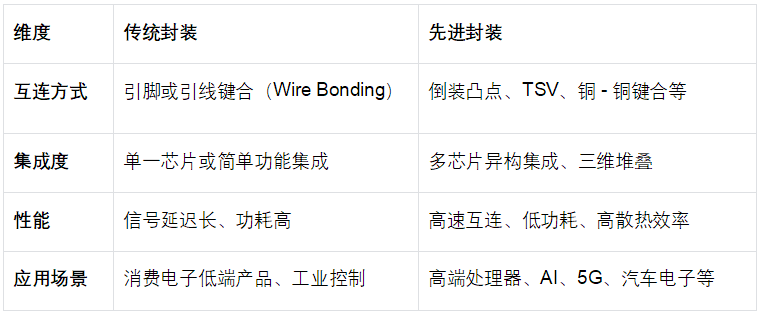

从事半导体行业的朋友都知道:随着半导体工艺逼近物理极限,传统制程微缩已经无法满足高带宽、低延迟的需求。这时候,先进封装技术应运而生,成为提升芯片性能的关键路径。

先说说什么是先进封装吧。简单来说,就是通过高密度互连、异构集成等方式,将多个芯片或功能模块集成在单一封装体内,从而提升整体性能、降低功耗并缩小体积。这一技术已经成为全球半导体行业的焦点,尤其在人工智能、5G通信、高性能计算(HPC)等领域,传统封装已经无法满足需求了。

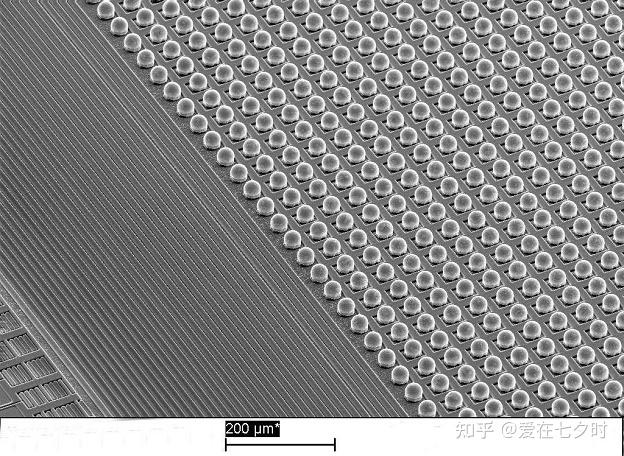

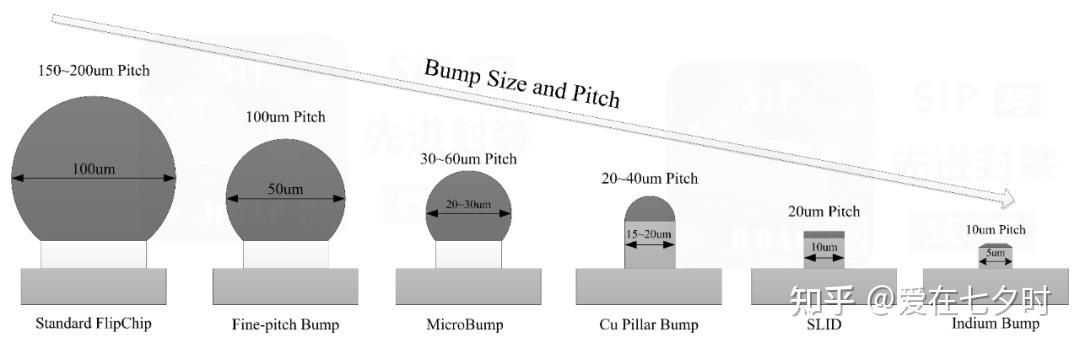

先进封装的典型应用场景在这里我就不多赘述了,有兴趣的朋友可以查阅我公众号里之前的文章就可找到很多与之“先进封装”相关的行业知识。那讲到“先进封装”,Flip-Chip(倒装芯片)便是它的最大市场,而讲到Flip-Chip(倒装芯片)封装,Bumping工艺技术就是其主要的工艺,显著提高集成密度。目前,头部晶圆制造厂将Bump Pitch推进至10μm以下,国内大封装厂挺近40μm。本文为您概述了当前微凸块的全球新进展。

一、先进封装Bumping工艺技术的介绍

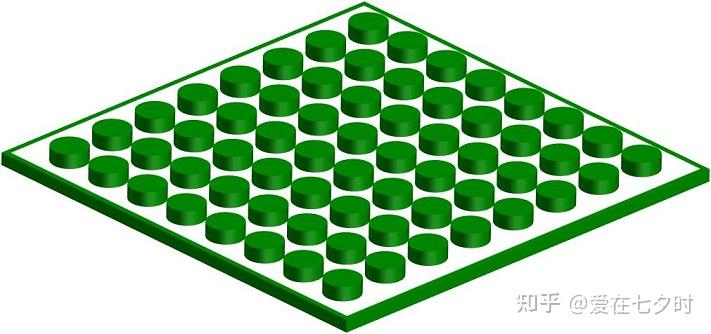

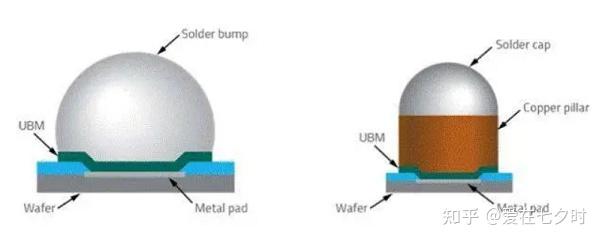

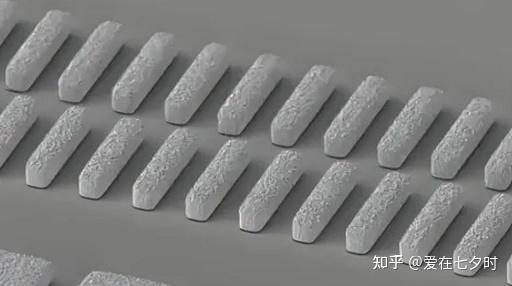

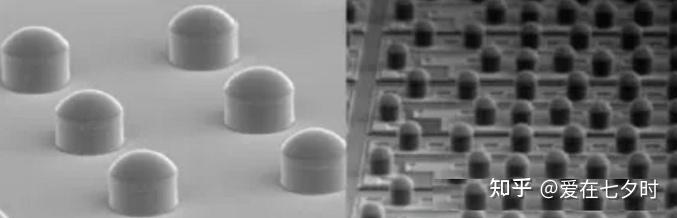

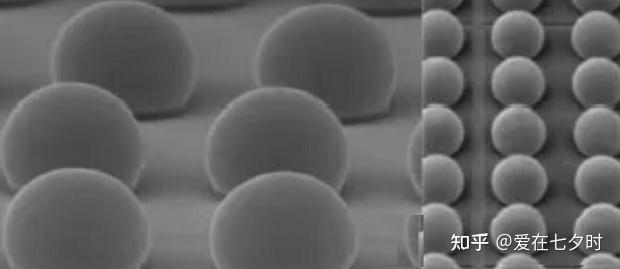

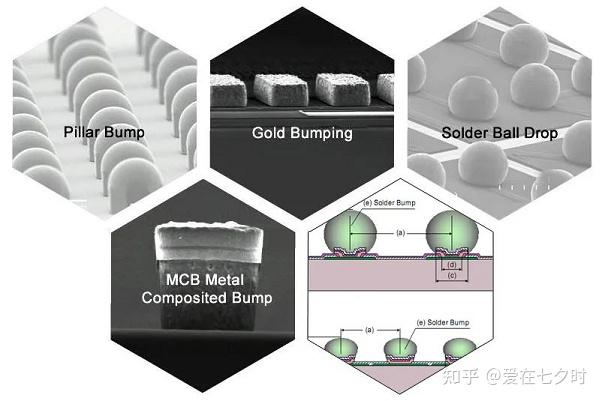

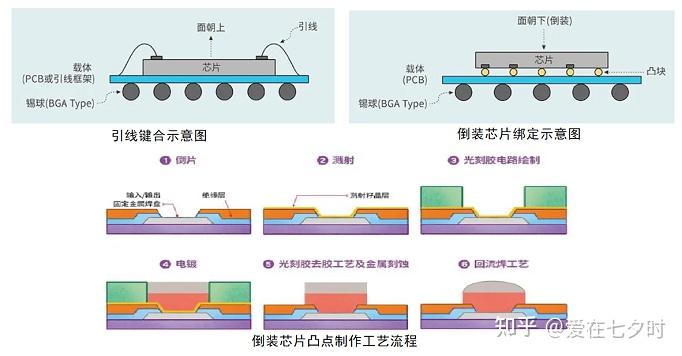

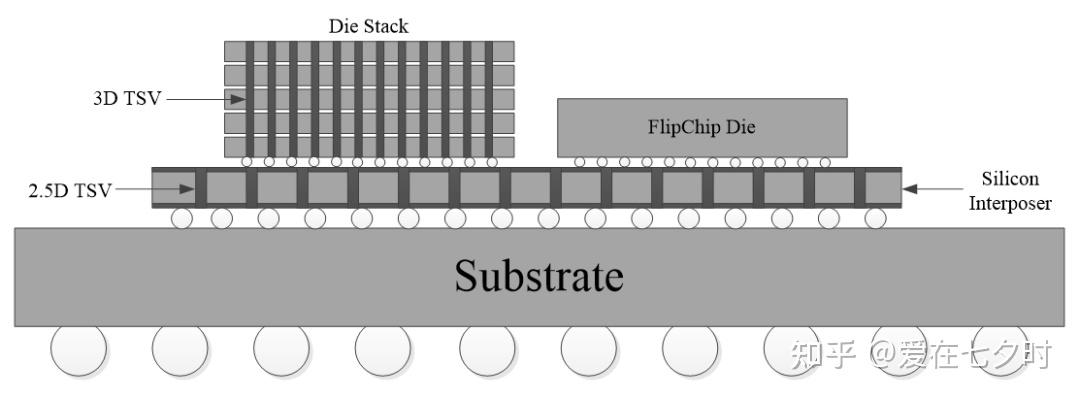

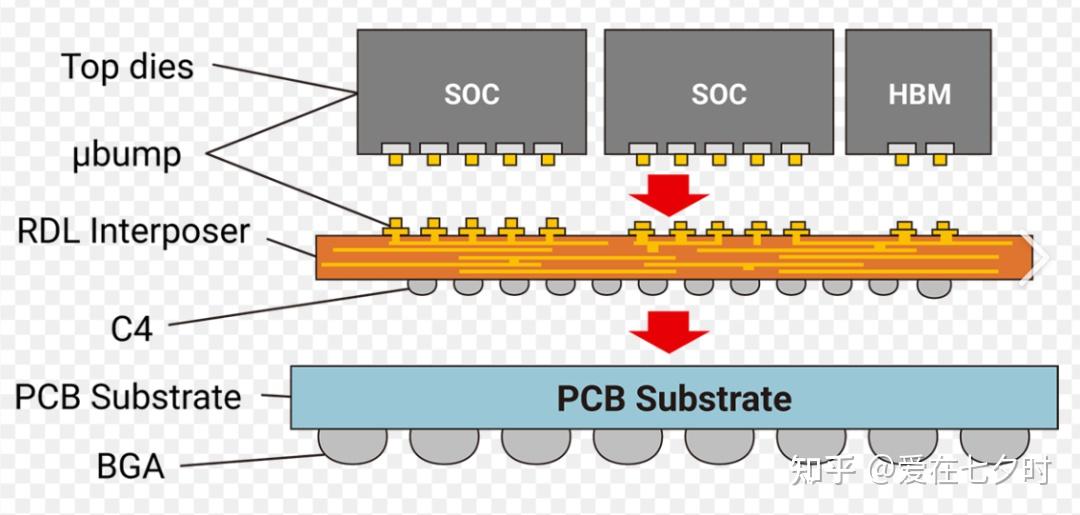

在先进封装中,Bumping/μBumping,通常是指(微)凸块,这种工艺制造技术是倒装等发展演化的基础工程,并延伸演化出TSV、WLP、2.5D/3D、MEMS等封装结构与工艺,广泛应用于5G、人工智能、云计算、可穿戴电子、物联网、大数据处理及储存等集成电路应用中。且Bumping工艺技是一种关键的连接技术,它是在芯片表面制作的小凸起,一般只有几十到几百微米大小,主要作用是提供芯片与其他电子元件之间的电气连接,从倒装焊FlipChip出现就开始普遍应用了,Bumping工艺技术的形状也有多种,最常见的为球状和柱状,也有块状等其他形状。Bumping工艺技术起着界面之间的电气互联和应力缓冲的作用,从Bondwire工艺发展FlipChip工艺的过程中,Bumping工艺技术起到了至关重要的作用。

随着工艺技术发展,Bumping工艺技术的发展趋势是尺寸不断缩小,从球栅阵列焊球(BGA ball),其直径范围通常在0.25-0.76mm,到倒装凸点(FC Bump),也被称为可控塌陷芯片焊点(C4 solder joint),其直径范围通常在100-150μm。行业内正朝着 20μm 甚至小于 10μm 的方向推进,凸点间距越小,凸点密度越高,封装集成度越高,技术难度也越大。对于 20μm 以上的间距,可采用基于热压键合(TCB)的微凸块连接技术,未来混合键合(HB)铜对铜连接技术有望实现 10μm 以下的凸块间距和更高的凸点密度,并带动带宽和功耗双提升。

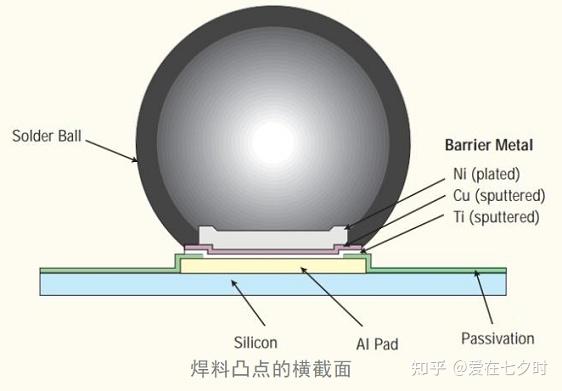

作为一种先进的晶片级工艺技术,Bumping工艺技术在将晶片切割成单个芯片之前,在整个晶片形式的晶片上形成由焊料制成的“凸点”或“球”。凸块制作的材质可分为金凸块、铜镍金凸块、铜柱凸块、焊球凸块。凸块将管芯和衬底一起互连到单个封装中的基本互连部件,每个凸块都是一个IC信号触点,成为了芯片之间、芯片和基板之间的“点连接”。

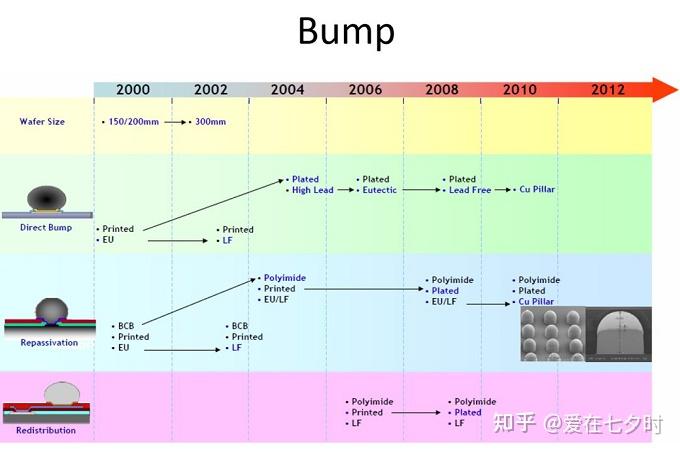

二、先进封装Bumping工艺技术的起源与发展历程

Bumping工艺技术起源于IBM在20世纪60年代开发的C4工艺,即可控坍塌芯片连接技术。该技术使用金属共熔凸点将芯片直接焊在基片的焊盘上,这是集成电路凸块制造技术的雏形,也是实现倒装封装技术的基础,但当时这种封装方式成本极高,仅用于高端IC的封装,限制了其广泛使用。例如在当时,这种技术主要应用于高端服务器芯片等对性能要求极高的领域,因为其他领域难以承受高昂的成本。

随着时间的推移,C4工艺逐渐优化,如采用在芯片底部添加树脂的方法,增强了封装的可靠性,促使低成本的有机基板得到发展,使得FC技术能在集成电路以及消费电子器件中以较低成本使用。在20世纪80年代到21世纪初,集成电路产业从日本向韩国、中国台湾转移,国际分工深化,凸块制造技术由蒸镀工艺转变为溅镀与电镀相结合的凸块工艺,大幅缩小了凸块间距,提高了产品良率。近年来,芯片集成度提高,细节距和极细节距芯片出现,推动Bumping工艺技术朝着高密度、微间距方向发展,比如现在一些高端智能手机芯片的封装就对Bumping工艺技术的高密度、微间距特性有较高要求。

三、先进封装Bumping工艺技术的流程

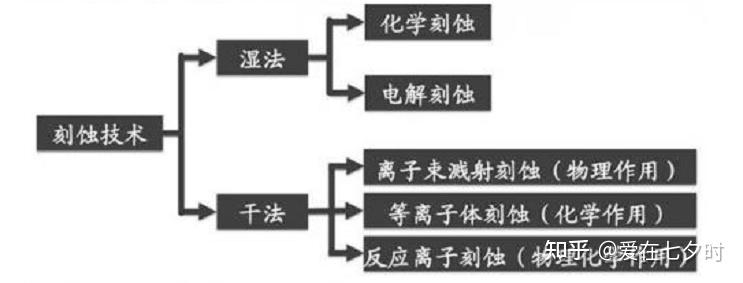

Bumping工艺技术制作过程复杂,需要清洗、溅镀、曝光、显影、电镀去胶、蚀刻和良品测试等环节,其对应材料需求为清洗液、靶材、电镀液、光刻胶、显影液、 蚀刻液等。主要的工艺步骤如下:

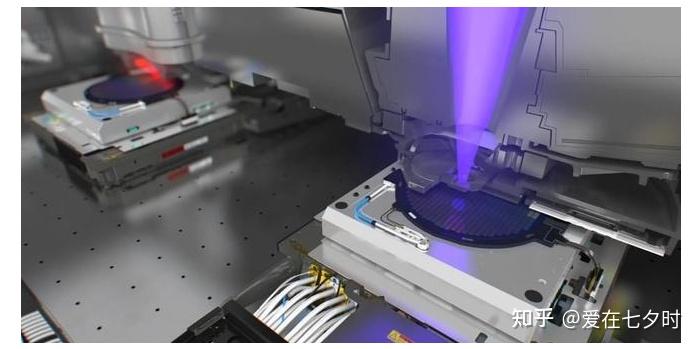

(1)、采用溅射或其他物理气相沉积的方式在晶圆表面沉积一层钛或钛钨作为阻挡层,再沉积一层铜或其他金属作为后面电镀所需的种子层。在沉积金属前,晶圆先进入溅射机台的预清洁腔体,用氩气等离子去除焊盘金属表面的氧化层。

(2)、在晶圆表面旋涂一定厚度的光刻胶,并运用光刻曝光工艺,以改变其在显影液中的溶解度。光刻胶与显影液充分反应后,得到设计所需的光刻图形。

(3)、晶圆进入电镀机,通过合理控制电镀电流、电镀时间、电镀液液流、电镀液温度等,得到一定厚度的金属层作为UBM(Under Bump Metallization,凸点下 金属化层)。在有机溶液中浸泡后,圆片表面的光刻胶被去除;再用相应的腐蚀液去除晶圆表面UBM以外区域的溅射种子层和阻挡层。

(4)、在植球工序中,需要用两块开有圆孔的金属薄板作为掩模板,位置与晶圆表面UBM的位置相对应。在植球前,先用第1块金属掩模板将助焊剂印刷到UBM 表面;再用第2块金属掩模板将预成型的锡球印刷到UBM上;

(5)、晶圆经过回流炉使锡球在高温下熔化,熔化的锡球与UBM在界面上生成金属间化合物,冷却后锡球与UBM形成良好的结合。

采用电镀的方式也可以得到焊球凸块,即在电镀UBM完成后,接着电镀焊料; 去除光刻胶和腐蚀溅射金属后,经过回流,得到焊球凸块。电镀方式也是铜柱凸块和金凸块加工的常用方法。

因此,凸块(bumping)工艺流程的主要有以上8个步骤,电子器件向更轻薄、更微型和更高性能进步,促使凸块尺寸减小,精细间距愈 发重要。凸块间距(Bump Pitch)越小,意味着凸点密度增大,封装集成度越高,难度越来越大。行业内凸点间距正在朝着20μm推进,而实际上巨头已经实现了小于 10μm 的凸点间距。如果凸点间距超过 20μm,在内部互连的技术上采用基于热压键合(TCB)的微凸块连接技术。面向未来,混合键合(HB)铜对铜连接技术可以 实现更小的凸点间距(10μm以下)和更高的凸点密度(10000个/mm2),并带动带宽和功耗双提升。随着高密度芯片需求的不断扩大带来倒装需求的增长,Bumping工艺技术的需求将不断提升,相关材料需求也将不断提升。

言归正传,具体而言,Bumping工艺技术是先在晶圆表面沉积钛或钛钨作为阻挡层,再沉积铜等作为种子层;然后旋涂光刻胶,通过光刻曝光和显影得到所需图形;接着进行电镀形成凸点下金属化层(UBM),去除光刻胶并蚀刻掉多余的种子层和阻挡层;之后进行植球工序,将助焊剂和锡球印刷到 UBM 上;最后经过回流炉使锡球熔化与 UBM 形成良好结合。

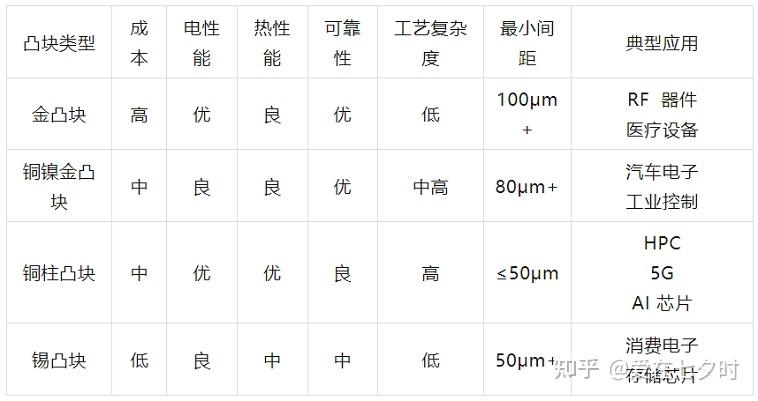

凸块制造技术是诸多先进封装技术实现和发展演化的基础:经过多年的发展,凸块制作的材质主要有金、铜、铜镍金、锡等,不同金属材质适用于不同芯片的封装,且不同凸块的特点、涉及的核心技术、上下游应用等方面差异较大。

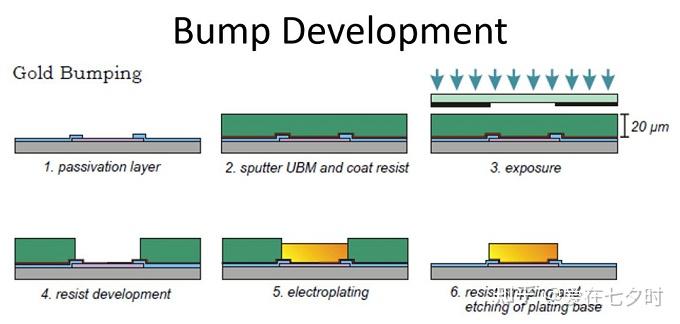

1、金凸块(Gold Bumping)

金凸块(Gold Bumping)是一种利用金凸块接合替代引线键合实现芯片与基板之间电气互联的制造技术,主要用于显示驱动芯片封装,少部分用于传感器、电子标签类产品。例如,目前LCD、AMOLED等主流显示面板的驱动芯片都离不开金凸块制造工艺。其工艺流程相对复杂,后续可通过倒装工艺将芯片倒扣在玻璃基板、柔性屏幕或卷带上,利用热压合或者透过导电胶材使凸块与线路上的引脚结合起来。

主要特点:

(1)优点:高导电性、抗腐蚀性强、键合工艺成熟、无需底部填充(Underfill)。

(2)缺点:成本高(黄金价格昂贵)、硬度低易变形、高温下可能与焊料形成脆性金属间化合物(IMC)。

(3)关键参数:典型尺寸为 50-150μm,间距 100-250μm。

(4)应用领域:

a、高频、高可靠性器件:RF模块、光通信器件、毫米波雷达;

b、医疗、航空航天:植入式医疗设备、卫星电子元件;

c、Flip Chip 封装早期应用:如早期手机芯片、FPGA。

工艺流程:

2、铜镍金凸块(CuNiAu Bumping)

铜镍金凸块(CuNiAu Bumping)可优化I/O设计、大幅降低了导通电阻。凸块主要由铜、镍、金三种金属组成,在集成电路封测领域属于新兴先进封装技术,是对传统引线键合封装方式的优化方案。例如电源管理芯片需要具备高可靠、高电流等特性,且常在高温环境下使用,铜镍金凸块可满足这些要求并大幅降低导通电阻,因此主要应用于电源管理类芯片。它可以通过大幅增加芯片表面凸块的面积,在不改变芯片内部原有线路结构的基础上,对原有芯片进行重新布线,大大提高了引线键合的灵活性,并且由于铜的占比相对较高,具有天然的成本优势。

主要特点:

(1)优点:结合铜的低成本和金的抗腐蚀性,Ni 层作为扩散阻挡层抑制 Cu-Sn IMC 生长。

(2)缺点:工艺复杂度高(三层金属沉积),需严格控制 Ni 层厚度(过薄易穿透,过厚易脆)。

(3)关键参数:Cu柱高度50-100μm,Ni层厚度3-5μm,Au层厚0.3-1μm。

(4)应用领域:

b、工业设备:高可靠性传感器、控制器;

c、消费电子:中高端手机摄像头模组、指纹识别芯片。

工艺流程:

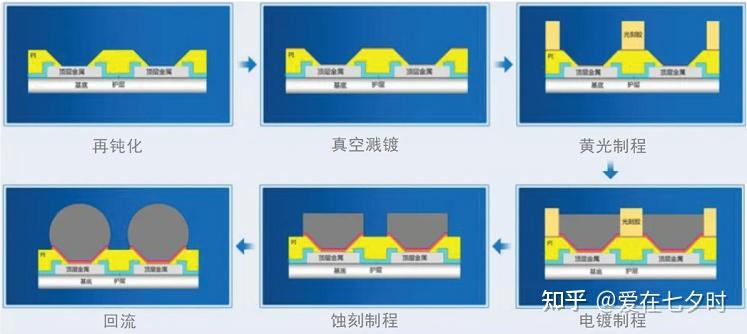

3、铜柱凸块(Cu Pillar)

铜柱凸块(Cu Pillar)是利用铜柱接合替代引线键合实现芯片与基板之间电气互联的制造技术。这是新一代芯片互连技术,后段适用于倒装的封装形式,应用十分广泛。例如在覆晶封装芯片的表面制作焊接凸块,以代替传统的打线封装,可以缩短连接电路的长度、减小芯片封装体积,使其具备较佳的导电、导热和抗电子迁移能力。其制造主要步骤包括再钝化、真空溅镀、黄光、电镀、蚀刻等。

主要特点:

(1)优点:低电阻(铜导电性优于锡)、高热导率、更好的机械稳定性(抗跌落测试)、适合细间距(≤50μm)。

(2)缺点:易氧化(需表面处理)、Cu-Sn IMC 生长可能导致可靠性问题。

(3)关键参数:Cu柱直径 10-50μm,高度 30-60μm,表面通常有 Ni/Au 或 Sn/Ag 涂层。

(4)应用领域:

b、5G 通信:RF 前端模块、高速 SerDes 芯片;

c、AI 芯片:需要高密度 I/O 的 ASIC、FPGA。

工艺流程:

4、锡凸块(Sn Bumping)

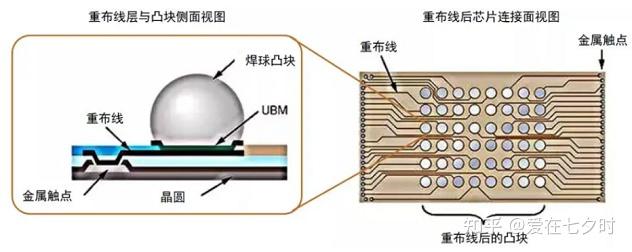

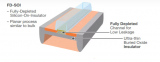

锡凸块(Sn Bumping)是利用锡接合替代引线键合实现芯片与基板之间电气互联。锡凸块结构主要由铜焊盘和锡帽构成(一般配合再钝化和RDL层),锡凸块一般是铜柱凸块尺寸的3 - 5倍,球体较大,可焊性更强(也可通过电镀工艺,即电镀高锡柱并回流后形成大直径锡球),并可配合再钝化和重布线结构,主要用于FC制程。多应用于晶圆级芯片尺寸封装,可以达到小尺寸封装,满足封装轻、薄、短、小的要求。

主要特点:

(1)优点:工艺简单、成本低、自对准能力强(回流时液态表面张力)。

(2)缺点:电性能较差(电阻高于铜)、热循环可靠性有限(锡易疲劳)。

(3)关键参数:典型成分为 SnAgCu(SAC)合金,尺寸 30-200μm,间距 50-400μm。

(4)应用领域:

a、消费电子:智能手机、平板电脑、可穿戴设备;

b、存储芯片:DDR、NAND Flash 封装;

c、低成本/中低端器件:如 WiFi 模块、蓝牙芯片。

工艺流程:

5、技术对比与选择标准

四、先进封装Bumping工艺技术的基本原理与作用

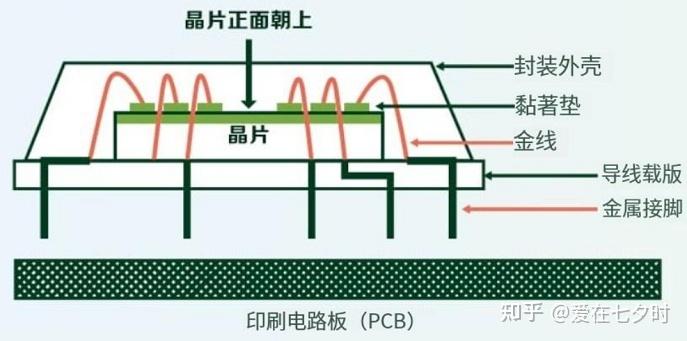

Bumping工艺技术是在芯片上制作凸块,凸块是定向生长于芯片表面,与芯片焊盘直接相连或间接相连的具有金属导电特性的凸起物。这些凸块通过在芯片表面制作金属凸块提供芯片电气互连的“点”接口,广泛应用于FC(倒装)、WLP(晶圆级封装)、CSP(芯片级封装)、3D(三维立体封装)等先进封装形式。它介于产业链前道集成电路制造和后道封装测试之间,是晶圆制造环节的延伸,也是实施倒装封装工艺的基础及前提。例如在倒装封装中,凸块起到了连接芯片和基板的关键作用,代替了传统以引线作为键合方式的封装中的引线,实现了“以点代线”的突破,使得芯片与基板之间的连接更为紧凑和高效。

五、先进封装Bumping工艺技术的工作原理

1、凸块的制作过程

凸块制造过程一般是基于定制的光掩模进行的。以常见的制作流程为例,首先是在芯片表面进行再钝化处理,这一步骤是为了保护芯片表面免受后续工艺的影响,同时也为后续的金属沉积提供合适的表面状态。接着进行真空溅镀,通过在真空环境下,利用离子轰击靶材,使金属原子沉积在芯片表面,形成一层薄薄的金属膜,这层金属膜可能是凸块制作的基础层,如铜层等。然后是黄光工艺,黄光工艺类似于光刻技术,通过光刻胶的涂覆、曝光、显影等步骤,将设计好的凸块图案转移到芯片表面的金属膜上,确定凸块的位置和形状。之后进行电镀工艺,在已经确定好图案的区域进行电镀,使金属原子不断沉积,逐渐形成凸起的凸块结构。最后进行蚀刻工艺,去除不需要的金属部分,从而得到最终的凸块结构。不同类型的凸块在具体工艺参数和步骤上可能会有所差异,例如金凸块、铜柱凸块等在电镀的金属材料和工艺控制上会根据各自的需求进行调整。

2、芯片与基板的连接方式

在芯片与基板的连接方面,Bumping工艺技术提供了一种高效的“点连接”方式。以倒装芯片封装为例,在芯片上制作好凸块后,通过将芯片倒扣在基板上,使凸块与基板上对应的焊盘对准。然后可以采用热压合的方式,利用高温和压力使凸块与焊盘之间的金属原子相互扩散,形成良好的电气连接;或者也可以使用导电胶材,将凸块与线路上的引脚结合起来。这种连接方式相比于传统的引线键合方式具有很多优势。传统引线键合是通过金属丝将芯片和基板连接起来,连接线路较长,而Bumping工艺技术以点代线,大大缩短了连接电路的长度。例如在一些高频高速信号传输的芯片封装中,较短的连接路径可以减少信号传输延迟,提高信号传输的速度和质量。同时,凸块与基板之间的连接在机械性能上也更为稳定,能够承受一定程度的机械应力,提高了封装的可靠性。而且这种连接方式有利于提高芯片的端口密度,因为凸块可以在芯片表面更密集地排列,满足现代芯片对于高密度I/O接口的需求。

3、信号传输与电气特性

从信号传输的角度来看,Bumping工艺技术对提升芯片的电气性能有着重要作用。由于凸块提供了直接的电气连接点,信号在芯片和基板之间传输时,不需要经过较长的引线,减少了信号的衰减和失真。在高速数字信号传输中,信号的上升沿和下降沿时间很短,如果传输路径过长或者存在较多的寄生参数(如电感、电容等),就会导致信号波形的畸变,影响信号的完整性。而Bumping工艺技术的短连接路径和低寄生参数特性,使得信号能够更快速、准确地传输。例如在一些高性能处理器芯片的封装中,Bumping工艺技术能够确保数据在芯片和外部电路之间的高速传输,满足处理器对大量数据快速处理的需求。在电气特性方面,不同类型的凸块也有各自的优势。如铜柱凸块具有较好的导电和导热性能,能够有效地将芯片产生的热量传导出去,同时也能保证较低的电阻,减少电能在传输过程中的损耗;而金凸块在某些对化学稳定性要求较高的应用场景中,能够提供良好的抗腐蚀性能,确保长期稳定的电气连接。

六、先进封装Bumping工艺技术的优势和局限性

1、优势

一方面,Bumping工艺技术实现的芯片与基板的连接更为稳固。凸块与基板之间的连接是通过金属原子的扩散或者导电胶的粘结实现的,这种连接方式能够承受一定的机械应力,如在芯片受到振动、冲击或者温度变化引起的热膨胀和收缩时,凸块连接不容易松动或断裂。另一方面,由于凸块的存在,可以减少芯片与基板之间因接触不良而产生的电气故障。例如在一些汽车电子芯片的封装中,由于汽车行驶过程中的颠簸和温度变化较大,采用Bumping工艺技术可以提高芯片封装的可靠性,保证汽车电子系统的稳定运行。

许多凸块材料(如铜柱凸块等)具有良好的热传导性能。在芯片工作过程中,会产生大量的热量,如果不能及时有效地将热量传导出去,就会导致芯片温度过高,影响芯片的性能和可靠性。Bumping工艺技术中的凸块可以作为热量传导的通道,将芯片产生的热量快速传递到基板或散热器上。例如在一些高性能图形处理芯片(GPU)的封装中,通过Bumping工艺技术连接的芯片能够更有效地散热,保证芯片在高负荷运行时的稳定性。此外,良好的热传导性也有助于降低芯片内部的温度梯度,减少因热应力而产生的芯片损坏风险。

凸块代替了原有的引线,大大缩短了信号传输路径。信号传输路径的缩短带来了多方面的好处。首先,减少了信号延迟,在高速信号传输中,信号每经过一段传输线都会产生一定的延迟,而较短的路径可以显著降低这种延迟。例如在一些高频通信芯片的封装中,采用Bumping工艺技术可以将信号延迟降低到纳秒级甚至更小,提高了信号传输的速度和效率。其次,减少了信号传输过程中的干扰,因为较短的路径意味着较少的电磁干扰源,同时也降低了信号反射的可能性,使得信号完整性得到提高。这对于一些对信号质量要求极高的应用,如高速数据中心芯片的封装,非常关键。

Bumping工艺技术允许芯片拥有更高的端口密度。在传统的引线键合封装方式中,引线的尺寸和间距限制了芯片端口的密集程度。而Bumping工艺技术通过在芯片表面制作微小的凸块,这些凸块可以更紧密地排列,大大增加了单位面积上的连接点数量。例如,在一些先进的微处理器芯片封装中,通过Bumping工艺技术可以实现数千个甚至更多的I/O接口,满足了现代芯片功能日益复杂、对外部连接需求不断增加的要求。这对于缩小芯片封装尺寸、提高芯片集成度具有重要意义,使得更多的功能可以集成在更小的封装空间内,如在一些可穿戴设备的芯片封装中,小尺寸、高密度的封装能够满足设备对小型化和多功能的需求。

(1)实现高密度封装

(2)改善信号传输性能

(3)具备优良的热传导性

(4)提高封装可靠性

2、局限性

不同的凸块材料与芯片、基板材料之间可能存在兼容性问题。例如,某些凸块材料在与特定的芯片材料接触时,可能会发生化学反应,导致接触电阻增大或者连接可靠性下降。在一些复杂的多芯片封装或者异构集成封装中,可能会涉及到多种不同的材料体系,确保各种材料之间的兼容性是一个挑战。此外,在高温、高湿度等特殊环境下,材料之间的兼容性问题可能会更加突出,影响封装的长期稳定性。

凸块的制作需要高精度的工艺控制。例如,在凸块的电镀过程中,要精确控制电镀的厚度、均匀性等参数,如果电镀不均匀,可能导致凸块的高度不一致,影响芯片与基板的连接质量。在黄光工艺中,光刻胶的涂覆、曝光和显影等步骤也需要极高的精度,任何微小的偏差都可能导致凸块图案的缺陷。此外,随着芯片集成度的不断提高,对凸块的尺寸和间距要求越来越小,如现在一些先进封装要求凸块间距推进至10μm以下,这对工艺的稳定性和可重复性提出了巨大的挑战。工艺难度的增加不仅会导致产品的良率降低,还会增加制造成本和生产周期。

Bumping工艺技术的成本相对较高,这在一定程度上限制了它的广泛应用。首先,凸块制造过程涉及到复杂的工艺步骤,如定制光掩模、真空溅镀、电镀等,这些工艺需要高精度的设备和严格的工艺控制,设备的购置和维护成本高昂。例如,高精度的电镀设备和光刻设备价格昂贵,而且需要专业的技术人员进行操作和维护。其次,一些用于制作凸块的材料(如金等)本身成本较高,这也增加了整体的制造成本。在一些对成本较为敏感的大规模消费电子市场,如普通的低端手机芯片封装,过高的成本可能使得厂商更倾向于选择传统的封装技术。

(1)成本较高

(2)工艺难度较大

(3)材料兼容性问题

七、先进封装Bumping工艺技术的应用

因为本章节有讲到Bumping工艺技术在Flip-Chip(倒装芯片)中的应用情况,所以先着重讲一下:

1、Bumping工艺技术在Flip Chip(倒装芯片)中的应用

Flip Chip(倒装芯片)封装技术因其将芯片上的凸点翻转并安装于基板等封装体上而得名,是一种实现芯片与板(如基板)电气连接的互连技术,键合至基板或形成焊接凸点过程中不存在任何工艺方面限制;倒片封装凭借其优越的电气性能(不存在电气连接I/O引脚数量和位置限制,电信号传输路径短于引线键合),已经很大程度上取代了引线键合。倒片封装体中Bumping(凸点)工艺技术是基于晶圆级工艺而完成的,而后续工序则与传统封装工艺相同。

2、在移动设备芯片封装中的应用

在现代智能手机和平板电脑等移动设备中,Bumping工艺技术发挥着重要作用。以智能手机中的应用处理器(AP)芯片为例,这些芯片功能复杂,需要与多个外部组件(如内存、基带芯片、传感器等)进行高速通信和数据传输。Bumping工艺技术的高密度端口特性能够满足AP芯片众多的I/O接口需求,实现与其他芯片的高效连接。例如,通过Bumping工艺技术将AP芯片与高速内存芯片进行倒装封装连接,可以大大提高数据传输速度,从而提升整个手机系统的运行速度。同时,移动设备对小型化和轻薄化的要求极高,Bumping工艺技术有助于实现芯片的小尺寸封装,如采用锡凸块或铜柱凸块技术,可以使芯片封装在满足性能要求的同时,体积更小、重量更轻,符合移动设备的设计需求。此外,在移动设备的摄像头芯片封装中,Bumping工艺技术也能提高芯片与基板之间的连接可靠性,保证摄像头在各种环境下(如拍摄过程中的振动、温度变化等)都能正常工作。

3、在高性能计算芯片封装中的应用

在高性能计算领域,如数据中心的服务器芯片和超级计算机芯片等,Bumping工艺技术是实现高性能封装的关键。对于服务器芯片而言,大量的数据处理需要芯片具备高速的信号传输能力和高端口密度。Bumping工艺技术通过缩短信号传输路径和提高端口密度,能够满足服务器芯片对大量数据快速传输的需求。例如,在一些多核处理器芯片的封装中,采用Bumping工艺技术可以实现各个核心之间以及核心与外部存储、网络接口等的高速连接,提高整个服务器系统的计算性能。在超级计算机芯片中,Bumping工艺技术的优良热传导性有助于解决芯片高功率运行时的散热问题。由于超级计算机芯片运算速度极快,产生的热量巨大,良好的热传导通道可以保证芯片在安全的温度范围内运行,避免因过热而导致的性能下降或芯片损坏。

4、在汽车电子芯片封装中的应用

汽车电子系统对芯片封装的可靠性要求极高,因为汽车行驶过程中会面临各种复杂的环境条件,如振动、高温、低温、潮湿等。Bumping工艺技术在汽车电子芯片封装中的应用主要体现在提高可靠性方面。例如,汽车发动机控制单元(ECU)芯片需要在高温、振动的环境下稳定工作,采用Bumping工艺技术可以确保芯片与基板之间的稳固连接,减少因振动导致的电气连接故障。同时,在汽车的自动驾驶系统芯片封装中,Bumping工艺技术的信号传输性能优势可以保证芯片与传感器、控制器之间的高速、稳定通信,提高自动驾驶系统的安全性和可靠性。而且,随着汽车电子朝着智能化、集成化方向发展,Bumping工艺技术的高密度封装特性也有助于在有限的空间内集成更多的功能芯片,如将多个传感器芯片、控制芯片等集成封装在一起,提高汽车电子系统的集成度。

八、先进封装Bumping工艺技术的未来发展趋势

1、朝着更小尺寸和更高密度发展

随着芯片技术的不断进步,对Bumping工艺技术的尺寸和密度要求也越来越高。未来,凸块的尺寸将进一步缩小,间距也将更小。例如,目前已经有研究在探索将凸块间距推进至10μm以下甚至更小的尺寸,这将使得芯片能够在单位面积上集成更多的I/O接口,进一步提高芯片的集成度。这种趋势在人工智能芯片、5G通信芯片等对高性能和高集成度有强烈需求的领域尤为明显。更小尺寸和更高密度的Bumping工艺技术将有助于实现芯片的小型化,满足未来电子设备不断缩小体积的需求,同时也能提高芯片的性能,如提高信号传输速度、降低功耗等。为了实现这一目标,需要不断研发新的工艺技术和设备,提高工艺的精度和稳定性,如开发更先进的光刻技术用于凸块图案的制作,以及更精确的电镀和蚀刻技术来控制凸块的尺寸和形状。

2、与其他先进封装技术的融合

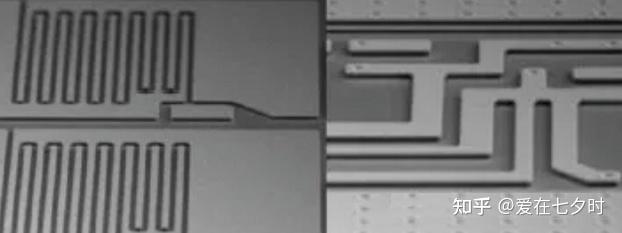

Bumping工艺技术将与其他先进封装技术更加紧密地融合。例如,与晶圆重布线技术(RDL)的结合将更加深入。RDL技术可以对原来设计的集成电路线路接点位置(I/O Pad)进行优化和调整,与Bumping工艺技术相结合后,可以进一步提高芯片的电气性能和封装灵活性。在3D封装技术中,Bumping工艺技术将成为实现芯片垂直互连的重要组成部分。通过在不同层的芯片上制作凸块,实现芯片之间的垂直连接,从而构建三维的芯片集成结构,提高芯片的集成度和性能。此外,Bumping工艺技术还将与系统级封装(SiP)技术相结合,在一个封装内集成多个不同功能的芯片,形成一个完整的系统。这种融合将使得封装后的芯片具有更高的性能、更小的尺寸和更低的成本,满足未来复杂电子系统对芯片封装的需求。

总之,在目前的市场环境中看来,Bumping工艺技术的应用主要集中在FC(倒装芯片)领域。根据市场研究机构Yole的数据显示,预计2024到2028年,2.5/3D堆叠、层压基板ED封装和扇出型封装的年复合增长率均将超过30%。尤其在AI、高性能计算(HPC)、数据中心等领域,Bumping工艺技术展现出了巨大的市场潜力。

写在最后面的话

随着电子产品向更高集成度和功能多样化发展,Bumping工艺技术的未来将呈现出更多的创新可能。无论是在手机、汽车等应用场景,还是在更前沿的AI及物联网设备中,Bumping工艺技术都将发挥重要的作用,助力电子产品实现更高的性能与更大的市场价值。

总体来看,Bumping工艺技术在半导体封装中的应用潜力巨大,其高效连接和优良可靠性为电子产品的发展带来了新机遇。我们建议行业各界持续关注这一技术的演进,抓住其带来的市场机遇。同时,普通消费者也可以通过了解这些先进技术,增加对电子产品性能的认知,从而做出更明智的消费决策。

免责声明

【我们尊重原创,也注重分享。文中的文字、图片版权归原作者所有,转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时私信联系,我们将第一时间跟踪核实并作处理,谢谢!】

审核编辑 黄宇

-

半导体

+关注

关注

339文章

31252浏览量

266613 -

封装

+关注

关注

128文章

9333浏览量

149053

发布评论请先 登录

半导体先进封装之“2.5D/3D封装技术”的详解;

半导体金线键合(Gold Wire Bonding)封装工艺技术简介;

热压键合工艺的技术原理和流程详解

半导体封装Wire Bonding (引线键合)工艺技术的详解;

半导体芯片封装“CoWoS工艺技术”的详解;

关于先进碳化硅(Sic)功率半导体封装工艺技术的详解;

半导体“封装过程”工艺技术的详解;

半导体“刻蚀(Etch)”工艺技术的详解;

半导体先进封装“重布线层(RDL)”工艺技术的详解;

半导体“光刻(Photo)”工艺技术的详解;

晶圆级封装(WLP)中Bump凸点工艺:4大实现方式的技术细节与场景适配

SOI工艺技术介绍

半导体先进封装“Bumping(凸点)”工艺技术的详解;

半导体先进封装“Bumping(凸点)”工艺技术的详解;

评论