CDM测试是一种模拟带电集成电路自身快速静电放电的可靠性检测方法。

一、CDM模型核心概念

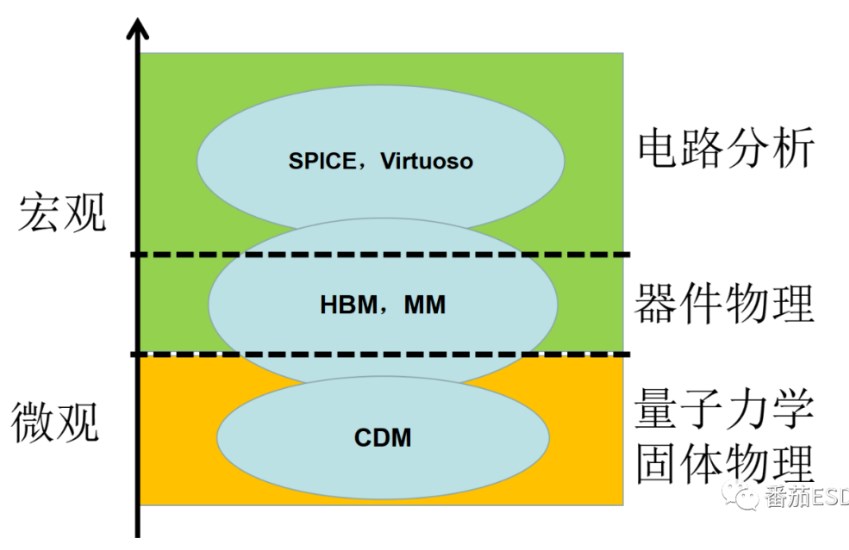

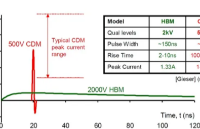

CDM(带电设备模型)是ESD(静电放电)测试中的一种关键模型,区别于HBM(人体模型)和MM(机器模型)。它专门模拟电子元器件(如芯片)在生产、运输或处理过程中因摩擦等因素自身累积静电,随后在接触接地导体时发生的快速放电现象。其最显著的特征是放电速度极快,电流上升时间在亚纳秒级别(0.1-0.5纳秒),整个过程在数纳秒内完成,导致其产生的瞬时峰值电流远高于其他ESD模型。

二、CDM测试装置

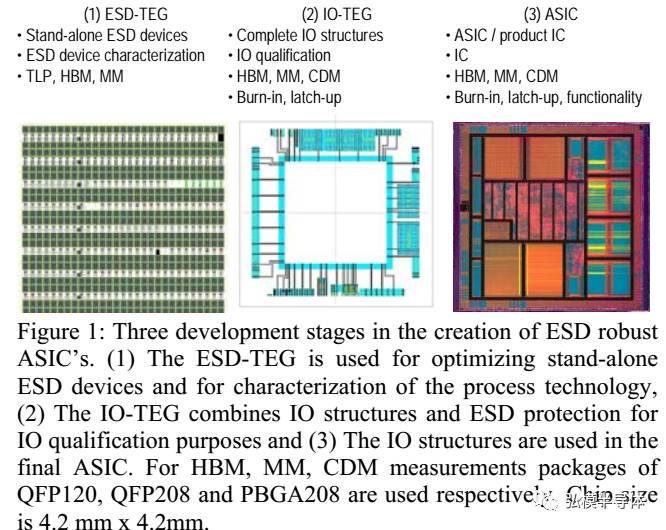

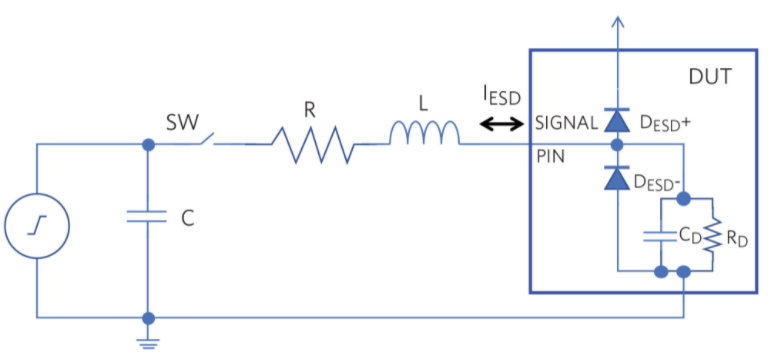

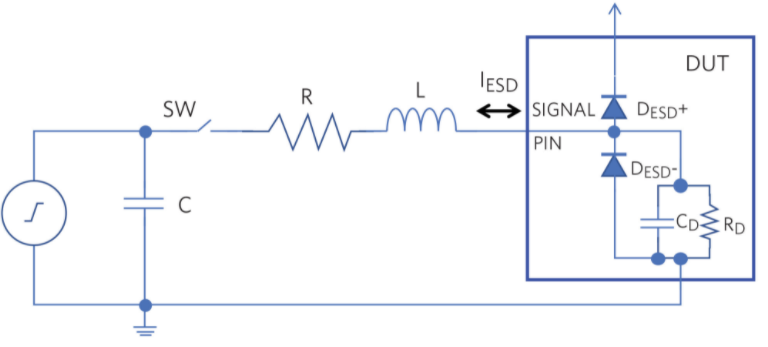

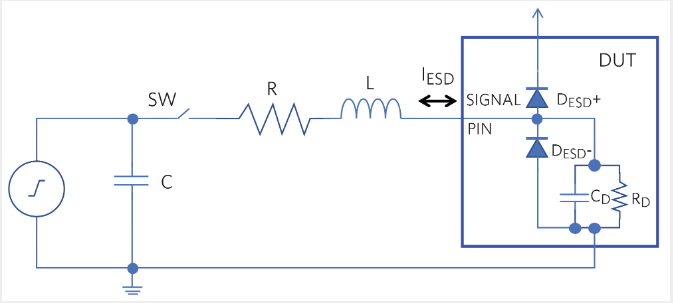

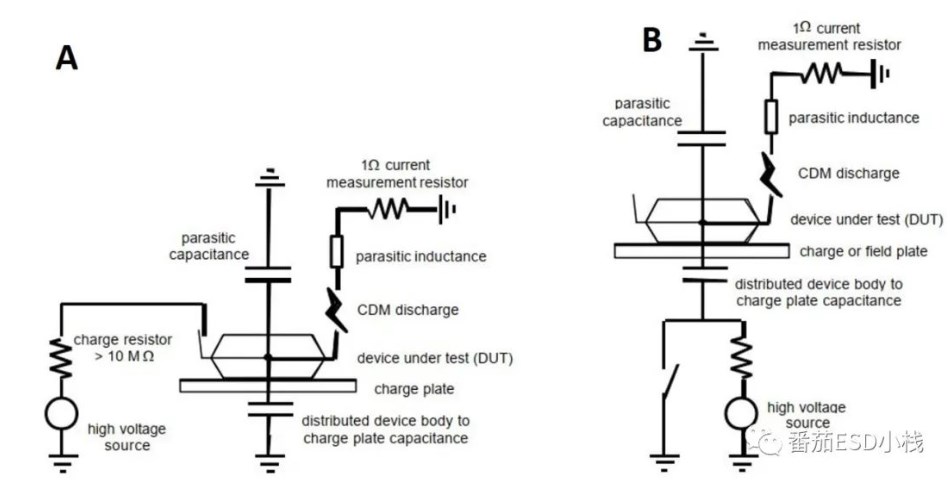

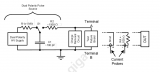

CDM测试旨在在可控的实验室环境中复现上述放电事件。CDM测试装置主要由一个与高压电源相连的充电板Field Plate和一个接地的Pogo pin构成,Pogo pin能够在待测IC(DUT)的引脚间移动,以模拟实际的ESD事件。图1展示了实际的测试模块,而图2则为等效电路图,其中CDUT代表DUT与场板之间的电容,CDG代表DUT与地平面之间的电容,CFG代表场板与地平面之间的电容。

三、CDM测试规范

在CDM测试规范统一化之前,存在多个参考标准,包括JESD22-C101、ESDA S5.3.1、AEC Q100-011和EIAJ ED-4701/300-2等,这些标准在校准平台、示波器带宽和波形验证参数等方面存在差异。

技术进步带来了晶体管性能的提升和更高的IO性能需求。随着IC芯片对高速IO的需求增加,以及在单一封装中集成更多功能的趋势,封装尺寸的增加对维持JEP157中推荐的CDM放电级别提出了挑战。考虑到不同测试设备的充电电阻差异,ESD协会(ESDA)在2020年的路线图中建议可能需要重新评估CDM放电目标级别。

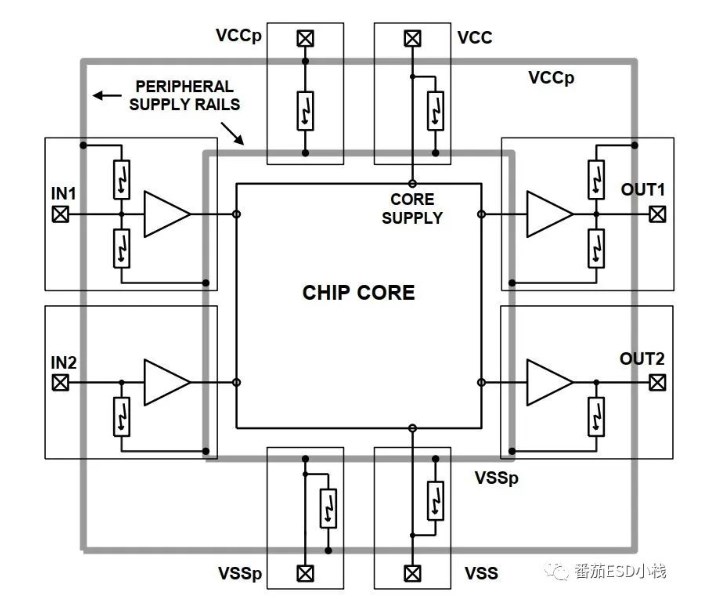

随着电子设备性能的提高,对ESD保护的需求也在增加,如图3和图4所示,分别展示了历年CDM放电目标级别的变化和CDM ESD目标级别的预期分布变化。通过金鉴的测试服务,客户能够更准确地掌握产品的ESD性能,确保产品在实际使用中的可靠性和稳定性。

四、CDM测试标准调整的原因

1. 封装因素:IC元件引脚数量和封装尺寸的显著增加

在固定的预充电压下,限制了芯片的CDM放电能力,尤其是封装尺寸。引脚数量和封装尺寸的增加意味着IC能够存储更多的电荷,导致CDM放电时峰值电流迅速上升。因此,在相同的峰值电流限制下,引脚数量和尺寸的增加会导致CDM能力的降低。

2.工艺因素: IC工艺技术的进步导致CDM放电能力的降低

随着工艺尺寸的缩小,CDM放电能力显著降低。工艺尺寸的缩小使得有源器件变得更小、更脆弱,金属互连变得更薄、电阻性增加,降低了ESD保护电路的鲁棒性。这使得在相同的电流水平下,实现CDM保护变得更加困难。

3. 性能因素:随着高速数字、射频模拟和其他性能敏感引脚的混合信号IC变得更加普遍,对ESD保护提出了新的要求

在高频电路中,直接将ESD保护器件连接到I/O引脚可能会导致射频功能的显著降低,因此需要将射频保护结构与核心电路隔离。

这通常通过在ESD保护器件和引脚之间插入并联电感/电容网络来实现,该网络在低频ESD事件中提供接近零的阻抗,在正常高频操作中提供高阻抗。

-

集成电路

+关注

关注

5446文章

12473浏览量

372749 -

ESD

+关注

关注

50文章

2377浏览量

178898 -

CDM

+关注

关注

0文章

32浏览量

12523 -

静电测试

+关注

关注

0文章

20浏览量

9701

发布评论请先 登录

新ANSI/ESDA/JEDEC JS-002 CDM测试标准概览

什么是小尺寸集成电路CDM测试?

关于静电保护(ESD) 中的CDM需求的发和应用

日本CDM 8.0正式版已经发布下载

HBM、MM和CDM测试的基础知识

HBM、MM和CDM测试的基础知识

浅谈CDM的原因与机理

CDM防护措施以及设计思路

季丰电子CDM测试机已全部配备高带宽的6G示波器

CDM试验对电子器件可靠性的影响

什么是CDM静电测试?

什么是CDM静电测试?

评论