主要的ESD测试是人体模型(HBM),机器模型(MM)和充电设备模型(CDM)。

有许多成熟的模型可以针对ESD事件测试半导体器件的可靠性,以确保有效性和可靠性。主要的ESD测试是人体模型(HBM),机器模型(MM)和充电设备模型(CDM)(图1)。

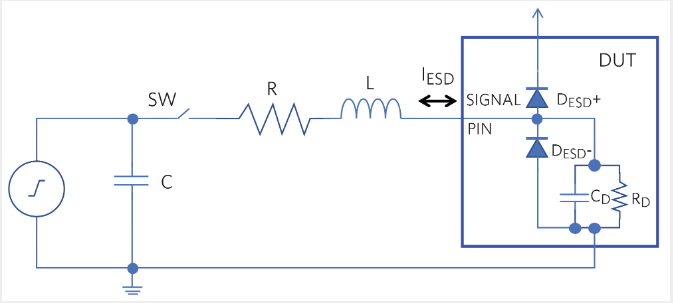

图1.用于 HBM、MM 和 CDM 测试的 ESD 模型。

JEDEC 标准确保 ESD 测试的有效性和可靠性。这三个测试的测试配置(图 1)有五个要素:V静电放电、C、SW、R 和 L。输入V静电放电在开关闭合 (SW) 之前对电容器 C 进行电压充电。随着SW的闭合,ESD灯具的输出阻抗(R和L)发送V静电放电信号,转换为电流(I静电放电) 到被测设备 (DUT) 中。现在的ESD电流流过DUT的ESD二极管;D静电放电+和 D静电放电-。如果其中一个或两个ESD二极管发生故障或缺失,则电流(I静电放电),从这个ESD事件中将找到另一条路径,该路径多次灾难性地进一步进入DUT电路。

公式1表示图1测试电路的数学传递函数。

公式 1

此配置会导致信号引脚接合处发生瞬时ESD事件,以模拟三个ESD测试信号事件之一。DUT 信号引脚是输入或输出器件引脚。对于这三个ESD测试,V的值静电放电、C、R 和 L 组件变化以实现实际的 ESD 事件(表 1)。

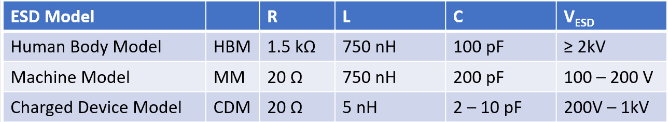

表 1.HBM、MM、CDM 的可持续发展教育活动

在表1中,这三种型号归结为串联RLC电路和脉冲发生器,但型号之间的电路值和脉冲特性不同。然而,所有三项测试都会产生一个短而明确的ESD脉冲,从而产生电流(I静电放电)的水平与实际可持续发展教育事件期间的水平相当。

人体模型 (HBM) 表征了电子设备对静电放电 (ESD) 损坏的敏感性。人体模型是一种模拟人类从手指到被测设备 (DUT) 再到地面的 ESD 路径的模型。静电放电电源电压(V静电放电) 为测试电路中的电容器充电。标准 HBM 测试包括 ±2 kV 的电源电压、1 至 10 M?的高值电阻和 100 pF 的电容。

机器模型 (MM) 的目的是创建一个更严格的 HBM 测试。电荷电容(C)故意变大(200 pF),电荷源电阻值非常低;0 至 10Ω。这种低阻值电阻允许ESD源提供比HBM型号更高的电流。尽管该模型的目的是表征与最终用户电子组件相关的机器ESD事件,但它并不打算体现半导体最终测试和处理中使用的处理程序。

充电设备模型 (CDM) 可以作为一次性普遍应用的 MM 的替代测试。该CDM测试模拟IC封装或制造设备在最终生产操作中处理设备时累积的电荷。在制造过程中,设备处理设备中存在产生静电的机会。这是IC器件从防静电管或测试处理器上滑下来的地方,这些防静电管或测试处理器会积聚电荷。

当前(I静电放电) 注入 DUT 会产生热量。产生的热量大小取决于峰值ESD脉冲电压、电容和DUT电阻。在 HBM 测试中,IC 故障模式通常表现为栅极氧化物、触点尖峰和结损坏。

静电放电测试比较

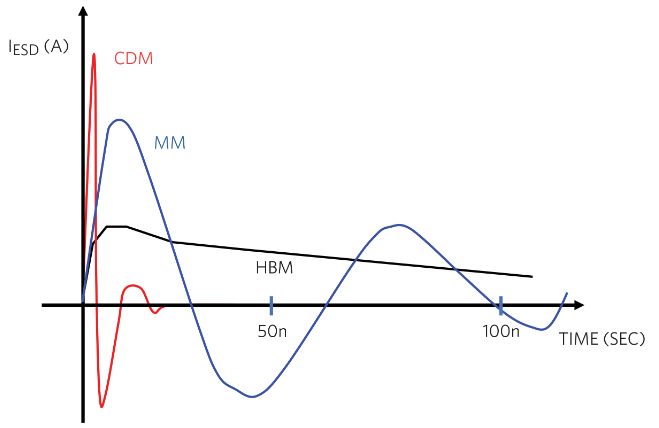

这三个测试的类似上升时间约为 10 ns,但 HBM 和 MM 测试的总持续时间比 CDM 模型高出约 200 ns(图 2)。

图2.CDM、MM 和 HBM ESD 电流与时间的关系测试。

图2显示了电流(I静电放电) HBM、MM 和 CDM ESD 测试的波形特性。通常,HBM ESD 测试的应力水平大约是 MM ESD 测试条件的 10 倍。此外,HBM 测试的保护电压水平通常为 2 kV,而 MM 测试的保护电压水平为 200 V,CDM 测试的保护电压水平为 500 V。CDM、HBM 或 MM 之间没有相关性。因此,HBM 和 CDM 测试通常用于 ESD 保护电路测试。I 的持续时间越长静电放电导致片上ESD结构过热增加。HBM 和 MM 测试失败通常表现在栅极氧化物或结部损坏中。

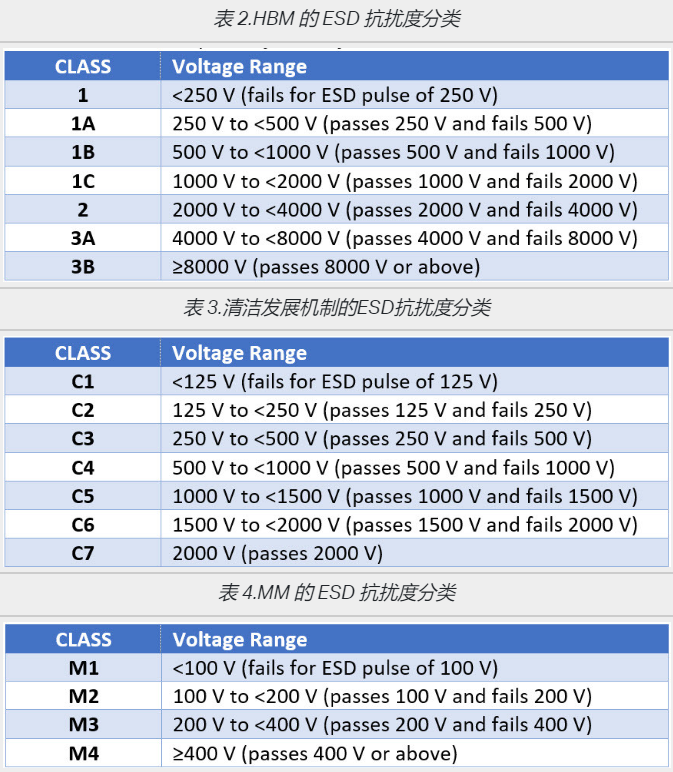

表 2、3 和 4 显示了 HBM、CDM 和 MM ESD 抗扰度分类。

审核编辑:郭婷

-

ESD

+关注

关注

50文章

2425浏览量

180425 -

半导体

+关注

关注

339文章

31248浏览量

266589

发布评论请先 登录

探索CDM10VD:灵活的0 - 10V调光解决方案

Infineon CDM10VD:灵活的0 - 10V调光解决方案

CW32L083RBT6在手机APP无线温控器应用优势

CW32抗干扰能力有多强?

存储狂飙与HBM扩产潮下,高端芯片烧录的“速度与精度”终极博弈

HBM量价齐飞,UFS加速普及:存储狂飙下的“最后质检”攻坚战

CW32系列MCU在温控器应用的优势

AI大算力的存储技术, HBM 4E转向定制化

ESD测试的详细解释

HBM技术在CowoS封装中的应用

CDM试验对电子器件可靠性的影响

HBM应用在手机上,可行吗?

季丰电子ESD实验室新增VFTLP测试能力

HBM、MM和CDM测试基础

HBM、MM和CDM测试基础

评论