引言

在 5G 乃至未来 6G 通信网络中,基站作为核心基础设施,其内部射频拉远单元(RRU)与基带处理单元(BBU)之间的数据传输效率,直接决定了通信质量与网络性能。而 CPRI(通用公共无线电接口)协议,正是保障这一传输过程高效、稳定的关键技术标准。今天,我们就带大家深入解读西安智多晶微电子有限公司的 CPRI 协议演示方案,看看这项技术如何为无线通信赋能。

CPRI 协议Demo介绍

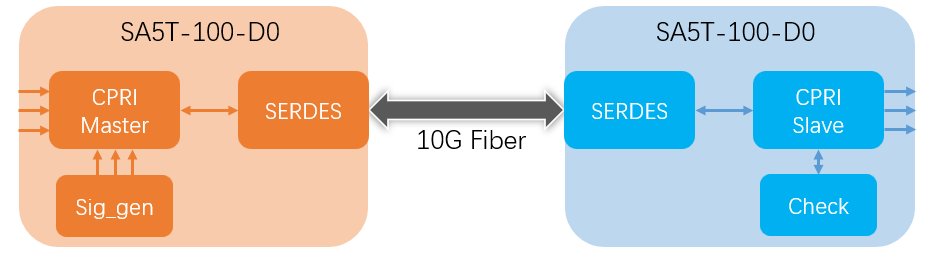

CPRI Demo中的核心模块CPRI基于智多晶的SERDES IP核实现信号的高速传输,在Seal 5000高性能FPGA系列SA5T-100-D0可以支持到10Gbps。Demo使用了两块SA5T-100-D0开发板,一块作为主端,另一块作为从端。两块开发板之间通过FMC子板连接的光模块进行交互,负责将FPGA输出的电信号转换为光信号,或接收光信号并还原为电信号,实现10Gbps速率的光传输。板载100MHz差分时钟晶振作为整个系统的时钟源,内置SERDES的CDR技术保障了数据传输的质量。

Demo传输系统示意图

在Demo演示环境中,CPRI主端利用信号生成模块来模拟用户并行输入信号,CPRI Master模块会与SERDES之间进行时钟、数据和控制信号的交互。串行数据通过光模块传输至另一开发板的SERDES,同样与CPRI从端进行交互。CPRI Slave模块解析并恢复主端发送的数据,然后Check模块会对输出的数据进行校验,以提示是否有比特错误。

Demo效果

信号生成模块产生4通道、12位I/Q信号,通过从端的错误检测和计数器,对接收到的数据进行误码率评估,从端能够正确恢复主端发送数据,实测误码率为0。

Demo特性

支持4通道、12位并行差分数据输入;

支持10Gbps数据传输;

能够恢复数据和时钟;

具备数据校验功能;

应用场景

6.4G、8G和10G速率的光纤数据传输;

基带信号与射频信号的高速、稳定交互;

ADC多通道输入信号的高速传输;

-

射频

+关注

关注

106文章

5947浏览量

172806 -

CPRI

+关注

关注

1文章

12浏览量

9114 -

智多晶微电子

+关注

关注

0文章

16浏览量

216

原文标题:“芯”技术分享 | 智多晶CPRI协议DEMO,解锁基站数据传输新可能

文章出处:【微信号:智多晶,微信公众号:智多晶】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

智多晶Bit_CDR Demo介绍

智多晶AXI视频通讯DEMO方案介绍

智多晶eSPI_Slave IP介绍

智多晶FIFO_Generator IP介绍

智多晶LPC_Controller IP介绍

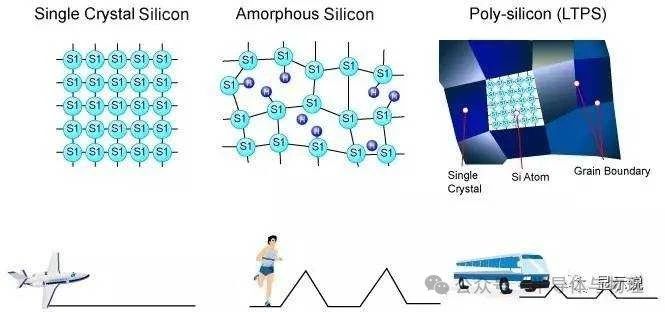

LPCVD方法在多晶硅制备中的优势与挑战

芯片制造中的多晶硅介绍

单晶圆系统:多晶硅与氮化硅的沉积

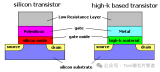

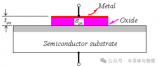

为什么采用多晶硅作为栅极材料

智多晶CPRI协议DEMO介绍

智多晶CPRI协议DEMO介绍

评论