引言

在高速串行通信中,CDR(Clock-Data-Recovery)时钟与数据恢复功能起着关键作用。CDR电路可以从数据流中同时提取出数据和时钟,链路上不再需要伴随信号发送随路时钟,大量节省IO资源和布线成本,并且完全消除在高速通讯中因数据和时钟相位偏差导致的传输错误,对长距离传输友好;采用了CDR电路的系统,数据收发两端在时钟系统上可以完全解耦,带来非常大的系统灵活性。

智多晶FPGA通过普通逻辑和IO资源实现了CDR应用的支持,在上限200~250Mbps[2]速率范围内提供了更为有力的通讯技术方案。

Bit CDR Demo介绍

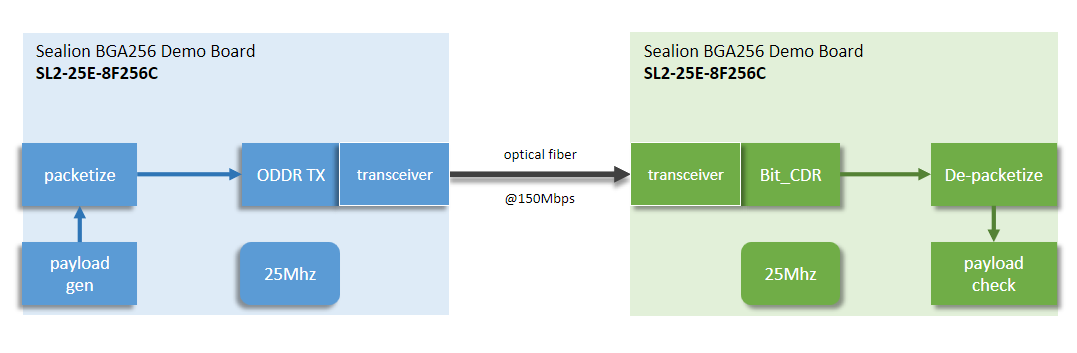

Bit_CDR Demo中的核心模块CDR基于过采样原理,在Sealion器件上可以支持到200Mbps。Demo使用了两张基于Sealion 25K FPGA的电路板,其中一张板做发送端,另一张板作为接收端。开发板上各有一对双波长光模块相互作为收发,光模块之间使用20KM的光纤连接,模拟真实应用环境。两张开发板工作于自己晶振产生的独立时钟,数据速率定为150Mbps。

Demo系统示意框图

考虑到Demo演示的合理性,整体技术方案上选择以IEEE802.3协议为框架来搭建。使用IEEE802.3协议,可以保证产生的串行数据在传输过程中可以保持DC平衡,编码后不会出现长0和长1码,还具备较强的错误识别能力。由于IEEE802.3协议框架在应用上的通用性,demo本身也具备足够的应用参考价值。

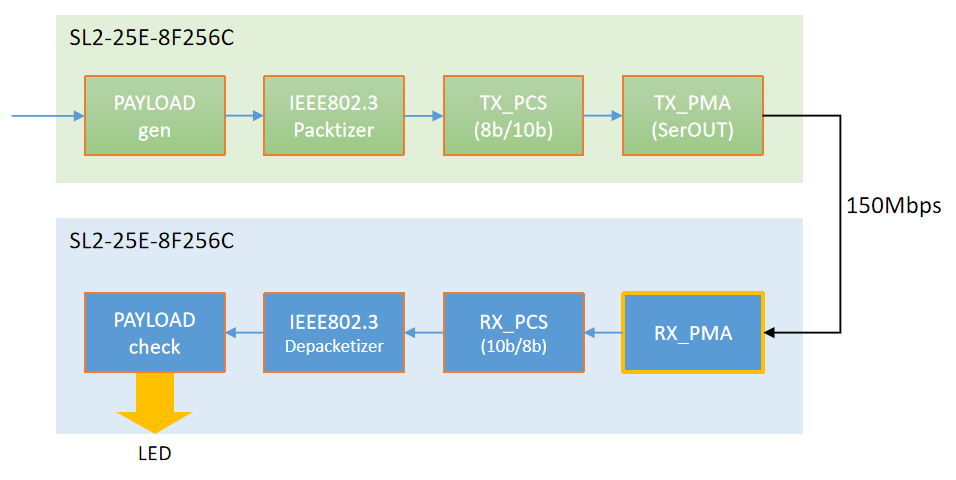

Bit_CDR_DEMO技术框图

发送端:数据生成模块自动生成有规律的报文数据;报文经过以太网IEEE802.3协议模块打包;在TX_PCS模块进行8b10b编码;在TX_PMA模块以150Mbps速率串化输出至光模块。

接收端:光模块接收下来的差分信号,在RX_PMA模块中完成信号识别和采样、数据窗的同步判断、10bit并行数据和时钟的恢复;在RX_PCS模块中完成8b10b解码;在以太网IEEE802.3协议模块进行payload解包,最后在PAYLOAD check模块对解出的数据包进行规律正确性检查并输出报错。

Demo效果

在上述的TX-RX环路平台上,我们通过错误统计计数器和计时器,对误码率进行了简单的实测和评估,误码率低于10^-12。

Demo特性

采用过采样方式实现CDR功能

能够恢复数据和时钟

可灵活支持串并转换数据格式

串并转换特征码(comma word)可配置

通过IEEE802.3链路验证

支持链路状态检测和管理控制

误码率低于10^-12 [1]

应用场景

200M~250Mbps[2]速率以内的单lane通讯。

工业设备子卡与主板之间的多节点背板通讯(M-LVDS)

长距离通讯光端机

应用中针对传输phy芯片的cost-down

[注]

[1]基于20Km光纤和150Mbps速率条件下测得。

[2]速率上限取决于器件。

-

FPGA

+关注

关注

1656文章

22291浏览量

630401 -

串行通信

+关注

关注

4文章

602浏览量

36991 -

时钟系统

+关注

关注

1文章

124浏览量

12785

原文标题:“芯”技术分享 | 智多晶Bit_CDR Demo

文章出处:【微信号:智多晶,微信公众号:智多晶】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

什么使集成CDR的误码率有益?

国产智多晶FPGA介绍及应用

AT32F415 Audio 24bit实例demo

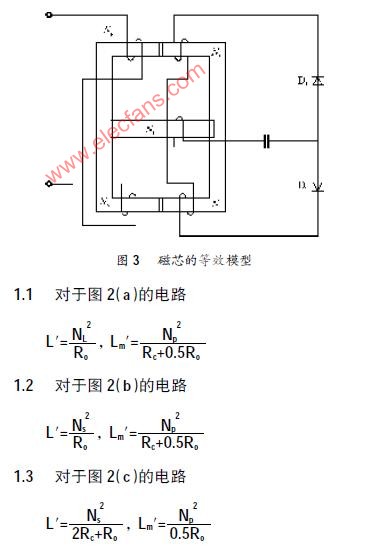

基于磁集成的CDR电路

HASS试验对CDR的PPM容忍度要求

Demo介绍UART 9bit通信的同步帧方式

LTC6115 Demo Circuit - Current and Voltage Sensor Monitor Circuit for 16-Bit ∆Σ ADC

智多晶AXI视频通讯DEMO方案介绍

智多晶Bit_CDR Demo介绍

智多晶Bit_CDR Demo介绍

评论