CDC7005:高性能时钟合成器与抖动消除器

在电子工程师的日常工作中,时钟合成器与抖动消除器是至关重要的元件,它们能够为系统提供精准且稳定的时钟信号。今天要给大家介绍一款性能卓越的产品——德州仪器(Texas Instruments)的CDC7005,一款3.3 - V高性能时钟合成器与抖动消除器。

文件下载:cdc7005.pdf

一、产品概述

CDC7005是一款高性能的时钟同步器,具备低相位噪声、低偏移等出色特性,能够将压控晶体振荡器(VCXO)的频率与参考时钟同步。其可编程的预分频器M和N为参考时钟与VCXO的频率比提供了高度的灵活性,计算公式为:$VCXO_IN / REF_IN =(NxP) / M$,VCXO_IN时钟的工作频率最高可达800 MHz。

该器件采用3.3 - V电源供电,拥有两个时钟输入(VCXO_IN和REF_IN),能够同步高达800 MHz的频率,并支持五个差分LVPECL输出,每个输出频率可通过x1、/2、/4、/8、/16进行选择,且所有输出均能保持同步。此外,它还集成了低噪声运算放大器(OPA),可用于外部低通滤波器,能够有效筛选抖动,具有低相位噪声的特点。产品支持可编程延迟用于相位调整、预分频器环路带宽调整,并且可通过SPI控制进行分频设置。在电源方面,当$V_{CC} < 1.5 V$时,上电控制会使LVPECL输出处于三态。

CDC7005提供两种封装形式,分别是64 - 引脚的BGA(0.8 mm间距 - ZVA)或48 - 引脚的QFN(RGZ),适用于工业温度范围(–40°C至85°C)。

二、引脚功能与结构

2.1 引脚分配

| CDC7005的引脚众多,不同引脚具有不同的功能。例如,AVCC为3.3 - V模拟电源供电引脚,CP_OUT为电荷泵输出引脚,CTRL_LE、CTRL_CLK和CTRL_DATA则是SPI接口的控制引脚,用于对器件进行配置。详细的引脚分配可参考下面的表格: | PIN | BGA | QFN | TYPE | DESCRIPTION |

|---|---|---|---|---|---|

| AVCC | C3, C4, C5, C6, C7 | 27, 30, 32, 38, 39 | Power | 3.3 - V模拟电源供电 | |

| CP_OUT | A4 | 31 | O | 电荷泵输出 | |

| CTRL_LE | A1 | 36 | I | LVCMOS输入,用于SPI的控制负载使能 | |

| CTRL_CLK | A2 | 35 | I | LVCMOS输入,SPI的串行控制时钟输入 | |

| CTRL_DATA | A3 | 33 | I | LVCMOS输入,SPI的串行控制数据输入 | |

| ...... | ...... | ...... | ...... | ...... |

2.2 功能框图

CDC7005的功能框图展示了其内部结构和信号流向。它主要由PFD电荷泵、可编程分频器、逻辑控制单元、LVPECL输出模块等部分组成。参考时钟REF_IN和VCXO时钟VCXO_IN经过一系列处理后,通过LVPECL输出端输出同步的时钟信号。OPA模块用于外部低通滤波器,可有效减少抖动。

三、SPI控制接口

CDC7005的串行接口是一个简单的SPI兼容接口,用于对器件的寄存器进行写入操作。它由三根控制线(CTRL_CLK、CTRL_DATA和CTRL_LE)组成,共有四个32位宽的寄存器,可通过传输字的两个最低有效位(bit 0和bit 1)进行寻址。每个传输的字必须为32位,且从最高有效位(MSB)开始。

在初始化时,建议在电源上电且NPD变为高电平后,立即对Word 0、Word 1、Word 2和Word 3进行编程。SPI传输通过CTRL_LE的下降沿启动,当CTRL_LE为高电平时,数据无法传输;当CTRL_LE为低电平时,可进行数据写入。数据需在CTRL_DATA上提供,并在CTRL_CLK的上升沿之前保持稳定。传输结束于CTRL_LE的上升沿,此时新的字将异步传输到内部寄存器。

四、寄存器功能

4.1 寄存器编程

CDC7005的四个32位寄存器(Word 0、Word 1、Word 2和Word 3)分别控制着器件的不同功能。例如,Word 0控制着参考分频器M、PFD脉冲宽度、CP电流设置、输出三态等功能;Word 1控制着VCXO分频器N、MUX选择、CP调节方向等功能。详细的寄存器位功能可参考文档中的表格。

4.2 编程示例

在实际应用中,我们需要根据具体需求对寄存器进行编程。例如,如果需要设置参考分频器M的值为128,可通过Word 0中的M0 - M9位进行设置。假设我们使用SPI接口进行编程,代码示例如下(这里只是一个简单的示意,实际代码需根据具体的硬件平台进行调整):

// 假设SPI通信函数已经实现

// 设置Word 0的M0 - M9位为对应的值(128的二进制编码为00000111111)

uint32_t word0_value = 0x000000FF; // 根据实际需求修改

// 发送Word 0到CDC7005

SPI_SendData(word0_value);五、性能指标

5.1 电气参数

CDC7005在电气性能方面表现出色,在推荐的工作条件下,其电源电流ICC典型值为230 mA($f{VCXO} = 245 MHz$,$f{REF_IN} = 30 MHz$,$V{CC} = 3.6 V$,$AV{CC} = 3.6 V$,$f{PFD} = 240 kHz$,$I{CP} = 2 mA$)。LVCMOS输入电流在$V{I} = 0 V$或$V{CC}$时,典型值为±5 μA;LVPECL输出的差分输出电压在10 ≤ $f_{OUT}$ ≤ 800 MHz时,典型值为500 mV。

5.2 噪声性能

在噪声方面,CDC7005在不同频率下的相位噪声表现良好。例如,在30.72 MHz参考时钟下,10 Hz时的相位噪声典型值为−77 dBc/Hz,100 Hz时为−95 dBc/Hz,1 kHz时为−118 dBc/Hz。在245.76 MHz VCXO时钟下,相位噪声也能满足大多数应用的需求。

5.3 时序要求

CDC7005对输入信号的时序有一定要求。REF_IN时钟频率范围为3.5 - 180 MHz,上升和下降时间在20% - 80% $V{CC}$时最大为4 ns,占空比为40% - 60%。VCXO_IN和VCXO_INB时钟频率范围为10 - 800 MHz,在80 MHz - 800 MHz时,上升和下降时间在20% - 80% $V{INPP}$时最大为3 ns,占空比为40% - 60%。

六、应用场景

6.1 高速ADC和DAC时钟生成

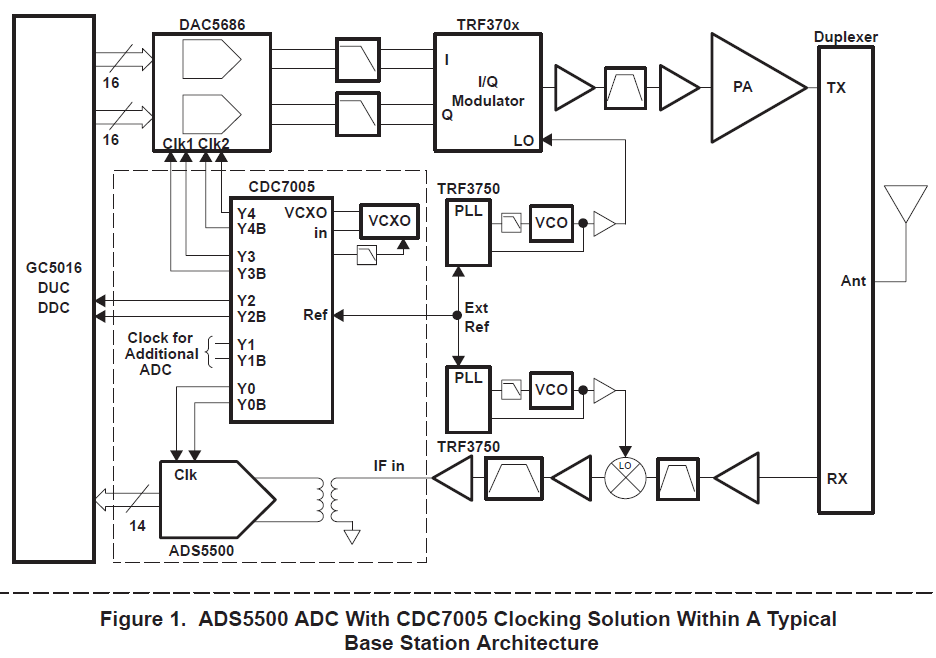

CDC7005凭借其出色的相位噪声性能,成为高速ADC和DAC的理想采样时钟发生器。特别是对于集成了插值滤波器的新型高速DAC,如DAC5686,CDC7005能够提供满足其要求的时钟信号。在3G系统中,常见的高速DAC采样率为245.76 MSPS,通过四倍插值,数字输入所需的数据速率可降低至61.44 MSPS,这一数据速率可由数字端轻松支持。CDC7005能够生成数据输入时钟和DAC时钟,并保证两个时钟信号的边缘相位在±500 ps内对齐,确保数据正确锁存。

6.2 其他应用

除了高速ADC和DAC时钟生成,CDC7005还可应用于其他对时钟信号要求较高的领域,如通信设备、测试仪器、数据采集系统等。其低相位噪声和低偏移特性能够为这些系统提供稳定、精准的时钟信号,提高系统的性能和可靠性。

七、总结

CDC7005是一款功能强大、性能卓越的时钟合成器与抖动消除器,具有高度的灵活性和稳定性。其丰富的功能和出色的性能使其在众多领域都有广泛的应用前景。在实际设计中,电子工程师可以根据具体需求,合理配置寄存器,选择合适的外部元件,以实现最佳的性能表现。同时,在使用过程中,要注意满足其电气参数和时序要求,确保器件的正常工作。大家在实际应用中是否遇到过时钟信号不稳定的问题呢?CDC7005是否能为你解决这些问题?欢迎在评论区分享你的经验和见解。

-

时钟合成器

+关注

关注

0文章

115浏览量

8911

发布评论请先 登录

能有效降低高速网络误码率的超低抖动时钟合成器

详解频率合成器高性能架构的实现

超低抖动时钟合成器的设计挑战

超低抖动时钟合成器的设计挑战

超低抖动时钟合成器的设计挑战

超低抖动时钟合成器的设计挑战

限制性试剂影响ADC的信噪比性能和CDC7005与ADS5500的比较详细概述

CDC7005:高性能时钟合成器与抖动消除器

CDC7005:高性能时钟合成器与抖动消除器

评论