汽车级时钟缓冲器与乘法器 CDCS504-Q1 设计指南

引言

在汽车电子应用中,时钟信号的精准处理至关重要。CDCS504-Q1 作为一款专为汽车应用设计的时钟缓冲器和时钟乘法器,凭借其出色的性能和易于使用的特点,在相关领域备受关注。本文将深入剖析 CDCS504-Q1 的特性、应用及设计要点,为电子工程师们提供全面的设计参考。

文件下载:cdcs504-q1.pdf

一、CDCS504-Q1 特性解析

(一)汽车级认证与宽温范围

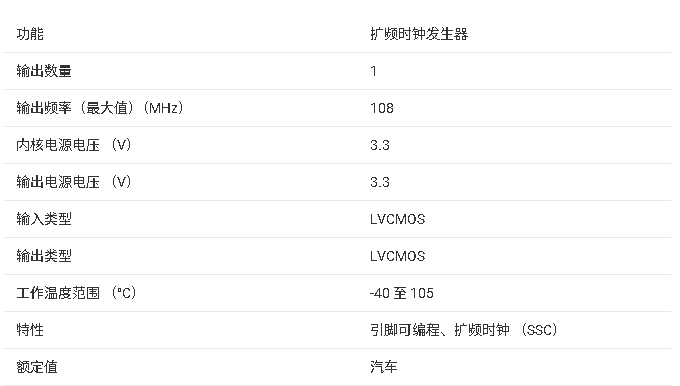

CDCS504-Q1 通过了 AEC-Q100 测试,符合汽车应用标准。其环境工作温度范围为 -40°C 至 105°C,能在各种恶劣的汽车环境中稳定工作。同时,该器件的 HBM ESD 分类等级为 H2,CDM ESD 分类等级为 C3B,具备良好的静电防护能力。

(二)灵活的时钟乘法与输出控制

它是时钟乘法器,可通过一个外部控制引脚在 x1 或 x4 之间选择输出频率。此外,还能通过控制引脚实现输出禁用功能,方便工程师根据实际需求灵活配置。

(三)低功耗与小封装设计

采用单一 3.3V 电源供电,功耗较低。并且采用 8 引脚 TSSOP 封装,占用空间小,适合对空间要求较高的汽车电子设计。

二、应用场景

CDCS504-Q1 主要应用于需要时钟乘法的汽车应用中,例如汽车放大器和信息娱乐系统。当应用中没有可用的 MCLK 时,它可以与 TAS6424-Q1 四通道 D 类数字输入音频放大器完美配合,为系统提供稳定的时钟信号。

三、详细技术参数

(一)绝对最大额定值

| 参数 | 最小值 | 最大值 | 单位 |

|---|---|---|---|

| VDD(电源电压) | -0.5 | 4.6 | V |

| VIN(输入电压) | -0.5 | 4.6 | V |

| Vout(输出电压) | -0.5 | 4.6 | V |

| IIN(输入电流) | - | 20 | mA |

| Iout(连续输出电流) | - | 50 | mA |

| TJ(最大结温) | - | 125 | °C |

| Tstg(存储温度) | -65 | 150 | °C |

(二)ESD 额定值

| 类型 | 数值 | 单位 |

|---|---|---|

| 人体模型(HBM) | ±1500 | V |

| 带电器件模型(CDM) | ±750 | V |

(三)推荐工作条件

| 参数 | 最小值 | 标称值 | 最大值 | 单位 |

|---|---|---|---|---|

| VDD(电源电压) | 3 | - | 3.6 | V |

| fIN(输入频率,FS = 0) | 2 | - | 27 | MHz |

| fIN(输入频率,FS = 1) | 2 | - | 27 | MHz |

| VIL(LVCMOS 低电平输入电压) | - | 0.3 × VDD | - | V |

| VIH(LVCMOS 高电平输入电压) | - | VDD | - | V |

| VIT(LVCMOS 输入电压阈值) | - | 0.5 × VDD | - | V |

| CLOAD(输出负载测试,LVCMOS) | - | 15 | pF | |

| IOH/IOL(输出电流) | - | ±12 | mA | |

| TA(工作环境温度) | -40 | - | 105 | °C |

(四)电气特性

在推荐工作温度范围内,该器件具有一系列电气特性,例如:

- 当 fin = 3.072 MHz 且 FS = 1 时,器件电源电流典型值为 24 mA。

- 输出频率方面,FS = 0 时为 2 - 27 MHz,FS = 1 时为 8 - 108 MHz。

四、功能模式与工作原理

(一)功能模式

CDCS504-Q1 的输出状态和频率由引脚 7(OE)和引脚 5(FS)控制。当 OE 为低电平时,输出为三态;当 OE 为高电平时,输出时钟信号,输出频率取决于 FS 的状态。FS 为高电平时启用频率 ×4 模式,FS 为低电平时输出频率等于输入频率。

(二)工作原理

该器件是 LVCMOS 输入时钟缓冲器,输入信号由锁相环(PLL)处理。PLL 的输出频率可以等于输入频率或乘以 4,从而使器件能够生成 2 MHz 至 108 MHz 的输出频率。

五、设计与应用要点

(一)电源设计

CDCS504-Q1 需要 3.3V 电源供电,在设计电源电路时,要确保电源的稳定性和纯净度,可在 VDD 引脚附近放置一个 0.01µF 的旁路电容,以减少电源噪声的影响。

(二)布局设计

由于该器件的典型供电电流仅为 20 mA,热设计方面没有太大挑战。在布局时,要注意输入输出引脚的布线,避免信号干扰。可参考文档中的布局示例进行设计。

(三)应用曲线参考

在不同的工作模式和温度条件下,器件的输出周期抖动会有所不同。例如,在 X1 模式下,8 MHz 输入和输出且 VDD = 3.3V 时,典型的周期抖动与温度的关系可参考相关应用曲线。工程师可以根据这些曲线来评估器件在不同环境下的性能。

(四)WEBENCH 工具辅助设计

借助 WEBENCH® 电源设计工具,工程师可以轻松创建自定义设计。只需输入输入电压、输出电压和输出电流要求,即可优化设计的效率、尺寸和成本等关键参数。该工具还能提供定制化的原理图、实时定价和组件可用性信息,同时支持电气和热仿真等功能,方便工程师进行全面的设计验证。

六、总结

CDCS504-Q1 作为一款专门为汽车应用设计的时钟缓冲器和乘法器,具有丰富的功能和出色的性能。在实际设计过程中,工程师们需要充分了解其特性和参数,合理运用电源设计、布局设计和辅助工具等手段,以确保设计的稳定性和可靠性。你在使用 CDCS504-Q1 进行设计时,遇到过哪些挑战呢?欢迎在评论区分享你的经验和见解。

-

汽车电子

+关注

关注

3046文章

9086浏览量

173110 -

时钟缓冲器

+关注

关注

2文章

273浏览量

51954

发布评论请先 登录

MPY600 具有负载驱动功能的乘法器

使用verilogHDL实现乘法器

乘法器原理_乘法器的作用

CDCL6010 1.8V 11输出时钟乘法器、分配器、抖动消除器和缓冲器数据表

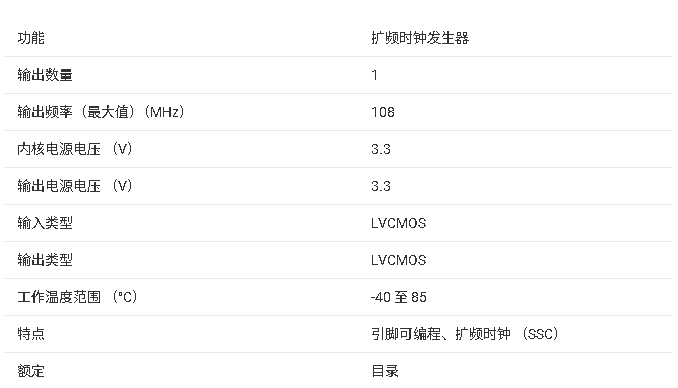

CDCS503带可选SSC的时钟缓冲器/时钟乘法器数据表

CDCS503-Q1 时钟缓冲器/时钟倍频器技术文档总结

汽车级时钟缓冲器与乘法器 CDCS504-Q1 设计指南

汽车级时钟缓冲器与乘法器 CDCS504-Q1 设计指南

评论