在2025 RISC-V中国峰会的高性能计算论坛上,阿里巴巴达摩院高级技术专家贾昊yan分享了玄铁处理器IP和生态的最新进展。他表示,玄铁IP持续完善在多个主流市场的产品矩阵,不断演进,覆盖高性能和AI加速场景的C系列,安全和实时性方面的R系列,赋能端测的E系列,以及搭建多核系统方案的玄铁系列,还有DIC技术等等。

高性能CPU IP玄铁C930

玄铁下一代旗舰处理器C930采用15级乱序超标量流水线设计,支持CHI协议,具备多核多cluster可扩展能力,拥有6译码宽度和10+发射宽度,性能表现卓越。据测试,C930的SPECint 2006高达15分/GHz以上,达到服务器级别应用水准,可满足PC、边缘服务器及自动驾驶等高性能计算场景的严苛需求。

C930搭载了512 bits RVV1.0矢量扩展与8 TOPS Matrix双引擎,将通用高性能算力与AI算力原生融合,并开放DSA(Domain-Specific Architecture)扩展接口,支持更多定制化功能,为AI与高性能计算提供了更强大的底层支撑。

贾昊yan介绍,C930架构包括指令取指子系统、译码与乱序发射子系统、执行子系统,以及多集访存子系统,其中向量执行包括加解密,同时协处理器拓展部分具有较高的可配置性。在RVA23 Profile的基础上加入了玄铁自定义的拓展,协处理器的拓展,并且高效支持了RV官方在高性能方面的规范。

在目前的典型工作场景下C930处理器性能可以达到3.4GHz以上,贾昊表示,当玄铁迈过3GHz大关,才算迈入高性能处理器的大门。而RISC-V处理器在赶超X86和ARM方面,C930既支持RV定义的拓展,同时在玄铁自定义上实现了8T配置能力,可谓是战力充沛,并且支持灵活的算力配比,并以解耦实现方式供用户在能效比还是性能优先之间进行自主选择,这样C930可以实现在GEMM算力利用率上相比友商达到2-3倍的性能提升。

玄铁XL-300

玄铁XL-300支持弹性可配置架构,最多可支持8处理器的核心,支持大小核的搭配配置,L3开始最大可支持到23兆,还有丰富的对外接口的支持。XL-300还对特定的场景进行性能优化,支持容量分配、带宽分配,同ID上的DPC独显也会进行另行的加速设计。XL-300在团队不断优化下,相比XL-200,频率提升20%,带宽翻倍,同时我们的面积增加5%。大大控制了硬件成本,也会实现很高的设计质量。

玄铁在系统方面的重要补充IO MMU,采用分布式高并发的IO TLB设计,它支持灵活集成,采用独立CU设计,适配多种接口,包括TCIE,集成了IO MPT,也支持虚拟化。面向加速器场景,我们支持GIPC,也支持设备QS的管控。总之玄铁分布式的IO MMU是一款面向服务器领域的功能完备高性能的IO MMU,实现了全栈软件生态的支持。

另外,在支持社区定义的多项RISC和安全规范的基础上,对服务器场景还进行了更加充分的可靠性支持。

玄铁DSA及可拓展接口

通过玄铁协处理器拓展接口,可以实现灵活应用的协处理的拓展支持。通过玄铁预定义的一些自定义指令集拓展,以及译码接口,可以帮助客户快速高效的参照使用运力,实现对自己特定应用场景的加速。通过玄铁自定义的协处理接口标准,可以实现高速的C930和协处理器之间的数据信息传递。这样可以高效定制指令和工具链,客户只需要根据指令规范,依据实际的需求进行定义、编写、拓展、描述文件。依据流程自动生成工具链,可以完成对玄铁处理器的适配,这样可以大大节省开发的周期和成本。

发布评论请先 登录

西门子EDA亮相2026玄铁RISC-V生态大会

玄铁C925首秀!思尔芯助推玄铁RISC‑V全场景验证与落地

直击玄铁RISC-V生态大会,看ALINX FPGA+RISC-V解决方案

RT-Thread 邀您参与“开放・连接”2026玄铁 RISC-V 生态大会,携手共铸 RISC-V“芯”纪元

新思科技邀您共赴2026玄铁RISC-V生态大会

RISC-V创新中心联合达摩院玄铁发布无剑芯片设计平台定制版

Powered by XuanTie,Qwen Inside:阿里通义大模型携手玄铁 RISC-V开启“端侧智能”新纪元

新思科技HAPS-200助力阿里巴巴达摩院加速玄铁C930开发验证

学以致用 虚位以待|玄铁RV学院课程正式上线,玄铁与PLCT实验室邀您创“芯”未来

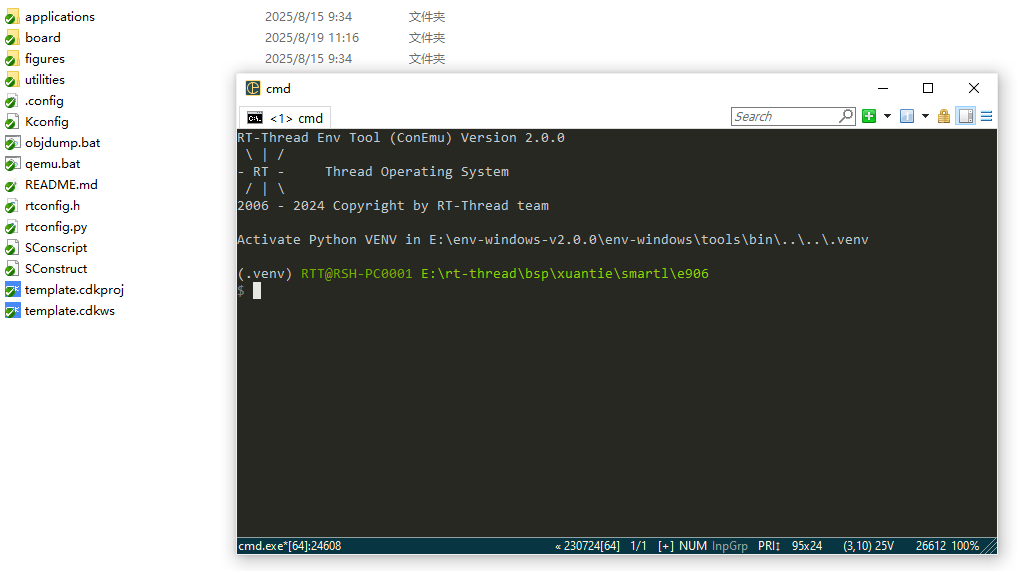

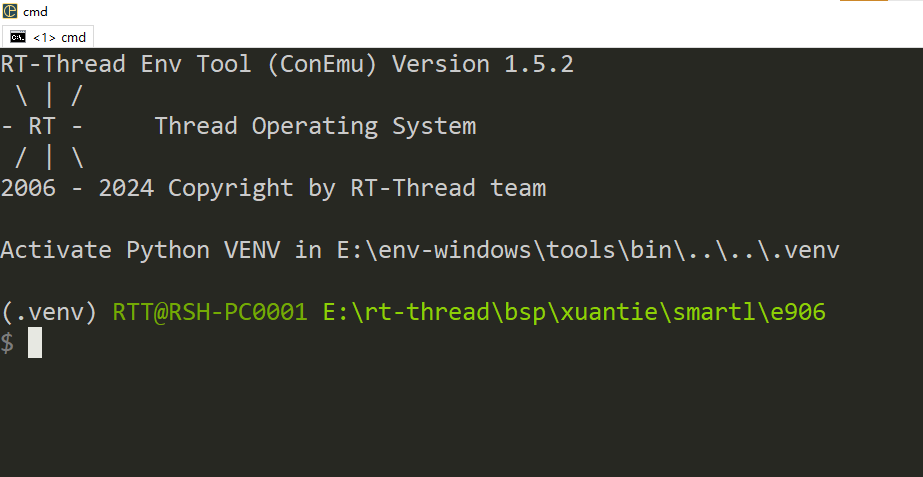

RT-Thread生成玄铁RISC-V BSP的CDK工程开发指南 | 技术集结

直播预约 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

玄铁下一代旗舰处理器C930:双算力引擎,助力 RISC-V高性能计算

玄铁下一代旗舰处理器C930:双算力引擎,助力 RISC-V高性能计算

评论