本文翻译转载于:Cadence Blog

作者:Vishnu Teja S

大家是否想过,我们的智能手机为何能够拍摄出令人惊叹的照片、播放清晰悦耳的音乐或是准确测量心率?

答案就藏在模拟集成电路(IC)设计领域。模拟电路在电子技术中发挥着至关重要的作用,负责处理连续信号,而这些连续信号构成了现代世界的支柱。此外,模拟 IC 设计将艺术与科学完美融合,工程师通过精心设计电子电路来处理连续信号。在设计过程中,他们需要综合考量各种因素,包括进行大量的调整、优化以及一些迭代任务。

在本文中,我们将探讨模拟 IC 设计流程的各个阶段,并重点介绍每个步骤中使用的 Cadence 工具。

模拟 IC 设计流程

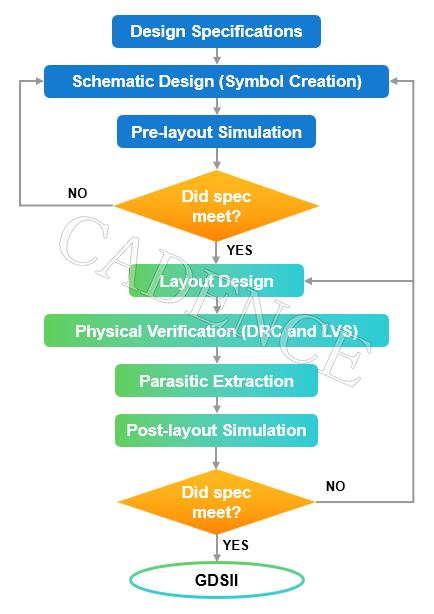

模拟 IC 设计是一个将概念转化为高性能物理芯片的迭代过程。以下是其中涉及的每个阶段。

模拟 IC 设计流程

设计规范:奠定基础

模拟 IC 设计流程的第一步是定义规范,包括性能指标、功耗和面积限制。明确了解这些要求是顺利开展后续设计阶段的关键。

原理图设计和符号创建:赋予设计生命

下一阶段是使用Virtuoso Schematic Editor创建原理图设计和符号,借助这一工具,可以轻松、准确地创建和编辑原理图。

布线前仿真:验证功能和性能

版图前仿真对于验证电路的功能和性能至关重要。Cadence Spectre Circuit Simulator用于进行电路仿真,而Virtuoso ADE Explorer 和 Virtuoso ADE Assembler提供用户友好的界面。这些工具可帮助设计师在版图阶段之前发现和修复潜在问题。

版图设计:将原理图转化为现实

在此阶段,原理图被转换为物理版图。每个晶体管都经过精心排布,以优化布线和面积。Virtuoso Layout Suite具有创新的自动布局布线功能,大大加快了版图设计过程。

物理验证:确保设计完整性

物理验证是一个关键步骤,包括使用Pegasus Verification System执行 DRC(设计规则检查)和 LVS(实体与逻辑)检查。借助适用于Virtuoso Studio的全新iPegasus Verification System,设计人员能够在Virtuoso Layout Suite中无缝运行物理验证检查。

寄生参数提取:精确建模以实现最佳性能

寄生参数提取涉及从版图中识别寄生元件并为其建模,以确保最佳性能。Cadence Quantus Extraction Solution可高精度地完成这一任务,帮助设计人员优化设计,进而获得良好的成果。

版图后仿真:功能和性能的最终检查

在提取的版图视图上进行版图后仿真,对功能和性能进行最终检查。设计人员可以重复使用版图前仿真中的相同设置,确保设计流程顺畅且高效。

流片:准备投产

最后阶段是生成用于制造的 GDSII 文件。芯片完成制造并经过质量检验后,即可投入市场。

通过遵循这一全面的模拟 IC 设计流程,设计人员可以利用 Cadence 工具的强大功能,创建高性能、可靠且高效的模拟 IC。无论您是经验丰富的设计师还是刚入门的初学者,该流程均可为您提供清晰的路线图,助您在复杂的模拟 IC 设计领域取得成功。

-

模拟IC

+关注

关注

8文章

179浏览量

30625 -

IC设计

+关注

关注

38文章

1369浏览量

108002 -

Cadence

+关注

关注

68文章

1000浏览量

146281

原文标题:模拟 IC 技术志|从概念到现实:了解 Cadence 模拟 IC 设计流程

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Giantec采用Cadence技术统一数字流程生产其混合信号芯片

基于Cadence的IC设计

Cadence助力Denso大幅提升IC设计效率

TSMC 和 Cadence 合作开发3D-IC参考流程以实现真正的3D堆叠

Cadence数字和定制/模拟设计流程获得TSMC最新N3E和N2工艺技术认证

Cadence 数字和定制/模拟设计流程获得 Samsung Foundry SF2 和 SF3 工艺技术认证

Cadence数字和定制/模拟流程通过Samsung Foundry的SF2、SF3工艺技术认证

Cadence 数字、定制/模拟设计流程通过认证,Design IP 现已支持 Intel 16 FinFET 制程

浅谈Cadence模拟IC设计流程

浅谈Cadence模拟IC设计流程

评论