共模抑制比详解

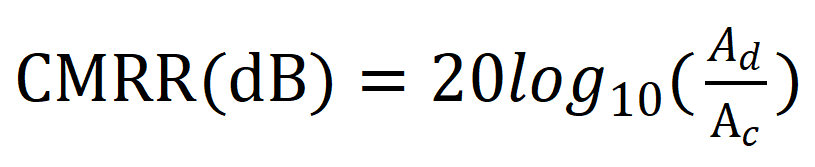

在探头的数据手册上,共模抑制比性能参数是核心指标之一。共模抑制比又名CMRR,通常用分贝(dB)来表示,其计算公式为:

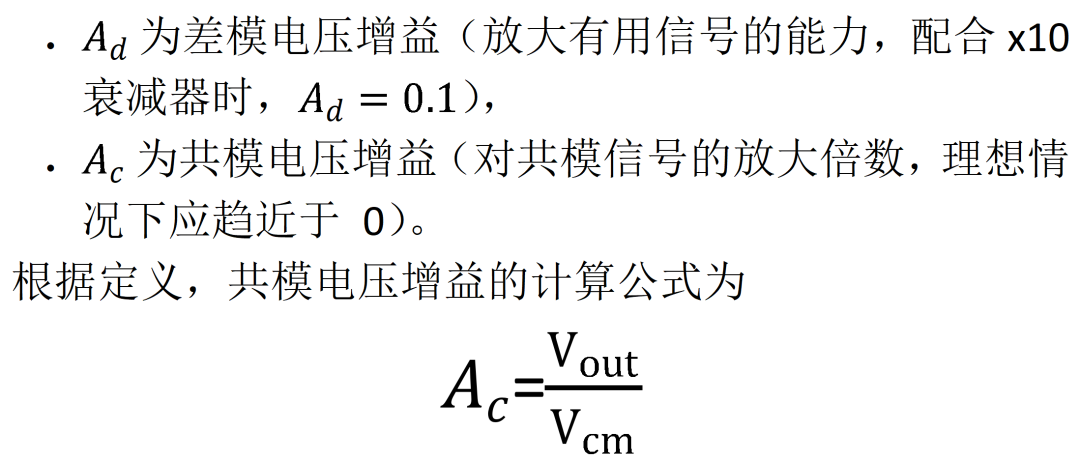

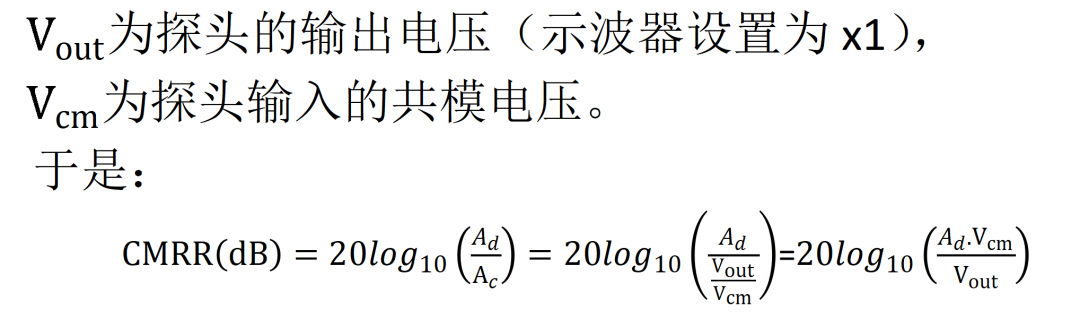

其中

其中

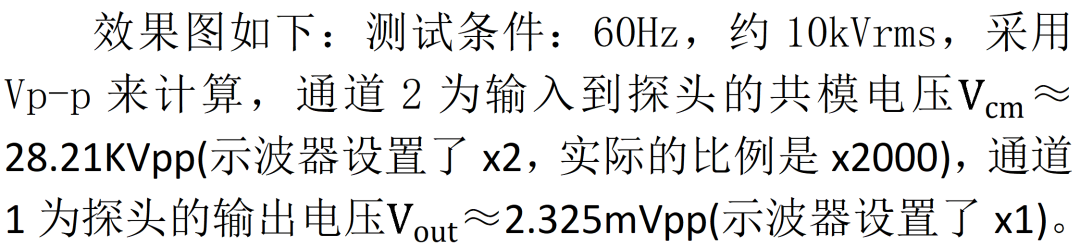

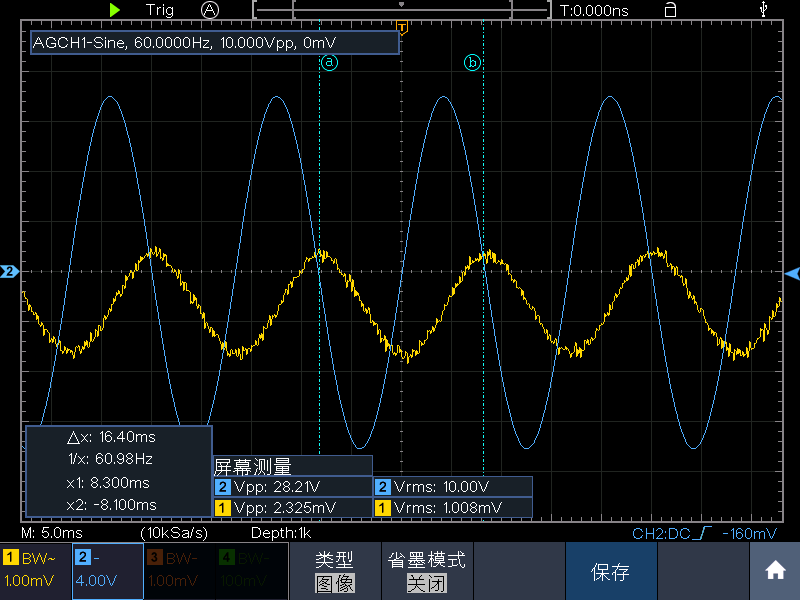

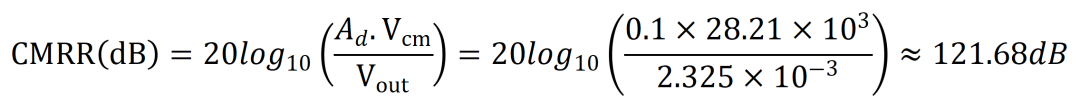

本司光隔离产品CMRR在直流或低频下能达到120dB以上,本文用光隔离探头介绍如何测量探头的共模抑制比:

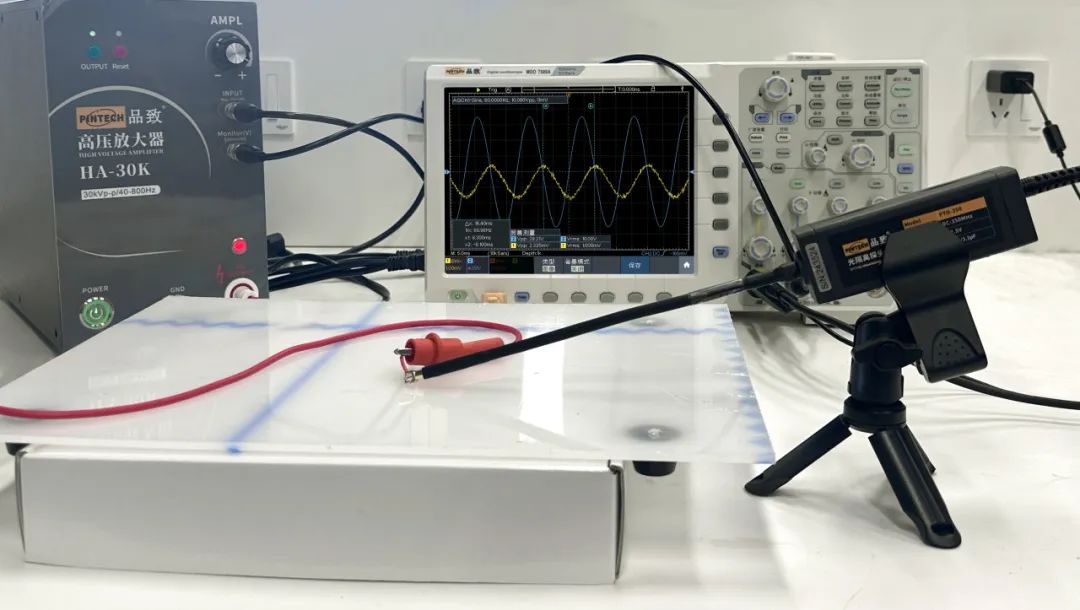

设备准备

30kV放大器:HA-30K

光隔离探头:PTO350配X10衰减器

高频示波器:MDO7500A

信号发生器:DG5100

搭建外围电路:X10衰减器前端两极短接,连到30kV放大器的输出端。

对应上述的公式计算:配合x10衰减器时,光隔离探头输入输出对应:

以上是用光隔离探头测量共模抑制比的实验过程。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

探头

+关注

关注

0文章

1397浏览量

44027 -

共模抑制比

+关注

关注

3文章

88浏览量

16413

发布评论请先 登录

相关推荐

热点推荐

对消驱动电路提高共模抑制比

为了提高电路的共模抑制比,常采用对消驱动电路(右腿驱动)来提高共模抑制比,本文分析了对消驱动电路的原理,结合实际电路实际验证了电路的效果。

发表于 02-02 11:20

•3918次阅读

消除共模噪声的秘密武器-共模抑制比

一、什么是共模抑制比?共模抑制比(CMRR)是衡量放大器对共模信号抑制能力的一个关键指标,是用来描述设备抵御共模信号影响的能力。共模信号是指同时存在于两个输入端并具有相同大小和相位的信号,例如电源

影响电路共模抑制比的因素有哪些?如何去提高电路的共模抑制比?

此电路用来检测脑电波的信号,性能要求此电路的共模抑制比要达到不低于80dB,而现在实测只能达到67dB,想知道,影响电路共模抑制比的因素有哪些?如何去提高电路的共模抑制比?

发表于 08-20 07:21

怎么测ADS1299芯片的共模抑制比?

怎么测ADS1299芯片的共模抑制比?将通道1的正负极输入短接,接入一个0.5VP,共模电压2.5V,F=50Hz,FFT图像显示输出在50Hz时,为80dB。然而手册是-110dB,应该怎么测出-110dB的共模抑制比呢?

发表于 11-15 06:26

关于仪表运放共模抑制比的问题

如图所示,下面是一个交流耦合放大电路,在电路的差分输入端输入差模(100uV,10Hz)和共模信号(10V,10Hz),进行电路的共模抑制比(CMRR)测试,测试发现:

1、差分信号从INS+

发表于 08-03 06:26

共模抑制比CMRR与电源抑制比PSRR相关介绍

共模抑制比(CMRR:comon-mode-rejection-ratio)和电源抑制比(PSRR:power-supply-rejection-ratio)是运放性能的重要指标,关于他们的具体仿真

发表于 12-27 07:24

求助,关于仪表运放共模抑制比的问题

如图所示,下面是一个交流耦合放大电路,在电路的差分输入端输入差模(100uV,10Hz)和共模信号(10V,10Hz),进行电路的共模抑制比(CMRR)测试,测试发现:

1、差分信号从INS+

发表于 11-17 09:09

差分放大电路共模抑制比的测定

通过硬件和软件的仿真实验,总结出差分放大电路共模抑制比测定的正确方法关键词:差分放大电路;共模抑制比;差模电压放大倍数;共模电压放大倍数;仿真

发表于 04-13 11:07

•91次下载

什么是共模抑制比

什么是共模抑制比

为了说明差动放大电路抑制共模信号的能力,常用共模抑制比作为一项技术指标来衡量,其定义为放大器对差模信号的电压放大倍数Aud 与对共模信号的电

发表于 10-15 17:37

•9337次阅读

放大器的共模抑制比的定义

放大器的共模抑制比的定义

共模抑制比(CMRR)是指差分放大器对同时加到两个输入端上的共模信号的抑制能力。更确切地说,CMRR是产生特

发表于 04-22 20:40

•2608次阅读

共模抑制比,共模抑制比是什么意思

共模抑制比,共模抑制比是什么意思

共模抑制比的定义

为了综合评价差动放大电路对共模信号的抑制能力和对差模信号的放大能力,特

发表于 03-09 16:36

•1.5w次阅读

六大问题帮你搞定共模抑制比

你或许知道“共模抑制比是差模增益与共模增益之比”,但你知道共模抑制比120dB与60dB区别多大吗?你知道为什么要抑制共模信号吗?

发表于 10-01 15:00

•2.4w次阅读

什么是共模抑制比CMRR?什么是电源抑制比PSRR?

什么是共模抑制比CMRR?什么是电源抑制比PSRR? 共模抑制比(common mode rejection ratio,CMRR)和电源抑制

影响共模抑制比的主要因素 如何提高共模抑制比?

影响共模抑制比的主要因素 如何提高共模抑制比? 共模抑制比是一种衡量信号处理系统抑制共模干扰的能力的指标。它表示当输入信号被共模干扰所扰动时,系统输出信号中共模干扰的减弱程度。

什么是共模抑制比?

什么是共模抑制比?

评论