影响共模抑制比的主要因素 如何提高共模抑制比?

共模抑制比是一种衡量信号处理系统抑制共模干扰的能力的指标。它表示当输入信号被共模干扰所扰动时,系统输出信号中共模干扰的减弱程度。共模抑制比较大的系统能够有效抑制共模干扰,提高信号传输质量。影响共模抑制比的主要因素有系统设计、电路拓扑、滤波器设计、地线布局等。

首先,系统设计是影响共模抑制比的关键因素之一。在系统设计过程中,合理地选择合适的工作电压范围、工作频率范围和放大倍数等参数是十分重要的。合理选择这些参数可以确保系统正常工作并保证共模抑制比在较高水平。

其次,电路拓扑也是共模抑制比的重要影响因素之一。电路拓扑指的是信号处理系统中各个元件的连接方式和布局。一种常用的电路拓扑是差分放大器,它可以有效抑制共模干扰。差分放大器采用了两个输入端,通过将共模信号作用在两个输入端上,可以将共模信号滤除,从而提高共模抑制比。

此外,滤波器设计也对共模抑制比起到重要作用。滤波器是一种用于滤除非特定频率的信号的电路。通过合理选择滤波器的带宽和特性,可以减小共模信号的影响,提高共模抑制比。在滤波器设计中,需要考虑滤波器的降噪能力、频率响应以及滤波器的截止频率等因素。

此外,地线布局也是影响共模抑制比的重要因素之一。地线布局指的是系统中地线的布置方式。合理的地线布局可以降低共模干扰的影响,提高共模抑制比。在地线布局中,需要注意避免地线回路过长,减小地线的电阻、电感和电容等。

综上所述,影响共模抑制比的主要因素有系统设计、电路拓扑、滤波器设计、地线布局等。为了提高共模抑制比,我们可以从合理选择系统设计参数、采用差分放大器电路拓扑、设计合适的滤波器以及优化地线布局等方面入手。这些措施可以有效地抑制共模干扰,提高信号传输质量。

-

共模抑制比

+关注

关注

3文章

85浏览量

16345 -

信号处理系统

+关注

关注

1文章

27浏览量

11772

发布评论请先 登录

影响电解电容寿命的主要因素及其详细分析

什么是共模抑制比?

NH13734网络测试巴伦(BALUN)现货库存

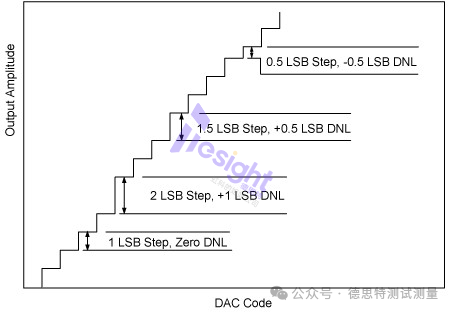

从偏移误差到电源抑制比,DAC核心术语全解析

海洋仪器电源抑制比测试方案26800元起

电池化成、医疗 ECG 精准检测!思瑞浦推出放大器TPA1287

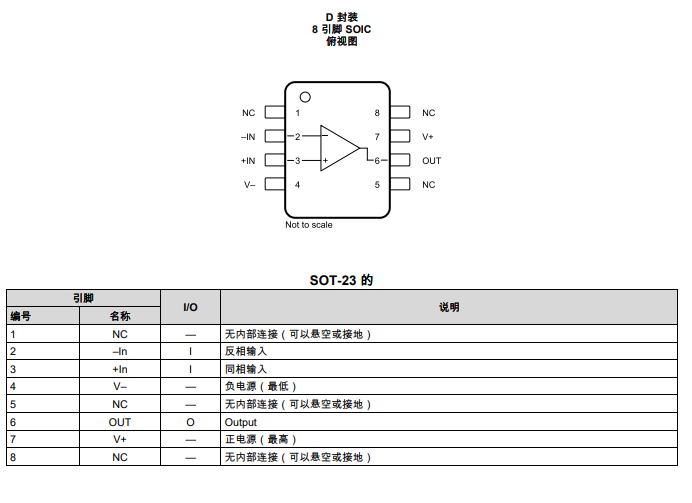

OPA207 低功耗、低噪声、高精度、双极性RRO运算放大器技术手册

瑞盟MS8188-36V、高精度、零漂移、低噪声运放,兼容OPA188/AD4077

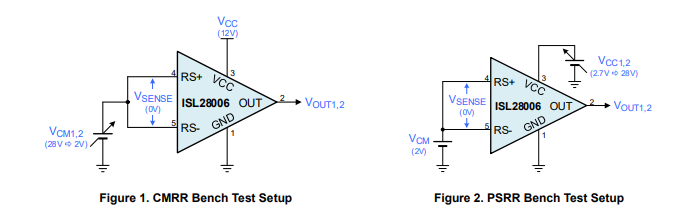

ISL28006:测量共模和电源抑制比

影响共模抑制比的主要因素 如何提高共模抑制比?

影响共模抑制比的主要因素 如何提高共模抑制比?

评论