何为信号完整性的分析

信号完整性包含:波形完整性(Waveform integrity)时序完整性(Timing integrity)电源完整性(Power integrity)信号完整性分析的目的就是用小的成本,快的时间使产品达到波形完整性、时序完整性、电源完整性的要求;我们知道:电源不稳定、电源的干扰、信号间的串扰、信号传输过程中的反射,这些都会让信号产生畸变,所以我们研究讯号完整性就需要研究差分讯号,讯号的反射,讯号的串扰等等参数,今天我们系统性的回顾下!

1

信号完整性的定义

信号完整性(Signal Integrity):就是指电路系统中信号的质量,如果在要求的时间内,信号能不失真地从源端传送到接收端,我们就称该信号是完整的,当电路中信号能以要求的时序、持续时间和电压幅度到达接收端时,该电路就有很好的信号完整性,当信号不能正常响应时,就出现了信号完整性问题。

何为高速差分讯号传输

随着信号速率的提高,差分互连得到越来越多的应用。实际上差分对是具有耦合的传输线,其主要用的是差分信号的特征,用差分对来实现。差分信号利用两个输出驱动来驱动两条传输线。其中一根携带信号,另一根携带它的互补信号,两条传输线上面的压差就是需要传输的信息。

在差分信号的传输过程中,主要是以两条传输线为传输载体,差分驱动器输出的是边缘能够对齐的两个信号,但是正好方向相反,如下图所示。两个高速信号分别传输,接收端在信号抵达接收器时对两个信号作差分检测,得到的差值就是差分信号,但是今天我们聊的是信号完整性,就是我们常说的SI参数,其名词解释就是指讯号线上的信号质量,讯号完整性不是由单一某一个因素导致的,而是讯号通讯过程中和设计中可能引起的多种因素引起的,我们也需要知道相关测试参数名词的解释!

传输线(Transmission Line):由两个具有一定长度的导体组成回路的连接线,我们称之为传输线,有时也被称为延迟线。

上升/下降时间(Rise/Fall Time):信号从低电平跳变为高电平所需要的时间,通常是量度上升/下降沿在10%-90%电压幅值之间的持续时间,记为Tr。

截止频率(Knee Frequency):这是表征数字电路中集中了大部分能量的频率范围(0.5/Tr),记为Fknee,一般认为超过这个频率的能量对数字信号的传输没有任何影响。

特征阻抗(Characteristic Impedance):交流信号在传输线上传播中的每一步遇到不变的瞬间阻抗就被称为特征阻抗,也称为浪涌阻抗,记为Z0。可以通过传输线上输入电压对输入电流的比率值(V/I)来表示。

传输延迟(Propagation delay):指信号在传输线上的传播延时,与线长和信号传播速度有关,记为tPD。

趋肤效应(Skin effect):指当信号频率提高时,流动电荷会渐渐向传输线的边缘靠近,甚至中间将没有电流通过。与此类似的还有集束效应,现象是电流密集区域集中在导体的内侧。

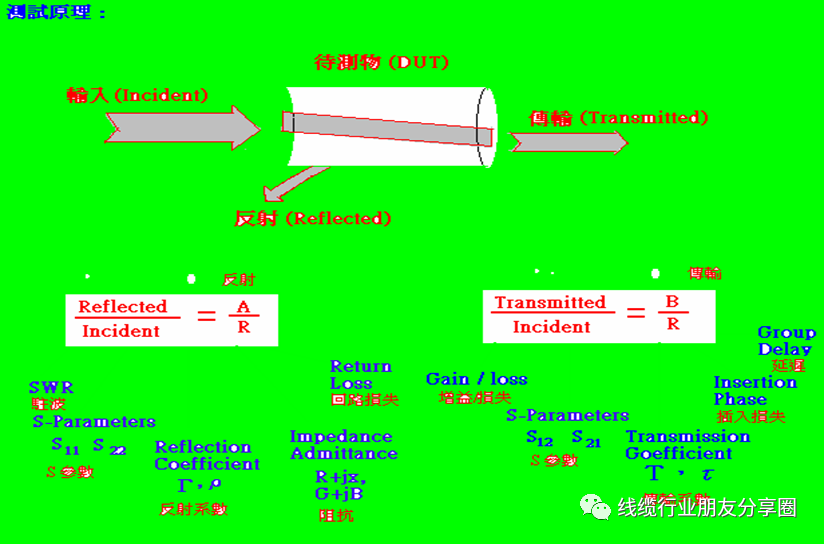

反射(Reflection):指由于阻抗不匹配而造成的信号能量的不完全吸收,发射的程度可以有反射系数ρ表示。

串扰:串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生的不期望的电压噪声干扰,这种干扰是由于传输线之间的互感和互容引起的。

屏蔽效率(SE):是对屏蔽的适用性进行评估的一个参数,单位为分贝。吸收损耗:吸收损耗是指电磁波穿过屏蔽罩的时候能量损耗的数量。

反射损耗:反射损耗是指由于屏蔽的内部反射导致的能量损耗的数量,他随着波阻和屏蔽阻抗的比率而变化。

校正因子:表示屏蔽效率下降的情况的参数,由于屏蔽物吸收效率不高,其内部的再反射会使穿过屏蔽层另一面的能量增加,所以校正因子是个负数,而且只使用于薄屏蔽罩中存在多个反射的情况分析。

差模EMI:传输线上电流从驱动端流到接收端的时候和它回流之间耦合产生的EMI,就叫做差模EMI。共模EMI:当两条或者多条传输线以相同

2

反射系数

首先我们说一下讯号完整性里面最重要的参数之一:

反射:反射--初始波

当驱动器发射一个信号进入传输线时,信号的幅值取决于电压、缓冲器的内阻和传输线的阻抗。驱动器端看到的初始电压决定于内阻和线阻抗的分压。S参数都是带限的,即每个S参数都有一个截断频率fstop,S参数只有频率低于fstop的信息。在频域-时域转换的时候,这种终止会引入截断误差。在时域反射曲线中表现为以1/fstop的振荡,即纹波。这个振荡的幅度,取决于输入上升沿的频谱。越快的上升沿,时域反射的振荡会越强。因此选择合适的上升沿非常重要。一般地,截断频率为fstop的S参数在求解时域反射的时候,可以用的最快上升沿(20-80%)为:比如一个fstop = 20GHz 的S参数,如果上升沿超过25ps(20-80%),那么输出的时域反射曲线就会出现较明显的纹波。如果上升沿慢于25ps,那么纹波会很小而可忽略。

反射产生的原因

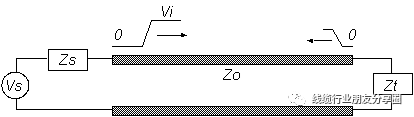

当发送器件将数字信号送到互连线上时,初始信号大小( )取决于发送器件的电压(

)取决于发送器件的电压( )、源内阻(

)、源内阻( )和互连线的特性阻抗(

)和互连线的特性阻抗( ),如图1所示:

),如图1所示:

图1 互连线上的反射现象

其等于互连线特性阻抗在它与源内阻的分压,如式(1),

如果互连线终端接到一个与互连线特性阻抗( )精确匹配的阻抗,那么互连线上的电压保持为,直到发送器件再次发送信号。而如果互连线终端所接阻抗不为

)精确匹配的阻抗,那么互连线上的电压保持为,直到发送器件再次发送信号。而如果互连线终端所接阻抗不为 ,而为

,而为 ,则传输到终端的信号一部分端接到地,而其余的部分将朝发送器件方向反射。反射信号分量的多少取决于负载端反射系数

,则传输到终端的信号一部分端接到地,而其余的部分将朝发送器件方向反射。反射信号分量的多少取决于负载端反射系数 .

.

于是,初始入射电压达到终端时,信号的一部分

,将返回发送器件,并与入射电压叠加,这时负载端的电压为

,将返回发送器件,并与入射电压叠加,这时负载端的电压为 +

+

,如果反射分量

,如果反射分量

达到发送器件,发现源内阻也与特性阻抗不相等(匹配),

达到发送器件,发现源内阻也与特性阻抗不相等(匹配),

会被再一次的反射,反射信号的多少取决于源端反射系数

会被再一次的反射,反射信号的多少取决于源端反射系数 .

.

这时源端的电压则变为 +

+

+

+ +

+

反射会在互连线上不断地进行,直到达到稳定,源端和负载端的稳定电压都为,

反射会在互连线上不断地进行,直到达到稳定,源端和负载端的稳定电压都为,

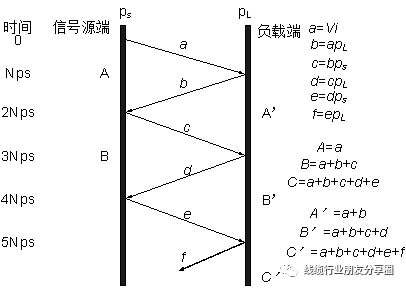

格形图是在源内阻和端接负载都为线性时理解反射产生机理的一种方法。如下图所示

如图中,左边竖线代表互连线的源端,右边竖线代表负载端,而两条竖线之间的斜线代表信号在源端和负载端来回反射,图中自顶向下,表示时间的增加,相邻时刻之间的时间增量等于互连线的延迟。另外,图中两竖线顶端标有相应的反射系数,小写字母表示互连线上传播的反射信号大小,包括从源端和从负载端反射回的,大写字母代表源端的电压,带撇的大写字母表示负载端的电压。

3

串扰参数

串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生的不期望的电压噪声。串扰是由电磁耦合引起的,耦合分为容性耦合和感性耦合两种。容性耦合是由于干扰源(Aggressor)上的电压变化在被干扰对象(Victim)上引起感应电流从而导致的电磁干扰。而感性耦合则是由于干扰源上的电流变化产生的磁场在被干扰对象上引起感应电压从而导致的电磁干扰。因此,信号通过一导体时会在相邻的导体上引起两类不同的噪声信号:容性耦合信号和感性耦合信号。

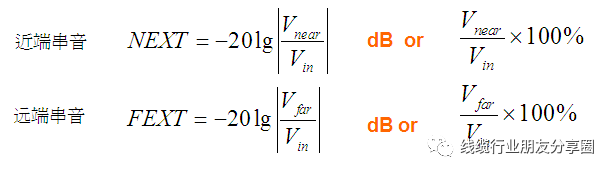

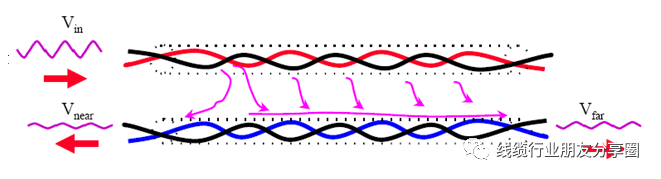

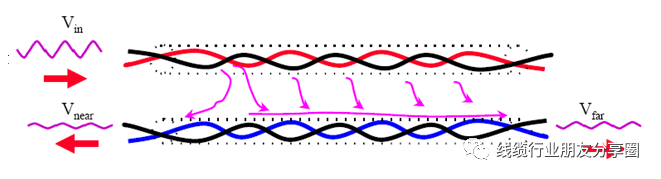

串音主要分为近端串音和远端串音两大类;它们的峰值定义为,近端串音係数NEXT和远程串音係数FEXT;其中Vin为动态线中信号电压;Vnear和Vfar为静态线上近端和远端测得的串音电压.

计算公式如下(串音—Cross Talk 單位—dB)

一对讯号线传输时的高频电容电感效应与 Impedance匹配效应,产生对相邻讯号线造成的干扰现象。

NEXT(Near End Cross Talk)---近端串音,发生在传输源一端的串音现象

FEXT(Far End Cross Talk)---远端串音,发生在接收一端的串音现象

dB=20 Log(V1/V0)

V1-相邻讯号线检出电压

V0-原讯号源输出电压

两线路之间互相干扰的电磁杂讯,一般会随著频率之昇高而增加。

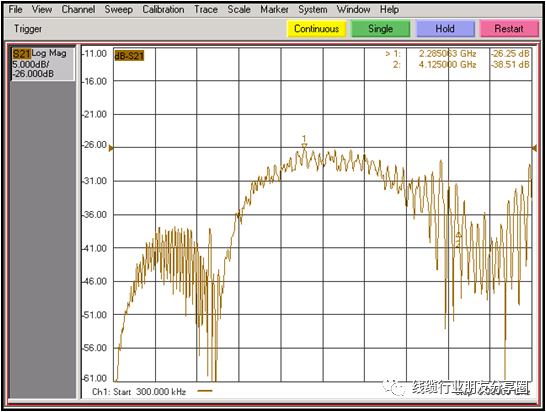

其量测可以NA或TDR来量测,其计算公式如下:

如果Xtalk数值越趋近于0 dB(or近100%)时,表示杂讯干扰的情况越严重,反之,Xtalk dB数值越大(or近0%)时,表示杂讯干扰的情况越少

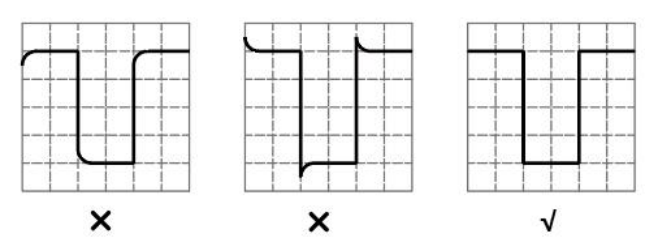

实际量测中的串音测试图形

SSN(同步开关噪音)

开关噪音由差分对间的感性耦合引起,当传输线上电流变化时,会在邻近的传输线上耦合出感 应电压,并激起感应电流,对邻近传输线上的信号产生干扰.

解决方式:

由于差分信号的特性,可以激励差分对进入奇模模态,在此模态下, 差分对本身对耦合噪音有很好的抑制作用.另外可以通过对线包铝箔屏蔽来减弱对其他邻近差分对的干扰.

在高频通信中,我们更关心的是串音干扰而不是SSN;串音干扰是相邻传输线对内或对间由于寄生电感,电容耦合产生的噪音;对传输线上的信号影响很大;必须加以控制;否则会引起信号波形的严重失真,导致接收端误判断.

串音产生原理

串音干扰可以从电容电感耦合角度去理解,也可以从差分信号和共模信号分量角度去理解.

耦合角度描述:

当动态线上有信号通过时,在信号的上升延区域(即电压电流变化的区域).由于线对间的互感和互容的耦合作用,在静态线上将感应出电流,由于噪音电流在静态线上每个方向上感受到的阻抗都相同,所以前向和后向的电流量将相等. 其中一半向后流回到近端,产生近端串音;另一半向前流动到远程,产生远程串音.

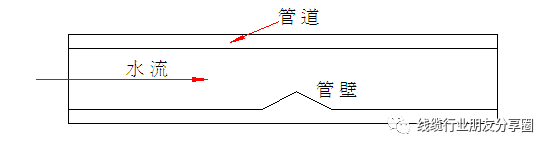

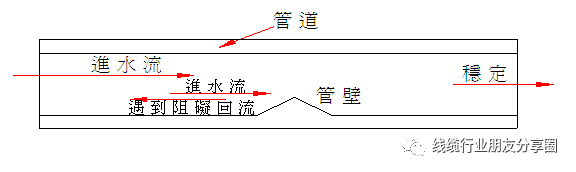

举例分析串音产生的机理和改善方式

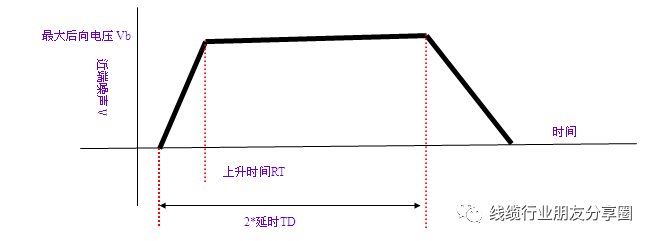

管道裡的水向前流,过程中由于管道孔径或管道有凸起物等诸多因素让水流的速度发生有不稳定的现象,但是当到达终点接收端后,有个稳定的接收后,其输入的水流将达到一个稳定状态,但是在过程中仍有由于遇到障碍而往后流的水流向供水端,这段额外的阻止时间为延时TD,近端串音就是水流从不稳定额外的阻止时间并持续2*TD的时间,如下图解说:

当两条传输线靠近时,互容和互感将增加,从而使NEXT增加)近端串音:

当信号前沿传输了一个饱和长度后,近端的电流将达到一个稳定值;而当动态线上的信号到达远端端接电阻后;就不再有耦合噪音电流,但是静态线上还有后向电流流向静态线的近端,这段额外时间等于时延TD.;近端串音就是耦合电流上升到一个恒定值并持续2*TD,然后下降到0,其中上升时间等于信号的上升时间,如下图解说

远程串音:耦合到静态线上前向传播的噪音,移动速度与动态线上的信号前沿向远端传播的速度相同.在静态线上的每一步,一半噪音电流会迭加在已经存在的沿线噪音上.直到信号前沿到达远端,才有电流出现.即信号达到远端时,远端噪音同时到达.因此远端噪音电流为一个很短的负向脉衝,持续时间等于信号的上升时间TD.近端和远端串音的特徵,决定了远端串音将在高频率段产生很大威胁,而近端串音则在中频率段影响较大.

从差分信号分量和共模信号分量角度描述:

近端串音:

差分信号分量和共模信号分量在差分对上所感受到的阻抗不同,这 一阻抗上的差异将导致,静态线产生近端串音.若阻抗上的这一差异越大则NEXT将越大.

远程串音:

由于共模信号分量和差分信号分量电力线分佈不同,所感受到的有效介电係数不同,导致它们的传播速度不同.差分信号分量将先到达远端,而共模信号分量稍晚点到达远端.它们的差值将导致远程串音,若这一速度差异越大将导致远端串音能量越大,FEXT越大;串音干扰由于相邻线间的耦合产生.耦合度越高,串音干扰越大;频率越高,串音干扰越大;电容稳定性越差,串音越严重;此外,低特性阻抗有利于低串音,绝缘材料介电係数越小,串音越低。

-

信号

+关注

关注

12文章

2936浏览量

80429 -

时序

+关注

关注

5文章

411浏览量

39020 -

电路系统

+关注

关注

0文章

75浏览量

13405

发布评论请先 登录

IDT信号完整性产品:解决高速信号传输难题

PK6350无源探头在高速数字总线信号完整性测试中的应用案例

深圳 9月12-13日《信号完整性--系统设计及案例分析》公开课,即将开课!

罗德与施瓦茨示波器RTO2014破解信号完整性难题的全面指南

普源DHO924示波器在信号完整性测试中的表现

普源DHO5000系列数字示波器信号完整性分析

了解信号完整性的基本原理

上海 6月20-21日《信号完整性--系统设计及案例分析》公开课,即将开课!

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

信号完整性分析科普

信号完整性分析科普

评论