文章来源:学习那些事

原文作者:前路漫漫

本文介绍了硅晶圆拣选测试需要进行直流特性测试、输出驱动能力验证、功能逻辑验证。

概述

硅晶圆拣选测试作为半导体制造流程中的关键质量控制环节,旨在通过系统性电气检测筛选出功能异常的芯片。该测试体系主要包含直流特性分析、输出驱动能力验证和功能逻辑验证三大核心模块,各模块依据器件物理特性与功能需求设计了差异化的检测方法与技术路径。

直流特性测试

直流测试聚焦于芯片基本电学连接性与静态漏电特性的量化评估,其核心检测项包括通路连续性、端口间短路 / 开路状态判定以及泄漏电流阈值监测。在测试执行前,需通过探针卡校准程序完成物理连接性预验证 —— 利用高精度阻抗测量设备,逐一对探针针尖与芯片压点(Bond Pad)的接触电阻进行扫描。对于 28 nm 及以上工艺,接触阻抗需控制在 100 mΩ 以下;14 nm 及以下先进工艺因压点尺寸缩小至 50 μm 以下,接触阻抗要求提升至 10 mΩ 以内,以避免接触不良导致的测试误判。

在通断性检测环节,采用恒压源 - 电流表(V-I)测试架构:对被测两端口施加 1 V 直流偏压,串联 1mA 限流电阻形成测试回路。若回路电流大于 1 mA(等效电阻 <1 kΩ),判定为短路;若电流小于 1 μA(等效电阻> 1 MΩ),则判定为开路。针对深亚微米器件的栅极漏电流(IGSS)与衬底漏电流(ISUB),需使用皮安计在器件截止态下进行精准测量:以 28 nm CMOS 反相器为例,施加 VDD=1.8 V、输入接地时,输出端漏电流典型合格阈值为 < 10 nA;而 10 nm FinFET 器件因栅氧厚度减薄至 1.2 nm,漏电流控制标准严格至 < 100 pA,以满足低功耗设计要求。

输出驱动能力验证

输出检查模块通过模拟实际负载工况,对集成电路的逻辑电平驱动能力进行功能性验证,不同逻辑族器件遵循差异化的测试标准:

TTL 电平器件:输出低电平时(VOL 测试),灌入 8 mA 灌电流,要求 VOL≤0.4 V;输出高电平时(VOH 测试),拉出 2 mA 拉电流,要求 VOH≥2.4 V。

CMOS 电平器件:VOH 典型值≥VDD-0.1 V,VOL 典型值≤GND+0.1 V,驱动能力由输出级晶体管宽长比(W/L)决定 ——PMOS 管 W/L 影响灌电流能力,NMOS 管 W/L 决定拉电流能力。以 PCIe 5.0 接口芯片为例,为满足 8 GT/s 数据速率与 50 Ω 负载驱动需求,其输出级 NMOS 管宽长比通常设计为 1500:1 以上。

通过阶梯式电流扫描(电流步长 1 mA)绘制输出电压 - 电流特性曲线,可评估器件在过载条件下的稳定性。当负载电流超过额定值 20% 时,需重点监测输出电压是否突破规格阈值,确保总线驱动芯片在复杂信号环境下的可靠性。

功能逻辑验证

功能测试通过构建全场景逻辑激励 - 响应模型,实现对电路功能完整性与时序正确性的深度验证。对于含 N 个输入端口的组合逻辑电路,理论穷举测试需 2^N 个向量,实际借助 Synopsys TetraMAX 等 ATPG 工具,通过故障优先级排序与冗余向量剔除算法,可将向量集压缩至 100-500 个,同时实现≥95% 的 Stuck-at 故障覆盖率,并生成故障字典用于失效定位。

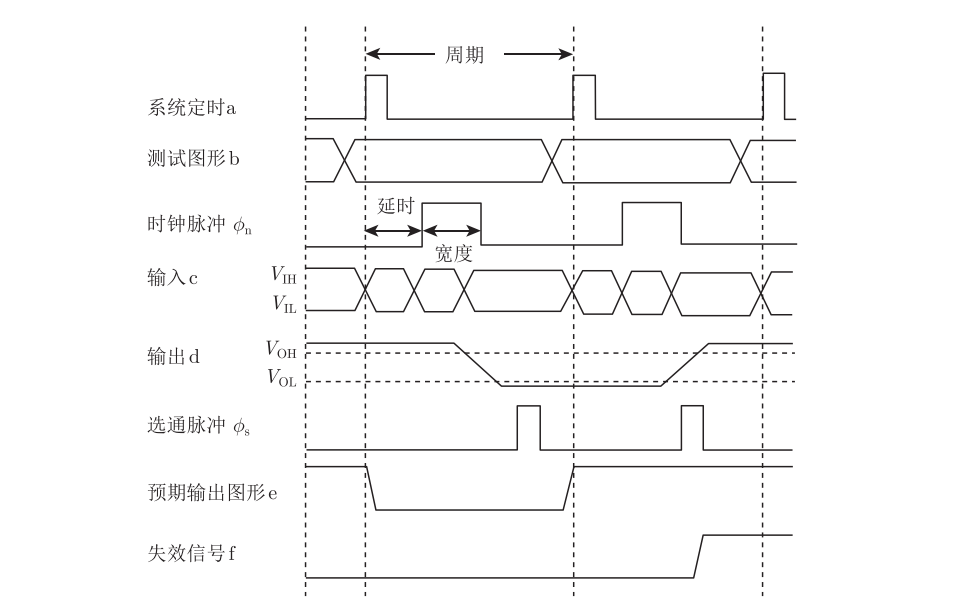

(1)数字电路动态测试

动态功能测试首先要有测试图形,再经过时钟脉冲信号φ控制而形成一定格式的输入测试信号,这些信号通过管脚驱动器送到被测器件的输入端。与此同时,被测器件的输出信号受高、低电平(VOE、VoL)比较器的检验,判断是否满足产品规范的要求;然后受选通脉冲中的控制而与预期输出图形比较,判断逻辑关系是否正确。最后,决定被测器件是否合格。

如果功能测试完全按照参数规范设置的定时信号(时钟脉冲和选通脉冲)和电平基准,而且在最高极限频率下进行,则被测器件通过动态测试时它的动态参数必然符合规范要求。

(2)存储器可靠性测试

存储器通常由地址译码器、存储阵列、输入缓冲器、输出驱动器和读出放大器等功能模块构成。其常见故障可归纳为以下六类典型模式:

① 地址多选故障:单个地址信号触发时,多个存储单元被同时选中,通常由地址译码器晶体管短路或版图布局缺陷导致;

② 地址失效故障:部分存储单元无法通过任何地址访问,多因地址线开路、译码器逻辑失效或存储单元晶体管烧毁引发;

③ 内容固定故障:存储单元数据写入后无法更新,表现为无论输入何种信号,读出值始终为固定逻辑电平(“0” 或 “1”),根源可能是存储电容永久性漏电或晶体管栅极氧化层击穿;

④ 单元串扰故障:某存储单元的数据翻转通过寄生电容耦合至相邻单元,导致非目标单元逻辑状态异常,尤其在高密度存储阵列中因单元间距缩小而更易发生;

⑤ 读后恢复延迟故障:读出放大器在连续读取长串相同数据后,无法快速切换至相反逻辑的读取状态,通常与放大器动态失调或反馈回路响应速度不足相关;

⑥ 写后恢复延迟故障:写周期后立即执行读操作时,取数时间显著延长,在读 / 写共用数据线的架构中,因总线切换延迟和电荷再平衡过程,该现象更为明显。

从故障特性可划分为两大类别:

硬故障:故障表现与环境温度、电源电压波动及输入信号时序无关,具有永久性和确定性。例如存储单元固定型故障、地址线短路等,可通过直流测试或基础功能测试直接定位。

软故障:仅在温度极值、电源电压临界阈值或输入时序边界条件下显现,常规工作条件下器件功能正常。典型场景包括高温下的存储单元漏电加剧、电压跌落导致的逻辑翻转阈值偏移等,需结合环境应力测试与动态功能测试进行暴露。

常用的测试图形

常用测试图形有以下三种:

1. N1型测试图形

2. N2型测试图形

3. N3/2型测试图形

测试图形技术体系

一.线性复杂度图形(O (N)):量产初筛

全 “0”/ 全 “1” 图形:顺序写入单一数据并读取比对,快速检测存储单元固定型故障。该图形对晶体管源漏短路、位线金属桥接等硬故障的检测覆盖率达 80%,广泛应用于嵌入式 SRAM 的内建自测试(BIST)与 NOR Flash 的块初始化验证。

测试序列长度:(2N)x2,全“0”和全“1”各一次,共(4N)次操作)。

棋盘格图形:相邻单元交替写入 “0” 和 “1”,利用存储单元电容(40-60 fF)与位线寄生电容(800 fF-1.2 pF)的分压效应检测串扰。当单元电容与位线电容比值 < 1:20 时,相邻单元数据翻转会导致目标单元电压波动超过阈值电压的 15%,触发数据错误,该图形可有效识别金属层间距不足(<0.15 μm)引发的耦合噪声。但地址故障检测仍不充分。

测试序列长度:2Nx2, “0-1”和“1-0”交替模式各一次,共( 4N ) 次操作)。

齐步图形(March C 算法):执行 “全写 0→逐读 0 写 1→全读 1 写 0→反向操作” 流程,检测地址译码器偏移故障(如地址 i 误选 i+1 单元)。该图形对译码器晶体管阈值电压漂移(ΔVth>100 mV)导致的地址误判具有 100% 检测覆盖率。

测试序列长度:(N+2N+2N)x2=(5N) x 2

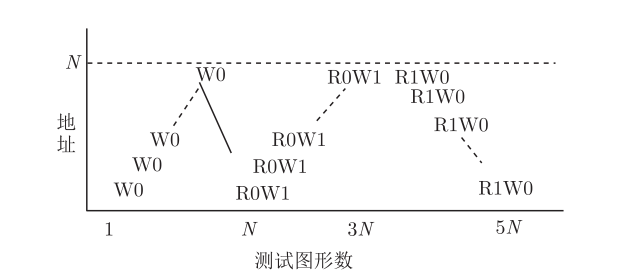

二、平方复杂度图形(O (N²)):研发级深度检测

这类测试图形的长度与存储单元数 N 的 2 次方成正比。这类图形能同时检测地址和数据两方面的故障,主要用于检测存储单元之间的干扰。

走步图形:全写 “0” 后,逐次将基准单元写 “1” 并扫描全阵列,检测位线粘连故障 —— 若字线驱动晶体管因栅极氧化层厚度不均(偏差 > 15%)导致导通电阻异常,基准单元写操作会通过寄生电容耦合至相邻位线,引发整列数据异常。某 1Gb DDR3 存储器实测中,该图形定位到字线氧化层厚度从标准 20 nm 减薄至 17 nm 处的跨单元干扰,对应漏电流超标 3 倍。

图形测试序列长度为:[N+ (1+ N + 1)N] x 2 = (N2+3N) x 2

跳步图形:在走步图形基础上,对非基准单元执行三次读取(Rj1→Rj2→Rj3),通过一致性验证识别动态噪声故障。测试设备需满足时钟抖动 < 1 ps、电压噪声 < 5 mV 的精度,以捕捉读出放大器回踢噪声(典型幅值 10 mV,持续时间 2 ns)对数据稳定性的影响,适用于 DDR4 存储器的时序边界测试(如 tAC=8 ns)。

图形测试序列长度为:{N+[3(N - 1) + 2]N} x 2 = 3N2x2

跳步写恢复图形:固定基准单元为 “0”,逐一对其他单元写 “1” 并实时读取基准单元,验证写操作干扰。在汽车级 eMMC 测试中,结合 125 ℃高温与 VDD=3.6 V(+20% 过压)应力,该图形可加速衬底耦合噪声导致的基准单元翻转,漏检率控制在 0.01% 以下。

图形测试序列长度:[N +6(N -l)N] x2= (6N2-5N) x2

三、N3/2复杂度图形:大容量存储器效率优化

随着存储器容量的不断增大 , N2 型测试图形的测试时间太长。为了减少测试时间,人们又开发了测试序列长度与存储单元 N 的 3/2 次方成正比的 N3/2型测试图形。

正交走步图形:将 N=R×C 的存储矩阵分解为行 / 列独立扫描,利用存储器页模式(Page Mode)减少行激活次数。以 16 Gb DDR4(8Bank,<4096Row,1024Column)为例,测试序列长度从 O (N²)=16 GB² 降至 O (N√N)=16 GB×√16 GB=16GB×4096,操作次数减少 99.96%,测试时间从 1.2 秒缩短至 65 ms。

测试序列长度:{3N + [(2N1/2-1) +2]N} x 2 = (2N3 / 2+4N) x 2

对角线走步图形:聚焦主对角线单元(i=j),该区域因高频访问易发生疲劳失效。在 8 层 HBM3 存储器中,扩展至三维空间测试同地址跨层单元,考虑 TSV 寄生参数(电容 50 fF / 个,电阻 15 Ω/ 个),需在测试向量中加入 200 mV 的驱动电压补偿,以抵消层间耦合导致的信号衰减。

图形测试序列长度为:[N+(N + 2)N1/2]x 2 = (N3/ 2+ N + 2N1/2) x 2

新兴测试技术

三维分层测试技术(成熟度 TRL 8):针对 HBM3 等 3D 堆叠存储器,开发基于 XYZ 三维地址映射的测试图形,通过多通道探针卡(通道间距 100 μm,同步精度 ±3 ps)实现 8 层 Die 同步激励。实测表明,该技术将层间串扰故障检测效率提升 5 倍,已应用于 12 层堆叠的 HBM2e 器件测试,漏检率从 0.5% 降至 0.05%。

机器学习优化图形(TRL 7):利用历史故障数据训练神经网络,动态生成针对特定工艺缺陷的测试向量。例如,针对 7 nm FinFET 工艺的随机栅极隧穿效应,生成的测试图形包含高频翻转(>1 GHz)与电压边沿扫描序列,相比传统 ATPG 工具,故障检测时间缩短 40%,覆盖率提升 3%。

光子辅助测试(TRL 6):采用硅光探针(波长 1310 nm,调制速率 25 Gbps)传输并行测试向量,通过光电转换模块(损耗 < 2 dB)实现电信号加载。该技术已在 22nm 存储控制器测试中验证,相比传统电子测试,其信号完整性提升 20%,但光探针校准精度(±5 μm)仍需进一步优化。

-

芯片

+关注

关注

463文章

54441浏览量

469405 -

半导体

+关注

关注

339文章

31248浏览量

266590 -

工艺

+关注

关注

4文章

720浏览量

30393 -

硅晶圆

+关注

关注

4文章

276浏览量

22193

原文标题:晶圆拣选测试类型

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

什么是晶圆测试?怎样进行晶圆测试?

晶圆测试探针台的组成以及晶圆测试的重要性和要求

晶圆清洗工艺有哪些类型

晶圆拣选测试类型

晶圆拣选测试类型

评论