台积电目前正在圣克拉拉举办第24届年度技术研讨会,它刚刚发布了一个可以为显卡带来革命性变革的技术Wafer-on-Wafer (WoW,堆叠晶圆)技术。顾名思义,WoW的工作方式是垂直堆叠层,而不是将它们水平放置在电路板上,就像3D NAND闪存在现代固态驱动器中堆叠的方式一样。这意味Nvidia和AMD GPU不需要增加其物理尺寸或缩小制造工艺即可获性能提升。

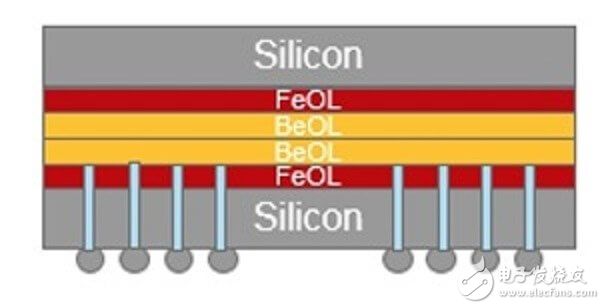

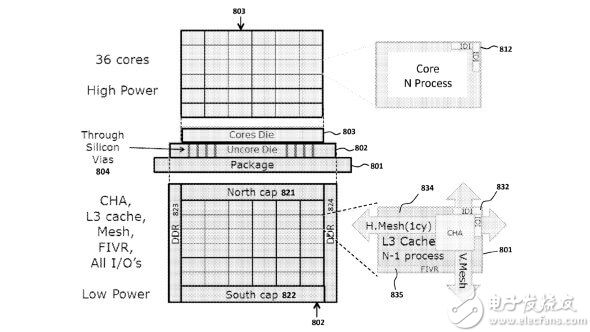

Wafer-on-Wafer (WoW,堆叠晶圆)技术通过使用形成硅通孔(TSV)连接的10微米孔彼此接触。台积电的合作伙伴Cadence解释说,Wafer-on-Wafer (WoW,堆叠晶圆)设计可以放置在中介层上,将一个连接路由到另一个连接,创建一个双晶立方体。甚至可以使用WoW方法垂直堆叠两个以上的晶圆。

该技术将允许更多的内核被塞入一个封装中,并且意味着每个晶片可以非常快速并且以最小的延迟相互通信。尤其令人感兴趣的是,制造商可以使用WoW的方式将两个GPU放在一张卡上,并将其作为产品更新发布,从而创建基本上两个GPU,而不会将其显示为操作系统的多GPU设置。

WoW现在最大的问题是晶圆产量。当它们被粘合在一起时,如果只有一个晶圆坏了,那么即使两个晶圆都没有问题,它们也必须被丢弃。这意味着该工艺需要在具有高成品率的生产节点上使用,例如台积电的16纳米工艺,以降低成本。不过,该公司的目标是在未来的7nm和5nm制造工艺节点上使用WoW技术。

-

台积电

+关注

关注

44文章

5810浏览量

177054

发布评论请先 登录

台积电Q3净利润4523亿元新台币 英伟达或取代苹果成台积电最大客户

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

化圆为方,台积电整合推出最先进CoPoS半导体封装

台积电战略收缩:两年内逐步关停6英寸晶圆产线

台积电Q2净利润3982.7亿新台币 暴增60% 创历史新高

wafer晶圆厚度(THK)翘曲度(Warp)弯曲度(Bow)等数据测量的设备

台积电的堆叠晶圆技术可以将NVIDIA和AMD GPU性能提高一倍

台积电的堆叠晶圆技术可以将NVIDIA和AMD GPU性能提高一倍

评论