本文对贴片厂贴回来的电路板出现芯片引脚间的连锡问题、PCB板(电路板)的阻焊桥脱落有一定意义,特别是做电子产品的工程师强烈建议阅读、而对于个人DIY的电子玩家也可以了解这些概念。

1.阻焊桥的作用与工艺生产能力

1.1.阻焊桥的定义与作用

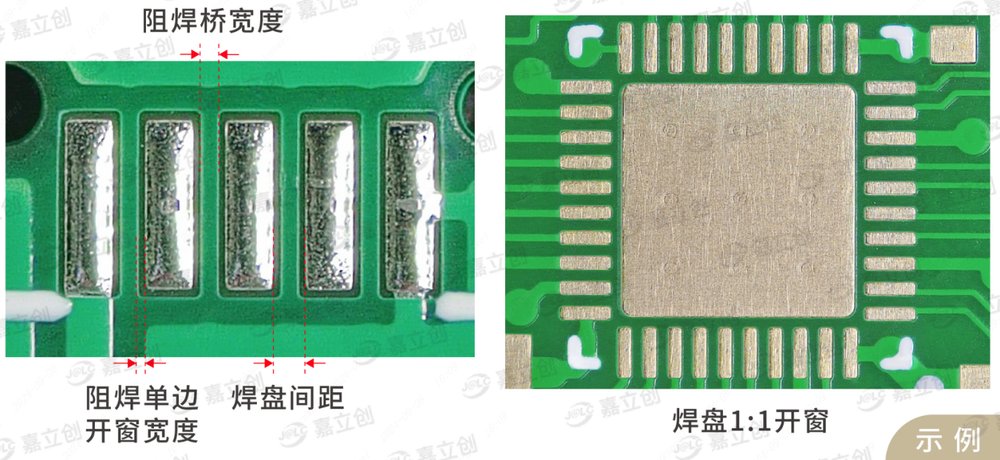

阻焊桥(又称绿油桥或阻焊坝),指的是表面贴装器件(SMD)焊盘之间的阻焊油墨。阻焊桥的作用是用于防止SDM焊盘(特别是IC封装)间距过小而导致焊接桥连短路,阻止焊料流动。

在日常开发中,我们有两种选择:

一种是开通窗去除阻焊桥:对整个芯片引脚区域进行阻焊开窗,像处理金手指一样,让IC引脚之间没有绿桥,手工焊接时还不觉的有问题,但是在量产,SMT贴片的时候,会出现芯片引脚之间的连锡问题。那就需要贴片厂的工作人员对每一块电路板进行检查(不过本来也应该要检查),但是人工检查总会有遗漏,是不是就可能发生把有问题的电路板寄到你们公司啦,这个时候就会去找贴片厂的麻烦。之后省略一万字,自己领悟。这种方法不建议。

另一种保留阻焊桥:如果我们没有对芯片的引脚焊盘区域进行开窗,默认就是保留阻焊桥的,但是,能不能真的保留打个问号?比如阻焊桥只有2mil宽(1mil=0.0254mm),那么工艺水平达不到啊,就像芯片说要做到3nm,5nm工艺,甚至1nm工艺,现有工艺水平达不到啊。所以阻焊桥能不能成功保留还是需要斟酌考虑的。

1.2.工艺生产能力

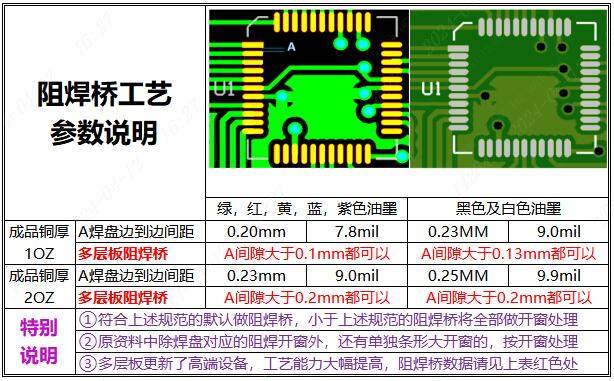

不同厂家的生产工艺不一样,这里我以嘉立创官网上展示的阻焊桥生产工艺能力进行分析:

一般电路板的铜厚默认就是1oz,那就以此来分析吧,

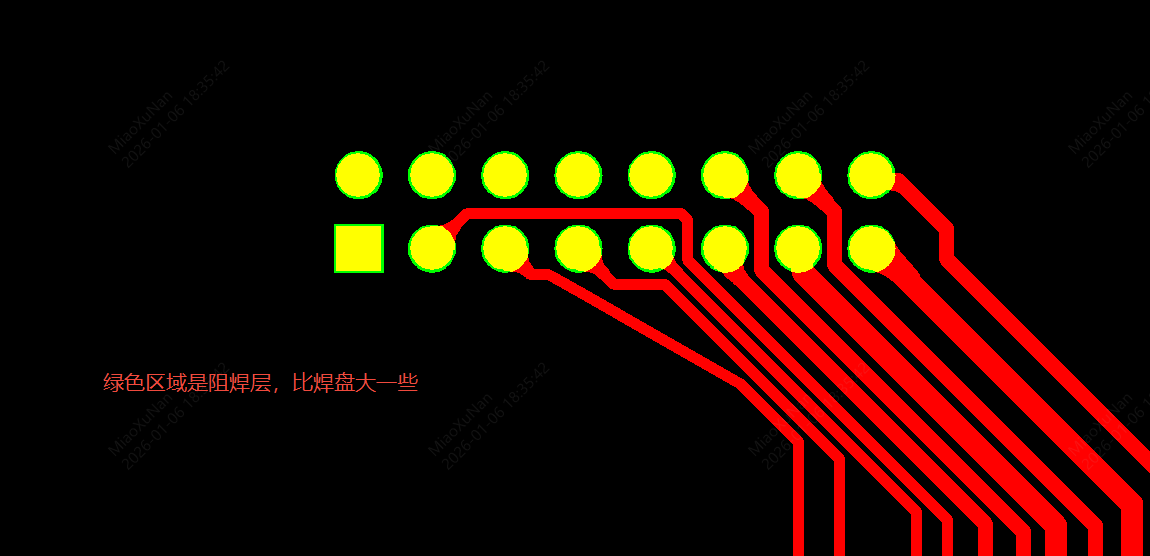

图中“A焊盘边到边间距”其实就是阻焊桥的宽度。为什么这里多层板的阻焊桥间隙可以做到0.1mm呢,因为所用生产工艺不同,导致的工艺能力不同,单双层板用的传统的CCD曝光机,而多层板(四层及以上板子层数)用的LDI阻焊曝光机;

传统的CCD曝光机阻焊对位存在一定的公差,为了避免焊盘被阻焊油墨覆盖,在设计阻焊层时,阻焊开窗通常要比焊盘单边大0.05mm,也就是大约2mil,以减少阻焊对位公差对产品良率造成影响。

可以看到,阻焊桥宽度和阻焊单边开窗宽度,两个参数是一个制约的关系,阻焊单边开窗宽度大,对应的阻焊桥宽度就会变小。

而LDI(激光直接成像)阻焊曝光机生产电路板时,减少了传统曝光技术和CCD曝光技术中因菲林光绘和对位的偏差,让阻焊精度更高。(就可以实现精准的1:1阻焊与焊盘开窗,也就是阻焊开窗和焊盘一样大,使用LDI可以缩小到0mm)。

但是相邻焊盘间的距离小于制作阻焊桥所需的最小值,在PCB的设计端仍然有阻焊桥,那么PCB成品可能会因为阻焊桥脱落等不良隐患。

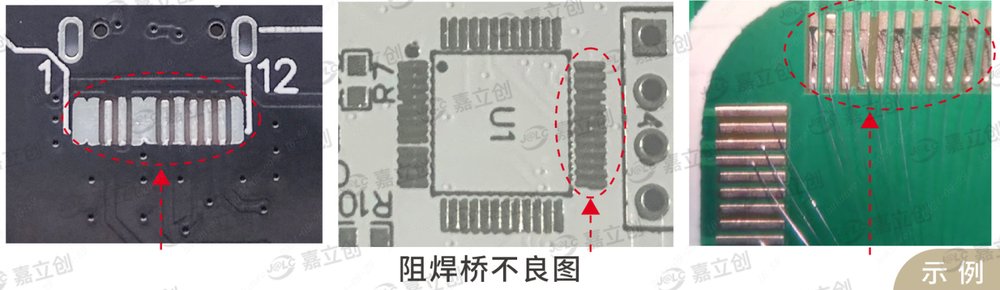

下面放一些阻焊桥不良的图片:

从图片可以看到,存在阻焊桥脱落,两个引脚焊盘连锡的情况,究其原因就是阻焊桥宽度太窄,小于最小工艺参数导致的。那如何避免出现这种现象呢,就要从设计端和制造端两个方面考虑了。

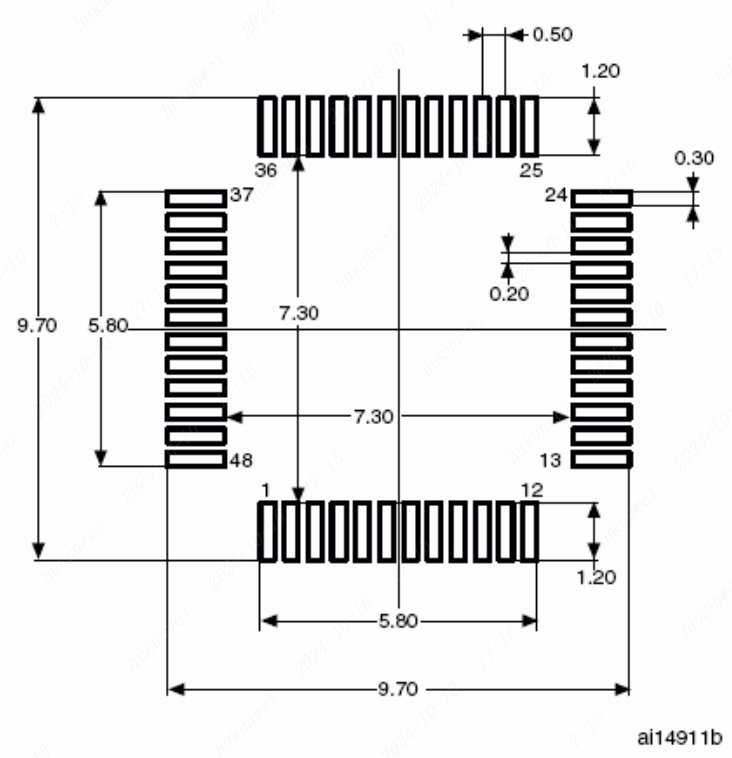

2.芯片IC的阻焊桥宽度

特意找了一下STM32F103c8t6,LQFP48引脚的封装的引脚间距,可以下载你要用的芯片的数据手册,注意:是数据手册,不是参考手册哦。在数据手册里面封装特性这一章节,可以看到要使用的芯片两个引脚之间的间距是多少。这个图可以看出STM32F103c8t6这款芯片两个引脚之间的中心间距是0.5mm,边缘间距是0.2mm。

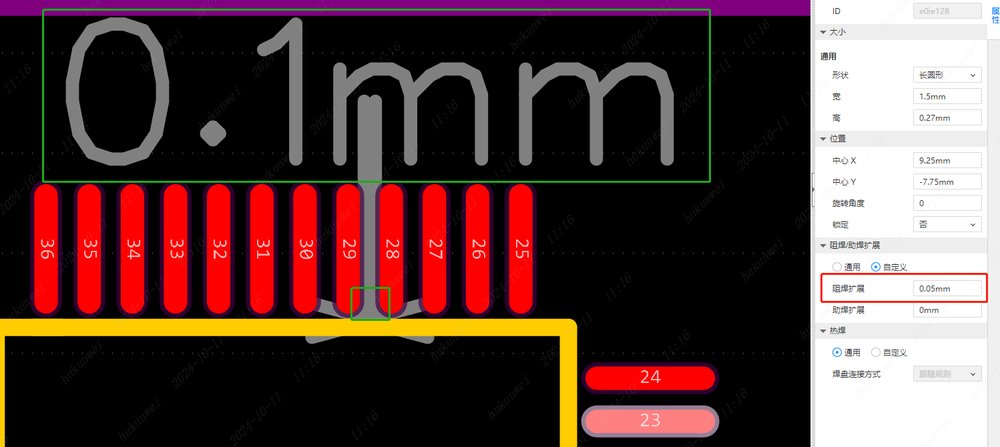

由上文提到的CCD曝光技术分析,会有对位误差,所以在画PCB封装的时候,阻焊开窗层会比线路层略微大一点,那么大多少呢,平常设计中可能直接用的其他人的器件库没注意到这些细节。这里我从就JLC-EDA里面直接找了STM32F103c8t6这款芯片,打开它的封装进行了查看:

这里我们可以看到,这个芯片的阻焊扩展默认宽度是0.05mm,那么引脚左右就要0.1mm,通过理论计算阻焊桥的宽度就剩下0.1mm,同时我也测了一下阻焊桥之间的宽度刚好是0.1mm,这个参数刚好卡在了1oz铜厚的极限值,生产出来的高多层板不会出现阻焊桥脱落的问题。

但是你选用的芯片引脚距离比0.2mm小,或者要生产2oz的铜厚的产品呢,或者你选用的厂家仍然用的是CCD曝光技术,那就会造成阻焊桥不良的情况。

3.PCB阻焊桥设计建议

1.对于硬件工程师,特别是负责PCBLayout或者可制造性分析部分的,要了解清楚板厂的工艺水平,对你要制造的电路板用什么工艺技术,要摸清楚。如嘉立创在多层板使用的是LDI曝光技术,那么对于一些引脚间距小于0.2mm的芯片设计时可以减小阻焊扩展宽度,那么阻焊桥的宽度就会增加。就不会出现阻焊桥脱落的问题。

2.如果所选用的芯片间的阻焊桥无论怎么设计都不满足工厂最小阻焊桥的设计工艺,那么就要更换这个芯片的封装类型或者更换所选芯片了。

综上所述:在设计阻焊桥时,不仅要考虑芯片焊盘之间的宽度,还要考虑板厂所使用的工艺。

审核编辑 黄宇

-

TLDI

+关注

关注

0文章

5浏览量

2172 -

PCB

+关注

关注

1文章

2355浏览量

13204 -

阻焊

+关注

关注

0文章

48浏览量

1234

发布评论请先 登录

SMT贴片加工对PCB的基本要求

FPC天线焊盘为何脱落?实验数据对比:压延铜 vs 电解铜

PCB阻焊覆盖的唯一依据:Gerber文件

PCB阻焊层与助焊层的本质区别

浅谈各类锡焊工艺对PCB的影响

哪种工艺更适合高密度PCB?

线路板阻焊工艺对PCB的可靠性有何影响?

什么是SMD&NSMD,怎么区分呢?

PCB设计中过孔为什么要错开焊盘位置?

银线二焊键合点剥离失效原因:镀银层结合力差VS银线键合工艺待优化!

PCB阻焊桥脱落与LDI工艺

PCB阻焊桥脱落与LDI工艺

评论