概述

MAX9310是一种快速,低扭曲1:5差分驱动器,具有可选的LVPECL/HSTL输入端和LVDS输出端,设计应用于时钟分配。这种器件的特点是具有345ps的极低传输延迟和45.5mA的电源电流。

MAX9310工作在2.375V至2.625V电源范围,适用于2.5V系统。通过2:1输入多路复用器,选择两路差分输入中的一路。输入选择是由CLKSEL引脚控制,这种器件也具有同步使能功能。

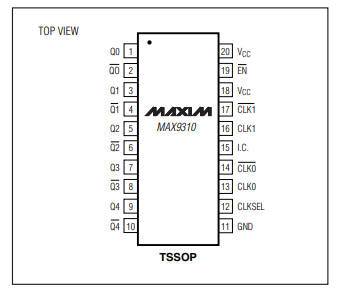

MAX9310提供节省空间的20引脚TSSOP封装,可工作在-40°C至+85°C的宽温度范围。

数据表:*附件:MAX9310 1比5时钟驱动器,可选的LVPECL输入与LVDS输出技术手册.pdf

应用

- 自动测试设备(ATE)

- 局端背板时钟分配

- 数据和时钟驱动器与缓冲器

- DSLAM

- 无线基站

特性

- 保证1.0GHz工作频率

- 8ps输出至输出扭曲

- 345ps传输延迟

- 接受LVPECL和差分HSTL输入电平

- 同步输出使能/禁止

- 两路可选择的差分输入

- 2.375V至2.625V电源电压

- ESD保护:±2kV (人体模型)

- 输入开路时,输入偏置电阻驱动输出为低

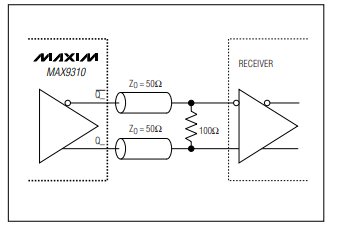

典型应用电路

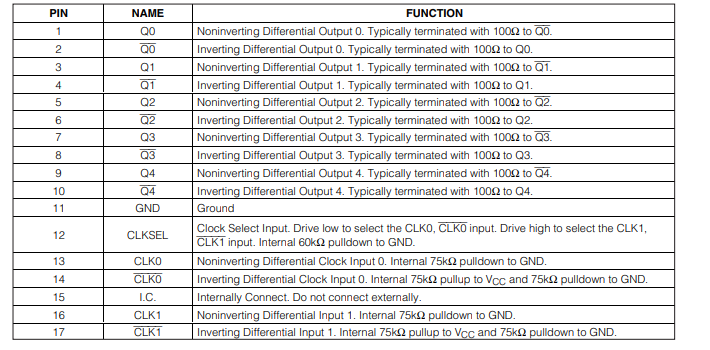

引脚配置描述

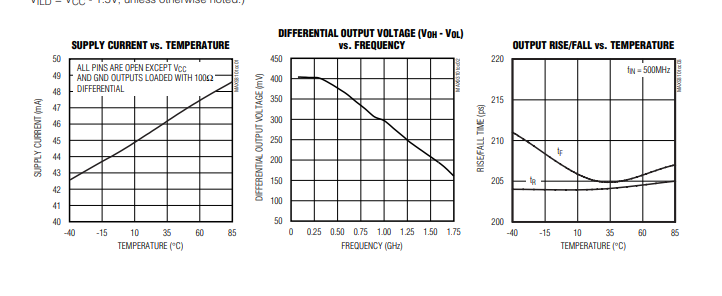

典型操作特性

详细说明

MAX9310是一款低偏斜1:5差分驱动器,具有两个可选的LVPECL输入和LVDS输出,专为时钟分配应用而设计。选通时钟接受差分输入信号,并将其复制到五个独立的差分LVDS输出。输入由内部偏置电阻进行偏置,这样当输入开路时,输出为差分高电平。输出驱动器保证在高达1.0GHz的频率下工作,LVDS输出电平符合EIA/TIA - 644标准。

MAX9310的设计工作电压范围为2.375V至2.625V,标称值为2.5V。

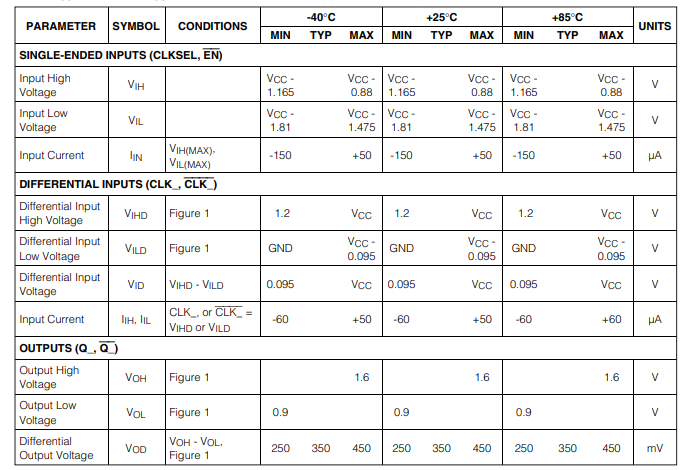

差分LVPECL输入

MAX9310有两个差分LVPECL输入端口,每个差分输入对都有独立的端接。一个选择引脚(CLKSEL)用于激活所需的输入。施加到输入的差分信号的最大幅度为Vcc。差分信号的高电平和低电平(VHD和VLD)以及差分输入电压(VIH - VIL)可同时施加。

同步使能

MAX9310的输出在差分低电平状态下同步使能和禁用,以消除选通时钟脉冲中的短脉冲。EN连接到输入的边沿触发D触发器的置位端。上电后,将EN驱动为低电平并切换时钟频率以启用输出。输出在所选输入时钟的下降沿使能。EN下降沿时,输出设置为所选输入时钟下降沿的差分低电平状态(图2)。

输入偏置电阻

内部偏置电阻确保在输入(差分)未连接的情况下输出为低电平。反相输入(CLK_)通过一个75kΩ下拉电阻偏置到地,同相输入(CLK_)通过一个75kΩ上拉电阻偏置到Vcc。

差分LVDS输出

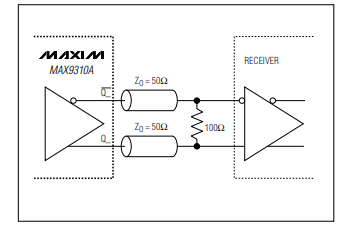

LVDS输出必须按照典型应用电路所示,在Q_和Q_之间用100Ω电阻进行端接。输出具有短路保护功能。

应用信息

电源去耦

将每个Vcc引脚通过0.1μF和0.01μF的高频表面贴装陶瓷电容旁路至地,尽可能将电容靠近器件安装,0.01μF电容最靠近器件。使用多个并联过孔,以最小化寄生电感并减少大电流瞬变引起的电源波动。

受控阻抗走线

输入和输出走线特性会影响MAX9310的性能。将高频输入和输出连接到50Ω特性阻抗走线,尽量缩短走线长度,以防止阻抗不连续。通过匹配电缆和连接器保持50Ω特性阻抗,以减少反射。通过匹配差分对内走线的电气长度来减少偏移。

输出端接

按照典型应用电路所示,在Q_和Q_之间用100Ω电阻对输出进行端接。

-

驱动器

+关注

关注

54文章

9111浏览量

156454 -

lvds

+关注

关注

2文章

1241浏览量

70212 -

LVPECL

+关注

关注

2文章

77浏览量

18897 -

差分驱动器

+关注

关注

0文章

69浏览量

15715

发布评论请先 登录

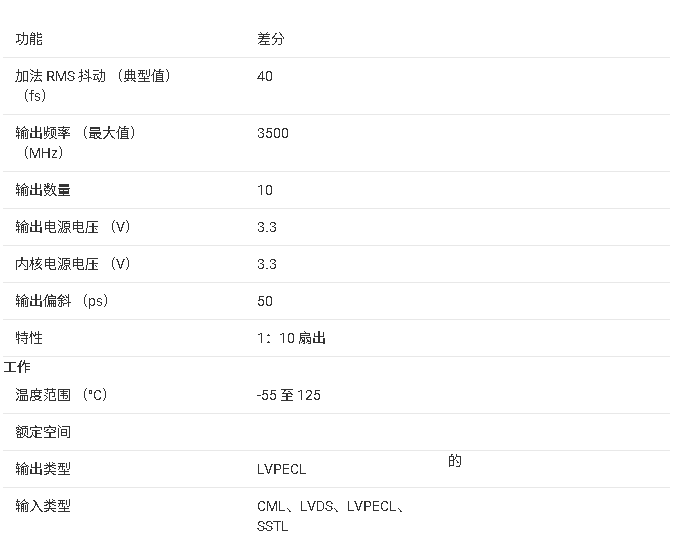

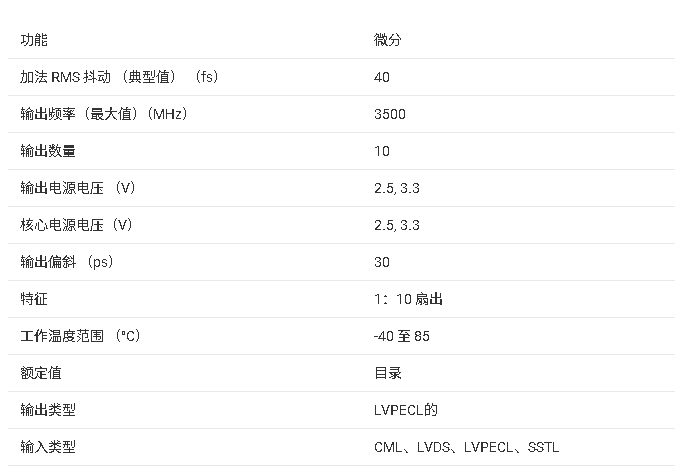

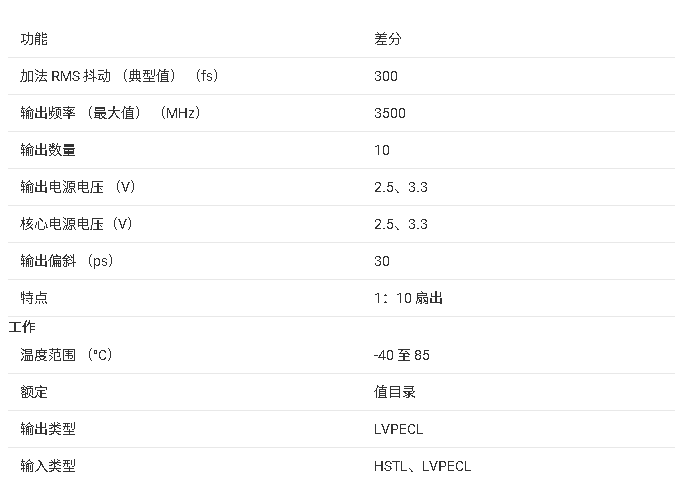

CDCLVP111-SP具有可选输入时钟驱动器的低电压1:10 LVPECL数据表

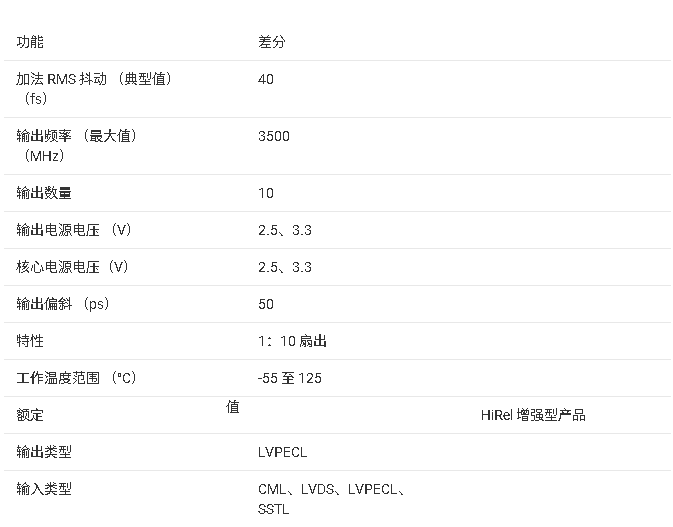

CDCLVP111低压1:10 LVPECL,内置可选输入时钟驱动器数据表

CDCVF111 1:9差分LVPECL时钟驱动器数据表

MAX9310 1:5时钟驱动器,可选的LVPECL输入与LVDS输出技术手册

MAX9310 1:5时钟驱动器,可选的LVPECL输入与LVDS输出技术手册

评论