相位累加器

关于相位累加器的使用,我不确定放在FPGA专题中是否合适,但是因为确实很多应用都是在FPGA上面的,所以暂时先这样定吧。

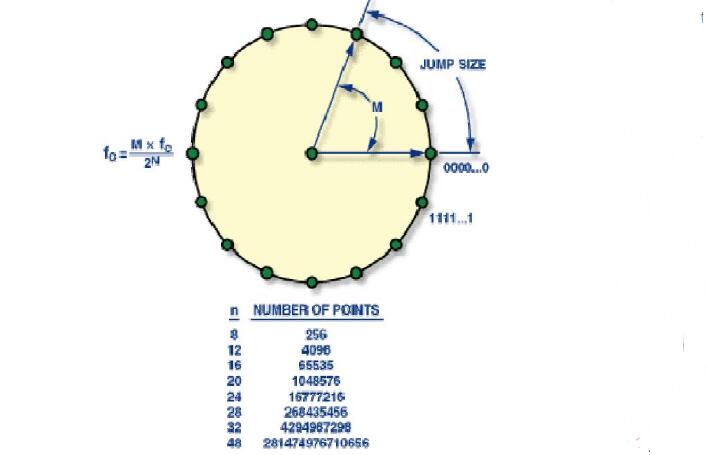

标题中所提到的DDS,我感觉这两个放一起也可以,因为DDS的核心思想就是使用的相位累加器。那么这玩意儿的作用是啥?简单来说就是在FPGA工作主频之下,可以生成任意频率的周期信号出来。

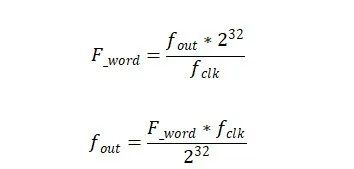

定义一个32bit的频率字Acc

定义一个32bit的频率控制字F_word

假设系统时钟(准确的说法应该是相位累加器的参考时钟)fclk

需要产生的时钟频率 fout

根据公式:

上面两个公式可以在已知需要获得的输出频率的基础上,计算得到需要的频率控制字。

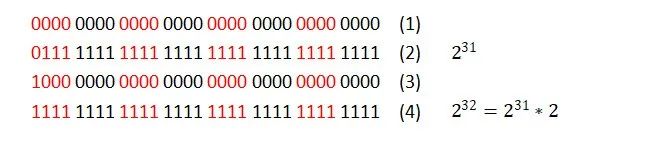

然后看下频率控制字是怎么用的,这里就是用的相位累加器的原理。

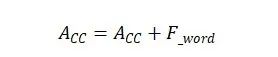

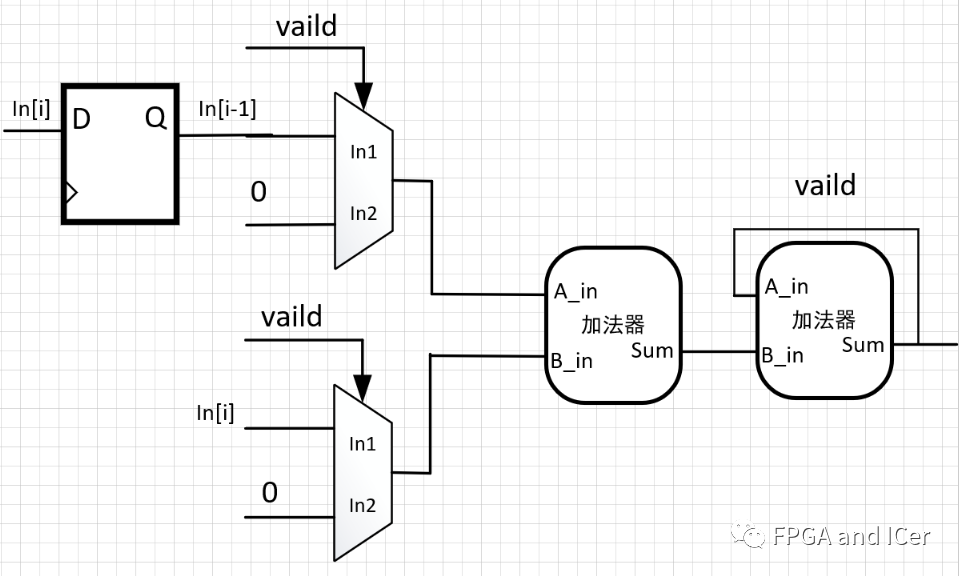

上式是一个累加的过程,实现的原理是在一个32bit的数据范围内,即在(0~2^32-1)这个范围内进行累加,累加的步进是F_word;完成这一个范围内的累加之后,用时为T,那么这个T的倒数就是我们需要的fout了。完成一次累加之后,频率字Acc会溢出,然后进入下一次累加,形成下一个周期信号;如此重复进行后就是一个振荡的周期信号了。

那么这个周期信号该怎么表示出来呢?上面说了,完成(0~2^32-1)的累加过程是一个周期T,那么在这个周期里面,应该会有一次信号翻转。即高电平时间T/2,低电平时间也是T/2。

对于一个32bit的数,当低31位不断累加,直到第32bit从0跳转到1的时间段内,就是用了T/2的时间;当第32bit变成1之后,低31位又开始累加,直到数据溢出,又是T/2的时间。

如果不能理解,结合下图

也就是说,在整个累加过程中,我们只要判断Acc的最高的情况,在0~T/2时间内,最高位为0;

在T/2~T的时间内,最高位为1;这样就是会产生一个fout的方波信号了。

assign clk_out=Acc(31);

这样的clk_out就是需要的fout了。

亦或者,直接对Acc的值进行判断

always@(posedgeclkornegedgerst)if(!rst) clk_out <= 1'b0;elseif(Acc <= 32'h7fffffff) clk_out <= 1'b0;elseif(Acc >32'h7fffffff) clk_out <= 1'b1;

同样可以输出fout。

采样率

同时,想说一下关于采样率的问题。

常见于ADC这类芯片中,例如,某ADC芯片的采样率为1MHz,意思是每秒可以采样1M个点,那么采一个点所要花的时间是(1/1M) 秒。

在做FFT的时候,通常需要采集一个完整的正弦波,来进行FFT,这里就会涉及采样率的问题。

假如一个正弦波的频率为fsig=50KHz,我们需要用128个点来进行FFT,那就是要128个点采集完成这个正弦波。根据正弦波的频率可以计算出正弦波的周期Tsig=1/fsig;那么这128个点所占的时间就应该是这个周期Tsig。也就是说,采样芯片需要在Tsig时间内采集完成128个点,那么这个就可以计算出需要的采样率了。采样率设为Fs,则采一个点的时间是1/Fs;采128个点的时间就是128/Fs;则

128/Fs=1/fsig;会得出采样率Fs=128fsig;得到的是和被采样信号频率的关系;

根据奈奎斯特定律,采样频率至少要是被采样信号频率的2倍,才能获得被采样信号的有效信息,否则就会出现失真。这里其实就可以分析得到,这里的128个点其实是可以人为设定的,假如设置为N;那么最后的公式就是Fs=Nfsig 。当然,保证这里的N>2是非常有必要的。

一般来说,我们的N会取的比较大。

FFT

说到上面的信息,不得不再说下FFT

其中的参数就包括上面说的Fs、N、fsig

FFT是一种计算,采样到一个点,进行一系列的运算后,输出一个复数,假设为A+Bi;这个复数中就包含这个被采样信号sig的信息,对A和B求平方和再开根号,就是当前采样点在频谱上的幅值(注意并不是在正弦波形上的幅值),频谱上幅值最大的点出现在fsig频率处。

对于一个未知频率的正弦波信号,对其进行采样,然后进行频谱幅值的最大值筛选,可以计算出这个信号的频率。

Fs/N的意思是,对所有的N个采样点,用Fs的采样率来采样,则在每个点处的频率值(这个是在频域上的信息)。假设fsig出现在从0~N之间的某个点n处,则会有Fs/N*(n-1)=fsig;同样是可以计算出这个n。

-

FPGA

+关注

关注

1664文章

22502浏览量

639212 -

时钟

+关注

关注

11文章

1999浏览量

135231 -

相位累加器

+关注

关注

0文章

11浏览量

9365

原文标题:相位累加器

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于相位累加器的任意分频原理解析

累加器verilog语言编程问题

FPGA实现NCO中相位累加器的输出和查找表地址什么关系?

请问AD9910并行端口控制相位时,并行数据是输入到相位累加器中还是输入到相位偏移字中?

dds相位累加器没有提高采样频率

计算机累加器有加法器功能吗,累加器是什么_累加器的作用及原理介绍 精选资料推荐

累加器A的主要作用是什么_一文解析累加器a和acc的区别

32位数字相位累加器的程序和工程文件免费下载

相位累加器的实现原理

相位累加器的实现原理

评论