NVM Express(NVMe)是一种高性能、可扩展的接口协议,用于通过PCI express(PCIe)总线,实现主机软件与NVM设备之间的通信。目前,由于NVMe SSD相比于SATA SSD具有更高的吞吐量、更快的访问速度和更低的功耗,已经被广泛应用于各种计算领域和存储系统。

NVMe队列

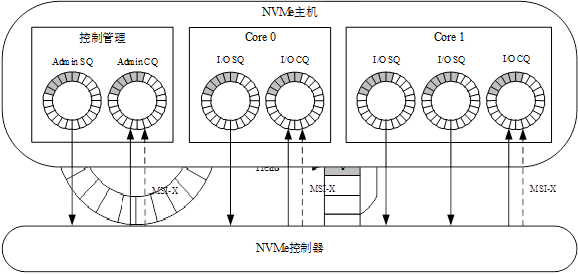

NVMe协议采用成对的提交队列(Submission Queue,SQ)和完成队列(Completion Queue,CQ)机制。SQ用于存放提交命令,而CQ则用于存放完成信息。队列状态信息通过门铃寄存器(Door Bell,DB)来检测。这两个队列采用了环形队列结构,队列可以映射到任何PCIe可访问的内存中,通常放在主机侧内存。对于提交队列,主机端是生产者,NVMe SSD是消费者。完成队列的情况刚好相反。因此SQ Tail指针和CQ Head指针由主机更新,而其他两个指针由NVMe控制器更新。NVMe的队列结构如图1所示。

图1 队列示意图

NVMe队列的深度是固定的,通过Tail和Head来分别指向队列的首尾位置,队列实际可用的大小是队列大小减1,当Head条目指针等于Tail条目指针时,队列为空。当Head条目指针比Tail条目指针多一个时,队列为满。

NVMe协议中根据命令类型将队列分为了Admin队列和I/O队列,Admin队列用来缓存管理Admin命令,如获取SSD属性、创建I/O队列等。而I/O队列用来缓存管理I/O命令,如读、写、识别等。在一个系统中只能有一对Admin SQ/CQ,但可以存在多对IO SQ/CQ。Admin SQ/CQ仅用来进行Admin命令的交互,I/O SQ/CQ仅用来进行I/O命令的交互。对于多核系统来说,每个核内虽然只有1个I/O CQ,但是可以存在多个I/O SQ,如图2所示。

图2 NVMe多队列示意图

由于Host端可能存在多个流水线,多队列的设计可以让系统的性能最大化。同时,可以通过对不同的队列设置不同的优先级,来保证高优先级队列的命令更快完成。NVMe协议中规定Admin SQ/CQ的队列深度最大可以支持4096(4K),I/O SQ/CQ的队列深度最大可以支持65536(64K)。在一个实际设计中,SQ的个数和深度的设置可以根据项目需求和硬件资源进行配置。队列深度的设置主要和系统中队列消费者和生产者之间的速率有关。

2. NVMe分层结构

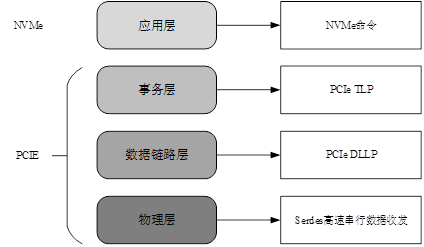

NVMe协议栈结构分为应用层和传输层两个层次。在应用层中实现NVMe命令生成、队列管理和流程控制,而传输层则借助PCIe协议进行实现。PCIe协议分为三层,即事务层、数据链路层和物理层。事务层负责将数据传输请求和响应打包成事务进行传输,数据链路层则负责数据传输的可靠性和流控制,通过链路层控制器(Link Layer Controller, LLC)实现。物理层则负责物理传输,包括电信号的发射和接收、时序控制和线路管理等。其分层结构图如图3所示。首先,在应用层生成NVMe命令传输至事务层。其次,在事务层会对上层传输的数据添加首部和校验,封装成TLP(Transaction Level Packet)传输至数据链路层。然后,在数据链路层会对TLP添加序列号和校验,封装成DLLP。最后,在物理层对数据包进行编码和并转串处理后,通过SerDes(Serializer/Deserializer)将数据发送至PCIe链路中。

图3 分层结构

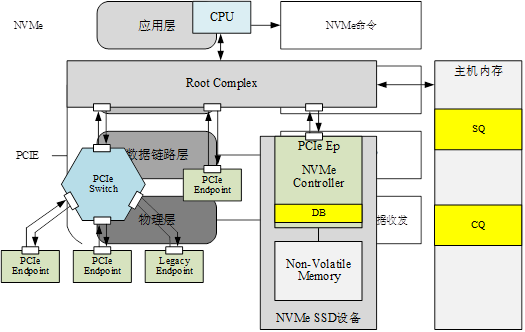

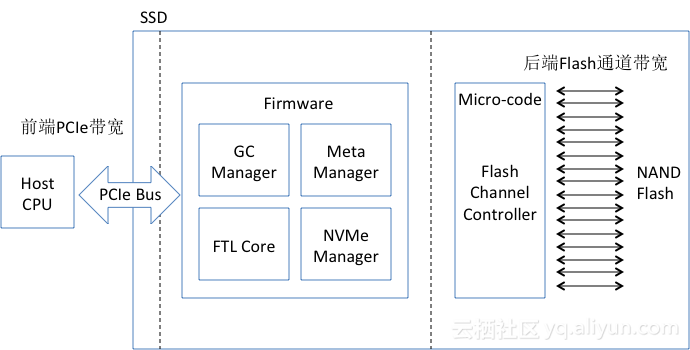

由于NVMe协议是基于PCIe协议实现的,下面通过在PCIe拓扑结构中介绍NVMe协议中的SQ、CQ和DB的位置,以及数据在Host和NVMe SSD之间的传输流程。NVMe SSD在PCIe拓扑结构中的位置如图4所示。

图4 PCIe拓扑结构

PCIe的拓扑结构由三部分组成,根联合体(Root Complex, RC)、PCIe交换器(PCIe Switch)和端点(Endpoint, EP)。根联合体位于拓扑结构的根部,最靠近CPU。端点设备位于PCIe的端末。交换机位于根联合体和端点设备之间。PCIe使用串行链路连接,一个链路的两端只能有两个设备。因此PCIe需要通过PCIe Switch扩展PCIe链路后,才能连接多个EP设备。在NVMe存储结构中,NVMe SSD也作为PCIe的一个EP端挂载在RC上。

NVMe协议中的SQ和CQ位于Host内存中,主机在初始化时根据队列的个数和深度在主机内存开辟出相应的内存空间,来存放SQ、CQ命令。DB寄存器位于NVMe SSD中,且被映射到BAR(Base Address Register)空间中,Host可以通过访问BAR空间来更新DB寄存器的值。

当Host需要向NVMe SSD发送命令时,首先将命令存放在主机内存开辟的SQ区域中,其次通过访问BAR空间的DB寄存器来告诉NVMe SSD到主机端内存区域取走待执行的命令。待命令执行完成后,NVMe SSD向主机内存的CQ区域写入完成命令。

3. NVMe数据结构

NVMe协议中规定每个提交命令的大小为64字节,完成命令大小为16字节,NVMe命令分为Admin和IO两类,NVMe的数据块组织方式有PRP和SGL两种。提交命令的格式如图5所示。

图5 提交命令数据格式

NVMe提交命令的数据格式属性如下:

(1)Opcode(OPC):命令操作码,不同操作命令的Opcode都有对应的值;

(2)Fused Operation(FUSE):融合操作,可选字段,用于将两个命令融合为一条命令;

(3)PRP or SGL for Data Transfer(PSDT):PRP或SGL数据传输;

(4)Command Identifier(CID):命令ID;

(5)Namespace Identifier(NSID):命名空间ID;

(6)Metadata Pointer(MPTR):元数据指针;

(7)PRP Entry 1/2:物理区域页项;

(8)SGL Entry:散列聚合列表。

Admin命令集定义了可以提交到Admin SQ的命令。NVM命令集定义了可以提交到IO SQ的命令。表1和表2分别列出了Admin命令集和NVM命令集中的常用命令、操作码和简要的功能描述。

表1Admin命令集

| 命令 | 必选/可选 | Opcode | 功能 |

| 删除I/O提交队列 | 必选 | 00h | 删除I/O提交队列 |

| 创建I/O提交队列 | 必选 | 01h | 创建I/O提交队列 |

| 删除I/O完成队列 | 必选 | 03h | 删除I/O完成队列 |

| 创建I/O完成队列 | 必选 | 04h | 创建I/O完成队列 |

| 识别 | 必选 | 05h | 返回描述设备的信息 |

| 设置特性 | 必选 | 07h | 设置SSD控制器特性 |

| 获取特性 | 必选 | 08h | 读取SSD控制器特性 |

| 获取日志页 | 必选 | 02h | 读取日志页表,如SMART日志 |

| 命令空间管理 | 可选 | 0Ah | 管理命令空间,如创建和删除操作 |

表2NVMe命令集

| 命令 | 必选/可选 | Opcode | 功能 |

| 清除 | 必选 | 00h | 将缓存内容刷新至非易失性存储器 |

| 写 | 必选 | 01h | 将数据写入指定逻辑块 |

| 读 | 必选 | 02h | 从指定逻辑块读取数据 |

| 写入不可纠正的错误 | 必选 | 03h | 标记范围内的逻辑块无效 |

| 写入全0 | 可选 | 05h | 将指定的逻辑块值设置为0 |

| 数据集管理 | 可选 | 06h | 指定逻辑块属性 |

接下来介绍NVMe协议中的寻址方式。在NVMe协议中定义了两种寻址方式,PRP和SGL。通过PRP和SGL来记录Host内存中物理页的位置。NVMe命令中的PRP和SGL字段用来向NVMe SSD传递将要读写数据在内存中的位置。NVMe协议中规定Admin命令只能通过PRP告诉NVMe SSD命令在内存中物理地址。而SGL主要是在NVMeoF中使用,因此本设计将采用PRP寻址方式。

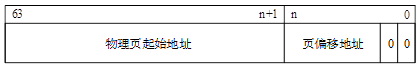

Host可以通过配置NVMe Controller的CC.MPS寄存器来设定物理页的大小,物理页的大小可设定的范围是4KB~128MB之间。物理页对应的地址记录在PRP Entry中,PRP Entry的数据格式。PRP Entry的数据格式由物理页起始地址和页偏移地址两部分组成,如图6所示。由于物理地址只能是四字节对齐,因此将偏移地址的最低2bit置为0。此外,图6中n的取值与设置的物理页大小有关,例如,将物理页大小设置为4KB,则n=11,通过偏移地址[11:2]来表示在一个内存页内的偏移地址。

图6 PRP Entry格式

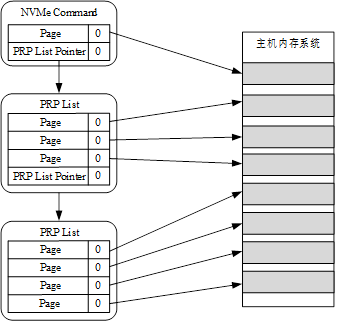

一个PRP Entry只能指向一个物理页。NVMe协议中只定义了两个PRP Entry,当传输数据量大小大于两个内存页大小时,PRP Entry2将不指向物理页,而是指向由若干个PRP组成的PRP List。如图7所示,NVMe命令中的PRP1指向第一个内存页,PRP2指向一个新的PRP链表的首地址。如果需要指定更大的内存空间可以通过每一个PRP List的最后一个PRP Entry指向新的PRP List。

图7 PRP原理示意图

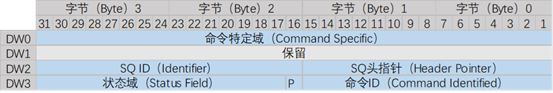

完成命令的数据格式如图8所示。

图8 完成命令数据格式

NVMe完成队列的命令格式属性如下:

(1)SQ Header pointer:SQ头指针;

(2)SQ Identifier:SQ ID;

(3)Command Identifier:命令ID;

(4)P:相位标志phase tag,完成队列没有head/tail交互,通过相位标志实现完成队列项的释放;

(5)Status Field:状态域。

NVMe工作流程

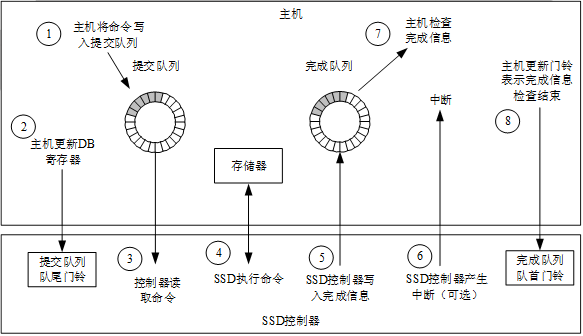

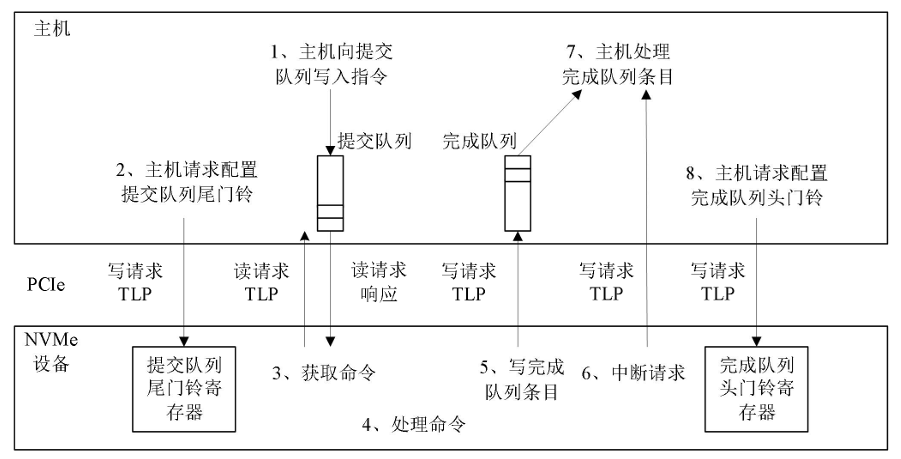

NVMe协议中的Admin命令和IO命令执行流程相同,主要通过SQ、CQ和DB寄存器三个关键部件之间的相互协作来完成。NVMe的命令处理流程分为了8个步骤,如图9所示。

图9 NVMe命令处理流程

Host和SSD之间通过更新DB(DoorBell)寄存器的值来实现队列信息的交互。每个SQ和CQ都拥有一个Head寄存器和Tail寄存器。对于SQ而言,Host是生产者,负责向队列发送提交命令,SSD是消费者,负责执行命令,因此Host负责更新Tail DB寄存器,SSD负责更新Head DB寄存器。对于CQ而言,SSD是生产者,负责向队列发送完成命令,Host是消费者,负责检查完成信息,因此SSD负责更新Tail DB寄存器,Host负责更新Head DB寄存器。而DB寄存器都存在于SSD内,且只能进行写操作,不能进行读操作。因此NVMe协议中规定SSD通过完成信息向Host反馈CQ Tail和SQ Head寄存器的值。

NVMe命令处理的步骤如下:

(1)主机提交新的NVMe命令。主机生成新的NVMe命令并添加ID号后,将其存放在SQ Tail指针指向的内存空间中;

(2)主机更新SQ Tail DB寄存器。主机通过Memory Write事务更新SQ Tail DB寄存器的值,以通知NVMe SSD控制器去主机端读取SQ中缓存的命令;

(3)NVMe SSD读取命令。NVMe SSD控制器检测到SQ Tail DB寄存器的变化后,通过Memory Read事务去读取SQ内缓存的命令,这个过程,NVMe SSD进行突发读取,一次读取多条命令,等待取命令完成后更新SQ Head DB寄存器的值;

(4)NVMe SSD执行命令。NVMe SSD控制器根据内部的仲裁机制来执行读取到的NVMe命令,其执行过程并不是按照队列的先后顺序来执行命令;

(5)NVMe SSD控制器将完成命令写入CQ。NVMe SSD控制器将NVMe命令的执行结果写入主机的CQ内存区域中,完成命令包括NVMe命令中的ID号和SQ Head DB寄存器的值;

(6)NVMe SSD通知主机检查完成命令。NVMe SSD控制器通过Memory Write事务向主机发出MSI-X中断信号,告知主机检查CQ中的完成信息。在本设计中,取消了完成队列的设计,而采用FPGA的并行处理方式,通过主机端实时监测CQ信息,以节省硬件资源和提高NVMe命令处理速度;

(7)主机检查完成命令。主机从CQ内存中读取完成信息,并根据状态字段判断NVMe命令的执行情况。若命令已经执行完成,主机会释放该ID号对应的提交命令空间,以便给新的命令使用;

(8)主机更新CQ Head DB寄存器。主机通过Memory Write事务更新CQ Head DB寄存器的值,以通知NVMe SSD控制器CQ中的完成信息已经检查。

对相关NVM安e设计感兴趣的可以看本博客,更多的见csdn用户: tiantianuser

或视频见B站 用户: 专注与守望

审核编辑 黄宇

-

PCIe

+关注

关注

16文章

1483浏览量

88944 -

协议分析

+关注

关注

0文章

8浏览量

7774 -

nvme

+关注

关注

0文章

301浏览量

23916

发布评论请先 登录

NVME控制器设计1

协议分析仪需要支持哪些常见协议?

PCIe协议分析仪能测试哪些设备?

NVMe高速传输之摆脱XDMA设计30: NVMe 设备模型设计

NVMe协议访问能释放存储级内存性能和存储系统的创新

如何选择合适的NVMe-over-Fabrics方案

PCIe Gen 4协议分析仪的竟然那么强大!

NVMe over Fabrics的优势是什么?

【虹科干货】FC-NVMe 介绍及性能分析

Emulex引导的光纤通道和NVMe FC协议用户指南 14.2版

NVMe协议分析

NVMe协议分析

评论