NVMe指令提交与完成机制

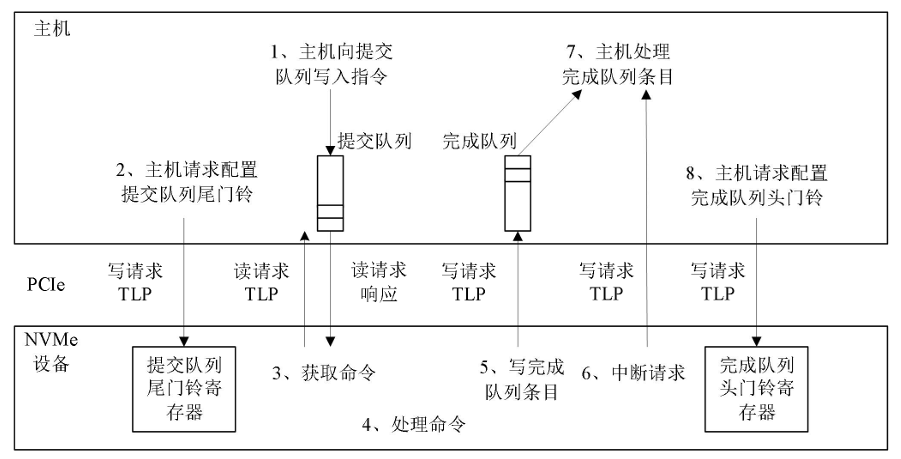

NVMe指令提交与完成机制是NVMe协议的核心,该机制制定了NVMe指令的 交互流程和处理步骤。在基于PCIe的NVMe协议中,NVMe主机控制器与NVMe 设备的交互通过PCIe进行,使用PCIe的存储读写TLP请求。指令的提交与完成机 制如图1所示,图中展示的指令提交与完成步骤如下:

图1 NVMe指令提交交与完成步骤图

(1)主机控制器向提交队列写入一个或多个提交命令;

(2)主机请求配置NVMe设备的提交队列尾门铃寄存器,表示有新的命令需要 进行处理;

(3)NVMe设备从提交队列中读取提交指令条目;

(4)NVMe继续执行获取的命令,命令可以无序完成;

(5)命令完成执行后,控制器将完成队列条目写入关联的完成队列。NVMe设 备在完成队列条目中提供最近的关联提交队列条目头指针; (6)NVMe设备可选地向主机生成一个中断,以表明有一个新的完成队列条目 要等待主机控制器使用和处理;

(7)主机控制器处理完成队列中的新完成队列条目;

(8)主机控制器请求配置完成队列头门铃寄存器,指示完成队列条目已被处理

对相关视频感兴趣者,请移步B站 搜用户名: 专注与守望

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

nvme

+关注

关注

0文章

300浏览量

23910

发布评论请先 登录

相关推荐

热点推荐

NVMe高速传输之摆脱XDMA设计54:如何测试队列管理功能2

。

如图1 所示, 删除所有提交队列和完成队列, 删除成功。 然后分别创建一个I/O 完成和提交队列, 连续多次删除, 打印信息返回错误

发表于 12-10 08:33

NVMe高速传输之摆脱XDMA设计52:主要功能测试结果与分析4(NVMe 指令提交与完成机制测试)

axis_rq 接口发起写 TLP 请求配置 Admin CQ 头门铃为 1。图 1 NVMe 写完成队列波形图

测试波形显示 NoP 逻辑加速引擎正确地执行了 NVMe 指令提交与

发表于 12-04 11:47

NVMe高速传输之摆脱XDMA设计41:队列管理功能验证与分析5

关键信号波形如图 3 所示。 在成功创建一个 I/O 完成队列和一个I/O 提交队列后, 删除 I/O 提交队列, 删除操作返回 cr_s

发表于 10-23 16:24

NVMe高速传输之摆脱XDMA设计39:队列管理功能验证与分析3

提交队列时, 返回数量错误, 并且不再生成对应 NVMe 指令, 仿真行为符合设计预期, 测试通过。

图 2 创建队列边界测试波形图三

发表于 10-20 16:01

NVMe高速传输之摆脱XDMA设计38:队列管理功能验证与分析2

波形如图1 所示。 创建深度为 1024 的 I/O 提交队列, 由于支持的最大队列深度为 1023, 所以创建返回状态 cr_status 值为 4, 表示创建深度错误, 仿真行为符合设计预期

发表于 10-15 08:14

NVMe高速传输之摆脱XDMA设计37:队列管理功能验证与分析1

队列、 删除队列、 队列边界、 操作顺序等功能的测试,待测设计的设计目标中, 提交队列的最大数量为 16, 单

发表于 10-13 11:17

NVMe高速传输之摆脱XDMA设计36:初始化功能验证与分析4

测试步骤 4 关键信号波形如图1 所示, 通过 axis_cc 接口获取 NVMe 指令后,NVMe 设备执行指令操作, 在操作完成后, 通过 axis_cq 接口向对应提交队列的完

发表于 10-11 08:22

NVMe高速传输之摆脱XDMA设计30: NVMe 设备模型设计

队列属性寄存器、Admin 提交队列地址寄存器和 Admin完成队列地址寄存器, 以及在队列工作中需要使用的门铃寄存器组。

发表于 09-29 09:31

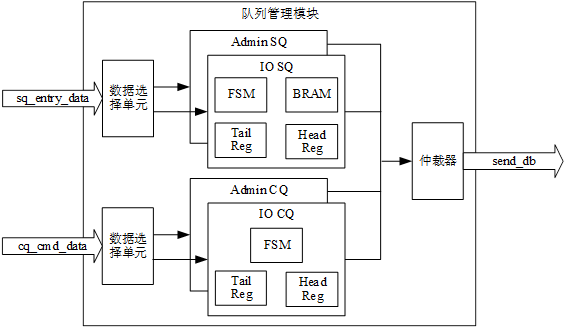

NVMe高速传输之摆脱XDMA设计九:队列管理模块设计(上)

效率和资源占用,N的最大数量为16。每一个提交队列表单包含了队列的ID、队列深度、起始偏移地址、门铃头指针、门铃尾指针、门铃地址,表单中的初始信息在

发表于 07-27 17:41

NVMe高速传输之摆脱XDMA设计之十:NVMe初始化状态机设计

DISABLE_CC状态。

RD_CAP:读控制器功能寄存器状态。该状态下读取NVMe设备的控制器功能寄存器,获取其中的Memory Page Size和支持的最大单队列深度信息,然后跳转到DISABLE_CC状态

发表于 07-05 22:03

NVMe协议分析之提交队列

NVMe协议分析之提交队列

评论