“System Level EOS Testing Method”可以翻译为:

“系统级电性过应力测试方法”

解析:

1.System Level(系统级):指在整体系统层面进行的测试,而非单个组件2。

2.EOS(Electrical Over Stress):即“电性过应力”,指电流或电压超过器件承受范围导致的损伤1。

3.Testing Method(测试方法):指具体的检测流程或技术手段6。

补充说明:

该术语通常用于电子制造或芯片测试领域,目的是通过系统级测试预防因电压/电流异常导致的硬件损坏14。

系统上常见的EOS测试端口以AC电源、电话线(RJ11)、同轴电缆(coaxial cable)以及以太网路(RJ45)最常见,这些端口因有机会布线至户外的关系,受到EOS/Surge冲击的机率也大大提升。故电子产品在安规认证阶段,都会在这些端口执行EOS/Surge这个测项,以加强端口对于外部EOS的抗干扰能力,并降低电子产品日后遇到EOS/Surge造成的损坏问题。

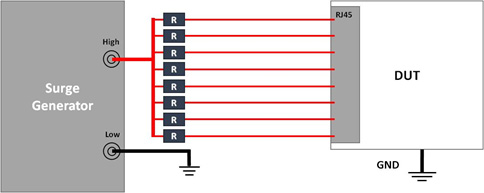

本篇文章以高速信号端口如以太网口及USB的EOS/Surge测试手法作介绍。以太网口的EOS/Surge测试标准众多,且依照不同产品的类型或应用区域而有所不同,像是资讯类产品标准IEC61000-4-5,北美电信商的GR1089,欧美电信商的K.21等。上述的这些法规,针对以太网口的测试皆有Common mode及Differential mode这两种,测试的波形为1.2/50us开路电压和8/20us短路电流波形。Common mode surge测试架构如下图一所示,测试手法是将网口的信号线(10/100Mbps为2组Differential pairs,1000Mbps为4组Differential pairs)接至Surge波形产生器的High接口,Surge波形产生器的Low接口接至大地,并对信号线注入Surge测试电压,每个测试电压注入Surge能量的次数为5次,间隔为60秒。需要特别注意的是每个法规所规定之测试阻抗及测试电压会有所不同,需详细确认后再执行测试。

图一: Common mode surge test 示意图

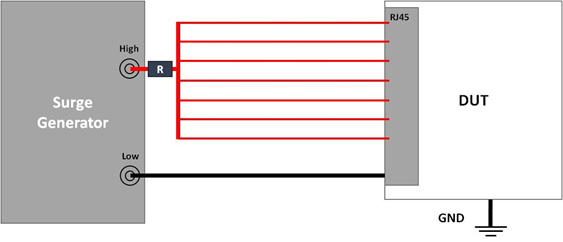

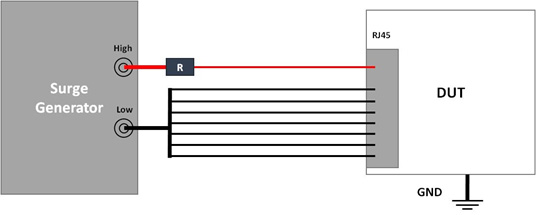

以太网口Differential mode surge测试手法跟Common mode不同,Differential mode surge是将surge能量注入差动信号间(例如TX+跟TX-),各个法规的手法又有些许不同,本文将以IEC61000-4-5及GR1089 Intra-Building两个国际标准为例进行说明。

•IEC61000-4-5测试阻抗为42 ohm,手法为Surge测试机台High端口接七条Ethernet信号线,Low端口接剩下的一条,测试完第一组后,须将Low端口接至下一条信号线,八条信号线都必须轮流接至Low端口,故会有八种测试组合。每种组合每个测试电压注入Surge能量的次数为5次,间隔为60秒,因Differential mode测试的组合较多,故测试所需的时间也较Common mode长,测试架构如下图二。

•GR1089里Intra-Building的Differential mode测试手法为Surge测试机台High端口接一条Ethernet信号线,Low端口接剩下的七条,八条信号线都必须轮流接至High端口,测试阻抗为8 ohm,其测试架构如下图三。

IEC61000-4-5及GR1089 Intra-Building虽手法有些许不同,但目的都是为了验证产品接口的EOS/Surge抗受性,达到预防突波干扰的效果。

图二: IEC 61000-4-5 Differential mode surge test 示意图

图三: GR1089 Differential mode surge test 示意图

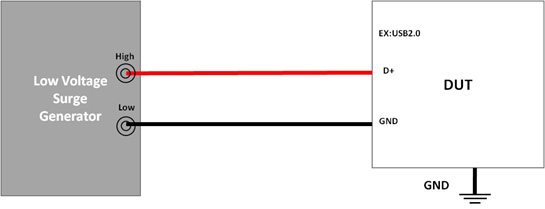

除了上述的测试端口及标准外,近几年手机、电脑、电视在产线及市场售后也遭遇越来越多对外接口被EOS能量破坏的问题,因此各大品牌厂从原本针对信号线端口的ESD Direct-Pin Injection测试外,亦追加导入了低压的EOS Direct-Pin Injection测试手法,来增强产品信号线端口的EOS耐受。

测试波形同样是依据IEC61000-4-5 的1.2/50us开路电压和8/20us短路电流波形,测试时的输出串联阻抗为2欧姆。由于测试的端口以USB、HDMI等高速信号端口为主,测试时要求的的起始电压、步进电压或需通过的电压规格皆较前述测试以太网口时低很多(例如:要求高速差分对信号线需通过EOS ±25V的规格,测试时的步进电压为2V或5V),期望透过低电压的较低EOS能量来放大测试结果的鉴别度,以利进行设计改善或规格调整。

测试方式是将低压Surge产生器的输出High端口接至待测信号线而Low端口接至系统地,并对信号线注入EOS能量,其测试电压、间隔秒数及注入Surge的次数由品牌厂制定。低压EOS测试架构如图四所示。

图四: Low voltage EOS test 示意图

上述介绍的三种EOS/Surge测试手法,可依照产品应用的环境挑选合适的EOS测试方式。此三种方式虽然各有差异,但其目的都是为了增加产品的EOS抗受性,故建议在系统设计初期就将EOS/Surge防护对策纳入考量,以提升产品EOS耐受程度,并降低产品在产线及市场端因EOS而发生的客退机率。

提供原厂技术方案设计,欢迎联系我们,电话075582542001,82574660谢谢惠顾~

审核编辑 黄宇

-

以太网

+关注

关注

41文章

5933浏览量

179664 -

EOS

+关注

关注

0文章

132浏览量

22092

发布评论请先 登录

抗EOS设计详解及实际"栗子"

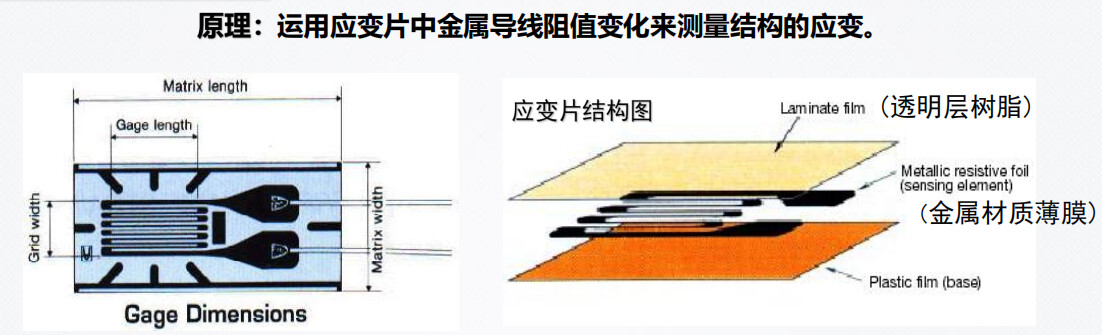

PCBA应力测试方法原理和应变片怎么粘贴

AKEMOND应力应变测试仪选型

Green Testing Lab联合CSM开展电池温度测试

PCBA应力测试:从标准方法到产业实践的可靠性守护

晶圆切割中振动 - 应力耦合效应对厚度均匀性的影响及抑制方法

详解晶圆级可靠性评价技术

CMOS可靠性测试中的电荷泵和交流应力技术解析

“System Level EOS Testing Method”可以翻译为: “系统级电性过应力测试方法”

“System Level EOS Testing Method”可以翻译为: “系统级电性过应力测试方法”

评论