全社会都在积极推动低碳化转型,而低碳化的背后其实是电气化。在新型电气能源架构中,相比于从前,一次能源到终端用户的能源转换次数增多。虽然可再生能源是免费的,但是这种多层级的能源转换,每一步都会带来一定的能耗损失,因此追求更高效的能源转化效率至关重要。

SiC正是功率半导体的能效提升技术,它的出现满足了低碳化时代两大全新的市场需求:

1

能效创新:SiC技术在光伏、储能、数据中心等大功率电源管理领域,能够显著提升能源转换效率。随着全球对清洁能源的需求增加,SiC的应用场景也在不断扩大。

2

设计创新:在电动车、高铁动力推进系统、机器人伺服等领域,SiC技术能够实现设备的小型化、低成本和高效节能。这不仅降低了生产成本,还提升了系统的性能。

成为首选的零碳技术创新伙伴

英飞凌一直致力于为用户提供更可靠的碳化硅技术,并主张“最值得信赖的技术革命”。随着SiC技术的普及,英飞凌的目标是成为首选的零碳技术创新伙伴。我们深信,企业的未来不在于与谁竞争,而在于与谁合作。因此,英飞凌致力于与客户协同创新,实现共赢。

随着SiC的应用增多,客户对SiC技术知识的积累正热情高涨。然而在日常访客过程中,我发现即使是资深的研发工程师,都会存在两个最常见的认知误区。今天我们就通过两篇系列文章做个深入浅出的解读。

常见误区1:可靠性之争

误解:“平面栅相对简单,单元一致性较好,可靠性更高;沟槽栅结构、工艺都很复杂,底部电场集中,容易引发长期可靠性问题”

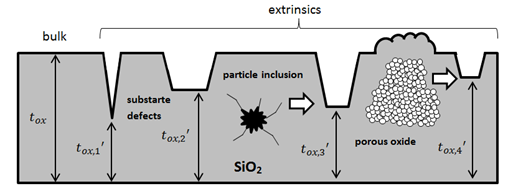

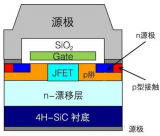

提及“可靠性”,不论是Si还是SiC功率半导体器件,都不得不谈到产品结构中一个重要的组成部分,即“栅极氧化层”。SiC的衬底缺陷、颗粒杂质、制程差异,会给SiC MOSFET的栅极氧化层带来很多缺陷,如下图所示。这些缺陷最终会呈现为栅氧有效厚度的减薄。这会让器件的寿命大打折扣,更容易出现击穿和早期失效现象。因此,为了让SiC和Si器件一样可靠好用,必须最大限度降低栅极氧化层缺陷密度。

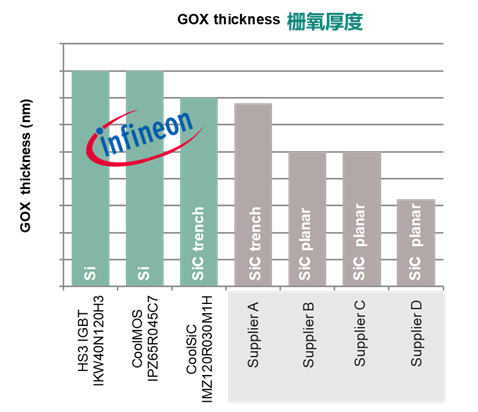

英飞凌Trench沟槽栅技术之所以更可靠,离不开更高效的筛选测试方法。我们使用更高的筛选电压来发现氧化层中的绝大部分缺陷。筛选电压越高,能发现的缺陷数量越多,从而筛选后的器件拥有更卓越的可靠表现。这点平面栅很难做到。

为何平面栅不能使用更高筛选电压?因为平面栅的栅极氧化层更薄。更薄的氧化层可以增强栅极对导电沟道的控制能力,来抵消水平方向栅极氧化层-沟道界面高密度缺陷对电子流动的阻碍作用,降低沟道电阻。

为什么沟槽栅的栅极氧化层可以做得更厚呢?如何理解栅极氧化层与导电沟道之间的界面缺陷,平面栅和沟槽栅有何不同?

MOSFET中导电沟道形成于栅极氧化层下面,如果把形成电流的电子比喻成路上行驶的汽车的话,栅极氧化层下面的导电沟道就像汽车行驶的路面。由于SiC和Si的材料特性截然不同,这条路面就会呈现出完全不同的路况。如果说Si基功率器件导电沟道像是一条高速公路的话,SiC的导电沟道更象一条颠簸山路,高低不平的路面其实就是“氧化层-沟道界面缺陷”。

由于SiC材料各向异性特性,使其水平方向的氧化层界面缺陷密度远远大于垂直方向。打个形象的比喻:SiC采用平面栅技术,就好像汽车在颠簸路面行驶时,同样的油耗,行驶的速度更低;而沟槽栅技术恰恰就利用了垂直方向界面缺陷密度更少的特性,就好比在颠簸路况处挖了地下高速隧道,更易于实现高速行驶。如果想要达到同样的行驶速度,平面栅就要一脚油门踩到底,这表现在功率器件的技术实现上,平面栅需要使用更薄的栅极氧化层。相反,沟槽栅的栅极氧化层则可以做得更厚。

如果只想在碳化硅器件单一电气参数的竞赛中胜出,一味地追求更低的导通电阻,应用平面栅技术的厂家就会倾向于使用更薄的栅极氧化层。但由于栅极氧化层自身杂质缺陷带来的有效厚度减损,当电场强度超过了一定的阈值,就会导致瞬时击穿,长期使用也可能带来TDDB经时击穿等现象。所以,如果缺乏深刻的理解和科学的筛查方法,在实际的动态工况应力下,栅极氧化层的有效寿命很可能会远远低于预期结果。

结论

越厚的氧化层,越可能使用比典型应用电压高很多的筛查电压,同时保证不损坏能通过筛查试验的无缺陷器件。

英飞凌的沟槽栅可以通过更厚的氧化层和更高的筛选电压,来最大限度地降低栅极氧化层缺陷率,保障可靠性。

这种对SiC材料物理底层的深度理解,以及超过40年沟槽栅技术、沟槽底部电场均匀设计的长期积累,使得英飞凌沟槽栅在SiC领域提前占据了可靠性的领先地位。

看到这里,关于SiC MOSFET的第一个误区——沟槽栅可靠性不如平面栅——也就不攻自破了。关于SiC MOSFET的性能评价还有一个误区:

“SiC的性能主要看单位面积导通电阻Rsp,电阻越小,产品越好。

与平面栅相比,沟槽栅SiC的电阻在高温下漂移更大,这是否会影响可靠性?”

关于这个问题的理解我们将在下篇文章进行详细阐述,敬请持续关注。

-

英飞凌

+关注

关注

68文章

2560浏览量

143133 -

碳化硅

+关注

关注

26文章

3538浏览量

52647 -

能源转换

+关注

关注

0文章

21浏览量

6813

发布评论请先 登录

博世碳化硅技术路线图持续演进

技术突围与市场破局:碳化硅焚烧炉内胆的氮化硅陶瓷升级路径

新品 | 英飞凌XHP™ 2系列2300V CoolSiC™ 碳化硅MOSFET

博世碳化硅垂直沟槽蚀刻技术的核心优势

【新启航】碳化硅外延片 TTV 厚度与生长工艺参数的关联性研究

【新启航】如何解决碳化硅衬底 TTV 厚度测量中的各向异性干扰问题

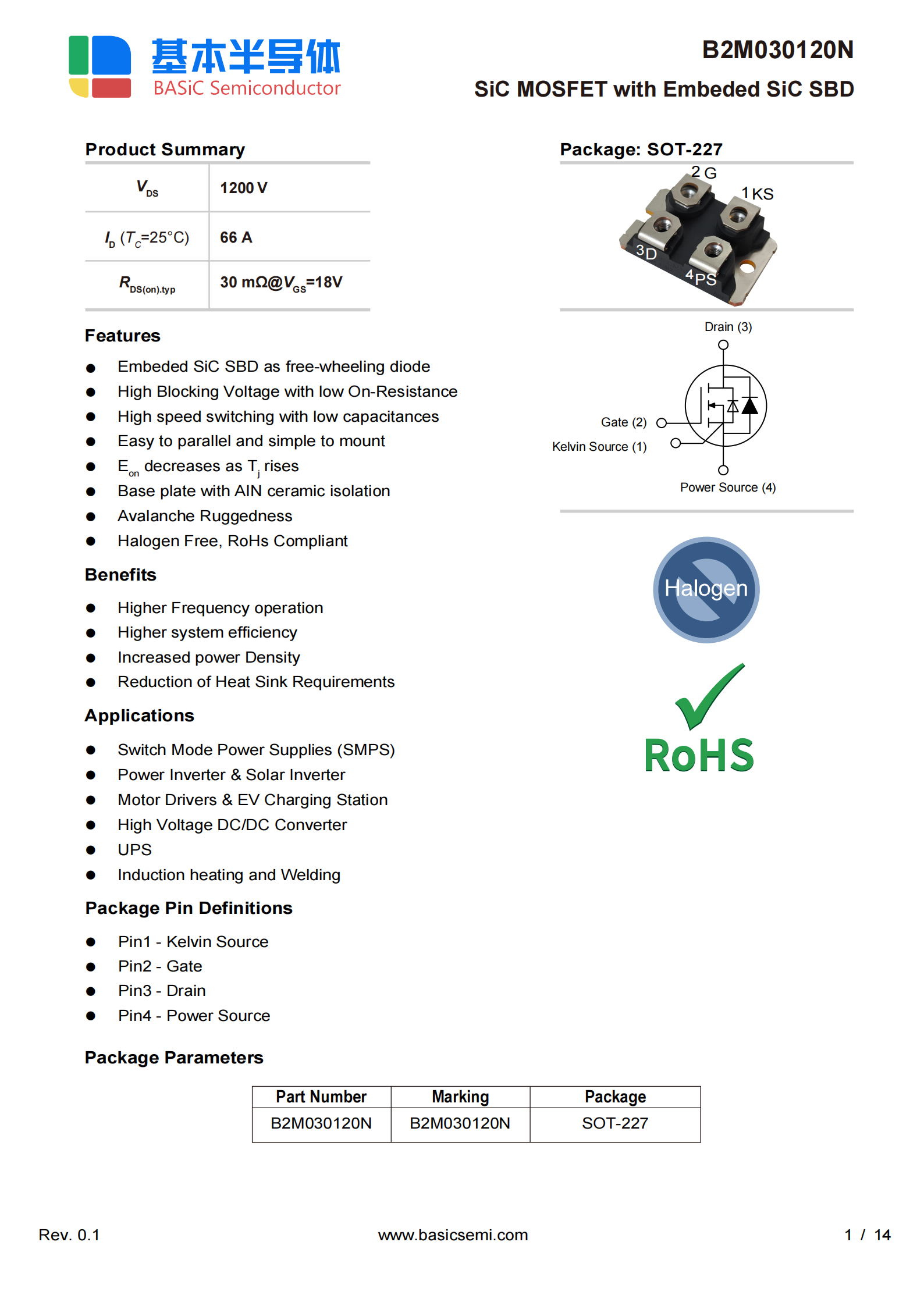

基本半导体推出34mm封装的全碳化硅MOSFET半桥模块

B2M030120N SiC碳化硅MOSFET完美契合半导体射频电源对效率、可靠性和紧凑化的严苛需求

EAB450M12XM3全碳化硅半桥功率模块CREE

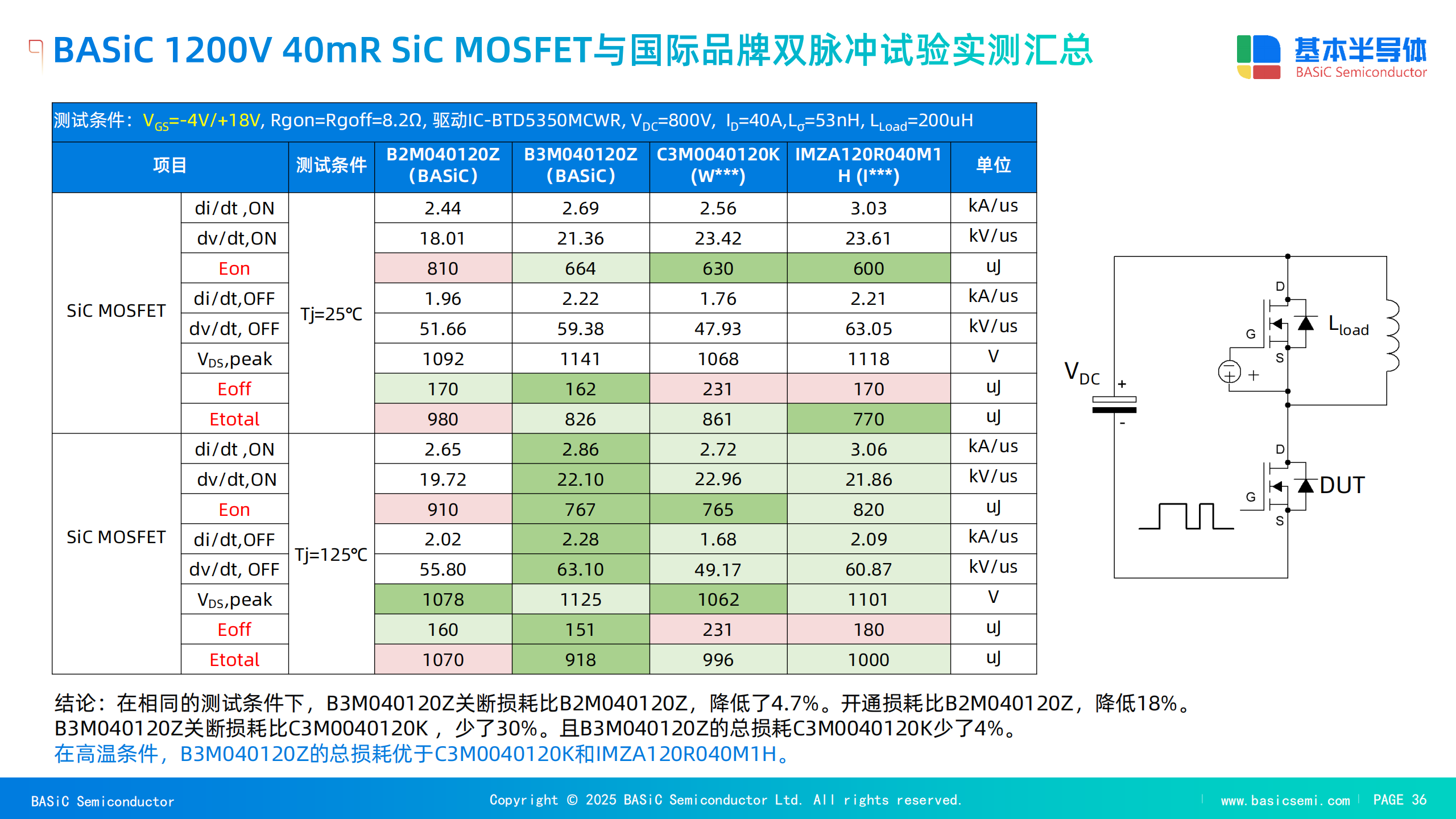

基本半导体碳化硅 MOSFET 的 Eoff 特性及其在电力电子领域的应用

IPAC碳化硅直播季倒计时丨沟槽栅VS平面栅,孰是王者?

碳化硅何以英飞凌?—— 沟槽栅技术可靠性真相

碳化硅何以英飞凌?—— 沟槽栅技术可靠性真相

评论