核芯互联CLRD320:高速互连解决方案

在数据中心、人工智能和高性能计算需求爆发的今天,高速信号传输的稳定性和效率成为系统设计的核心挑战。核芯互联推出的CLRD320八通道redriver(线性转接驱动器)芯片,凭借多项技术创新,为PCIe 5.0、PCIe 6.0、CXL 2.0等超高速接口提供了更优的国产化解决方案,助力企业突破信号完整性与系统能效的瓶颈。

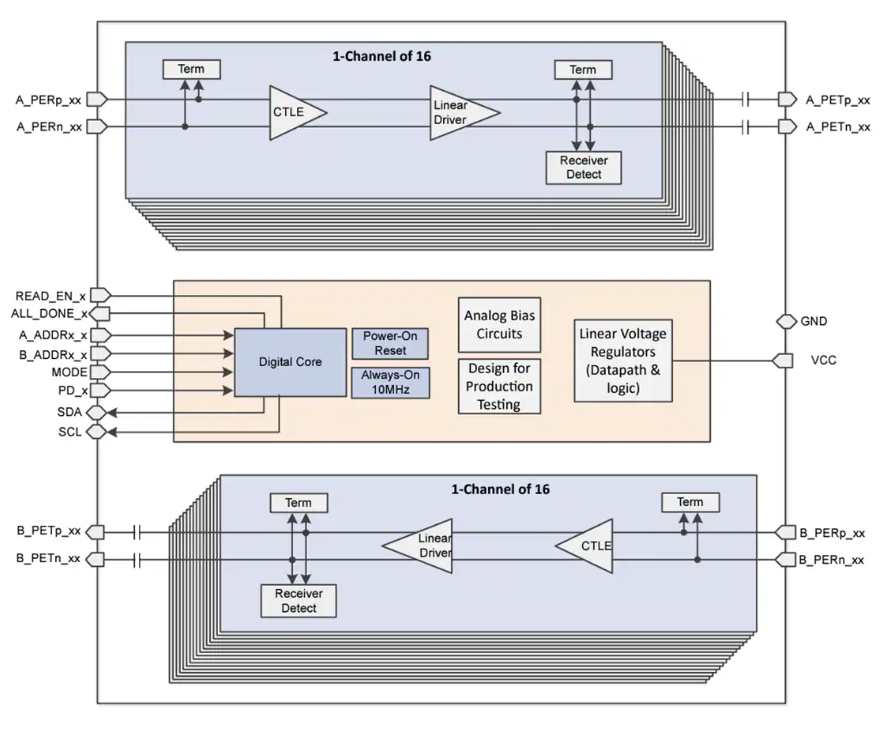

CLRD320完全采用国产化设计,封装上与DS320PR810的完全Pin 2 Pin兼容,提供更优秀的增益和串扰抑制。

什么是redriver芯片

Redriver芯片(重驱动器芯片)是一种用于高速信号传输的关键器件,主要功能是补偿信号在传输过程中的衰减和失真,提升信号完整性。

基本定义

Redriver是一种模拟信号调理芯片,通过均衡器(如CTLE)和信号放大器来增强高频信号的幅度,抵消传输线(如PCB走线、电缆)导致的频率相关衰减。它不涉及协议处理,仅作用于物理层,因此具有低延迟(<5ns)和低功耗的优势。

工作原理

- 信号补偿:在发送端,Redriver通过连续时间线性均衡器(CTLE)补偿信号的高频损耗,再通过增益放大恢复信号幅度;

- 预加重/去加重:部分型号支持预加重技术,提前增强信号的高频分量,以对抗传输中的衰减;

- 眼图优化:通过上述技术,Redriver能将原本闭合的信号“眼图”重新张开,降低误码率。

典型应用场景

- PCIe/USB/HDMI/以太网接口:延长高速接口(如PCIe 4.0/5.0)的信号传输距离,解决服务器、AI加速卡等场景中的链路损耗问题;

- 数据中心与存储:用于NVMe SSD、全闪存阵列等设备,确保高速存储协议(如SATA/SAS)的稳定性;

- 车载与工业电子:工业级Redriver可支持车载以太网、传感器数据汇聚等严苛环境下的信号传输。

与reimter的技术、市场应用及成本对比分析

信号处理机制

- Redriver:本质是模拟信号放大器,通过连续时间线性均衡(CTLE)和增益级补偿信道损耗,仅放大信号但无法消除累积抖动和噪声。其延迟极低(约100ps),但无法恢复数据时钟,不参与协议交互(如PCIe链路训练)。

- Retimer:采用数字+模拟混合架构,集成时钟数据恢复(CDR)和判决反馈均衡(DFE),能完全再生信号并消除抖动,支持协议层交互(如PCIe均衡训练)。其延迟较高(约64ns),但可重置链路时序预算,适用于复杂信道环境

均衡能力与协议支持

- Redriver仅支持CTLE和预加重,无法处理反射和串扰(核芯互联CLRD320中加入了动态串扰抑制电路,可以有效的抑制串扰),信号噪声可能被放大。

- Retimer通过DFE和Tx FIR均衡器,可动态调整参数适应信道特性,支持PCIe、CXL等复杂协议,且能消除串扰影响。

信号完整性

- Redriver在中短距离场景下性价比高,但长距离传输时眼图恶化风险大。

- Retimer通过CDR再生信号,可延长传输距离,并保持高质量眼图。

CLRD320的技术突破:攻克高速互连三大核心挑战

-

32Gbps超高速信号完整性优化

CLRD320在支持PCIe 5.0(32Gbps)速率的同时,通过多级自适应均衡技术,将CTLE(连续时间线性均衡)在16GHz下的增益提升至24dB(较同类产品提升9%),有效补偿长达40英寸的FR4 PCB走线损耗。其创新的动态串扰抑制电路可将通道间串扰降低至-45dB以下,确保在密集布线场景下的眼图张开度。 -

亚纳秒级超低延迟设计

针对AI训练、金融交易等对实时性要求严苛的场景,CLRD320采用全差分线性驱动架构,将端到端传输延迟压缩至85ps(行业平均100ps),并通过独特的时钟树优化技术,实现通道间延迟偏差<5ps,显著降低系统时序不确定性。 -

智能电源管理与热控制

在3.3V单电源供电下,CLRD320集成多级动态电压调节模块,可自适应负载波动,将电源噪声抑制能力提升至30dB@500MHz,且低功耗的设计使得芯片无需外置散热器即可在-40℃~105℃宽温范围内稳定运行。

技术优势:性能全面升级,设计无缝迁移

| 特性 | CLRD320 | 竞品典型值 |

|---|---|---|

| 最大数据速率 | 32Gbps(兼容PCIe 5.0/CXL 2.0) | 32Gbps |

| CTLE增益@16GHz | 24dB | 22dB |

| 附加随机抖动(RJ) | 65fs RMS | 75fs RMS |

| 端到端延迟 | 85ps | 100ps |

| 单通道功耗 | 145mW(@32Gbps全负载) | 160mW |

| 温度范围 | -40℃~105℃ | -40℃~85℃ |

此外,CLRD320提供三重配置模式:

• Pin Strap模式:通过电阻配置快速启用预设优化参数,缩短开发周期

• I2C/SMBus接口:支持实时通道级EQ调节与状态监控

• EEPROM自加载:可实现多设备级联配置,适用于x24宽链路拓扑

应用场景:赋能下一代算力基础设施

-

AI服务器与异构计算

在GPU/FPGA集群中,CLRD320可延长PCIe 5.0信号传输距离至1.5米(通过电缆),解决多机柜扩展时的信号衰减问题,同时支持CXL 2.0内存池化低延迟互联。 -

全闪存存储与数据中心网络

针对NVMe-oF架构,CLRD320的-50dB回波损耗特性可优化25G/100G以太网物理层连接,确保RDMA零拷贝传输的稳定性,助力存储时延降至微秒级。 -

自动驾驶域控制器

CLRD320,可在车载环境下实现多传感器数据的低抖动汇聚,支持10Gbps车载以太网TSN实时通信。 -

5G基带与边缘计算

在O-RAN前传网络中,CLRD320的高抗噪特性可有效抑制毫米波频段干扰,确保CPRI/eCPRI接口在复杂电磁环境中的可靠性。

-

驱动器

+关注

关注

54文章

9115浏览量

156508 -

PCIe

+关注

关注

16文章

1479浏览量

88923 -

核芯互联

+关注

关注

0文章

40浏览量

2490

原文标题:核芯互联发布支持PCIe 5.0/6.0的32/64Gbps的高速redriver芯片CLRD320

文章出处:【微信号:gh_0dbe96735e9d,微信公众号:核芯互联】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

MACOM宣布推出面向长距离、城域和数据中心互连应用的四通道64G线性调制器驱动芯片

MACOM宣布推出面向100G和400G PAM-4应用的单通道和四通道线性EML驱动器系列

核芯互联推出符合DB2000QL及PCIe Gen5和Gen 6标准的低抖动时钟缓冲器CLB2000

核芯互联推出全新20路LP-HCSL差分时钟缓冲器CLB2000

AI和数据中心:PCIe 6.0,你是懂加速的

DS320PR1601 32Gbps 16通道PCIe 5.0、CXL 2.0线性转接驱动器数据表

Alpahwave Semi推出全球首个64Gbps UCIe D2D互联IP子系统

DS320PR1601 PCIe 5.0 32Gbps线性转接驱动器技术解析与应用指南

解析DS320PR822:PCIe 5.0和CXL 1.1的高性能线性转接驱动器

探索SN75LVPE5412:PCIe 5.0 32Gbps 4通道线性转接驱动器的卓越性能与应用

深入剖析SN75LVCP601:双信道6Gbps SATA重驱动器的卓越之选

忆联正式推出面向PCIe 5.0的自研M.2 SLT测试系统

MB408A5 PCIe 5.0 x4 NVMe扩展卡:转MCIO 4i接口,内置Redriver信号重驱动器

核芯互联推出面向PCIe 5.0/6.0的32/64Gbps高速重驱动器芯片CLH3264R

核芯互联推出面向PCIe 5.0/6.0的32/64Gbps高速重驱动器芯片CLH3264R

评论