ㄧ、电容电感的阻抗

被动型喇叭分音器基本上是由电感与电容组成,由于...

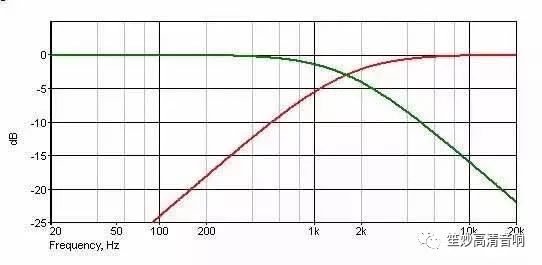

频率越高时电容器的阻抗会越小,反之亦反

频率越高时电感器的阻抗会变大,反之亦反

两者功能互补关系很适合用来设计分音器。

例如:高音喇叭串联一颗1uF的电容器时其阻抗在各种频率时为Xc=1/(2x3.14x f xC )所以

10Hz时是2.4K欧姆

100Hz时是240欧姆

1KHz时是24欧姆

3KHz时是8欧姆

10KHz时是2.4欧姆

20KHz时是1.2欧姆

所以3KHz以下的音频会被电容器的高阻抗阻挡不能产生电流。3KHz以上则畅通产生电流振动纸盆发出声音。

同理低音喇叭串联0.4mH电感时其阻抗为XL=2 x3.14 x f x L

10Hz时是0.026欧姆

100Hz时是0.26欧姆

1KHz时是2.6欧姆

3KHz时是8欧姆

10KHz时是24欧姆

20KHz时是48欧姆

所以3KHz以上的音频会被阻挡不能产生电流,3KHz以下则畅通,产生电流振动纸盆发出声音。

如此一来声音就会被分为两股,分别流入不同喇叭。

二、主流分音器设计有三种

一阶型分音器

就是高音喇叭串一颗电容,低音喇叭串一颗电感的最简结构。这种分音法频率响应很平坦。它的衰减率是..

6dB/octave或20dB/decade

6dB/octave是2进位值,表示频率2倍时声音会衰减4倍

20dB/decade是10进位,表示频率10倍时声音会衰减100倍

octave就是八度音,也就是频率2倍或1/2倍的意思。例如:

分音点是3KHz的话,1.5KHZ或6KHz的功率就会衰减到剩原来的1/4。

decade是10倍的意思,也就是频率10倍或1/10倍时功率就会衰减到剩原来的1/100。例如:

分音点是3KHz的话,300HZ或30KHz的功率就会衰减到剩原来的1/100

这种分音法适合小喇叭,但因分工显然不够锐利,两只喇叭共同工作的频率区域实在太宽。两个喇叭为同一个频率,同时振动时,相位不一致的问题很多。声音自然会觉得有点混浊。

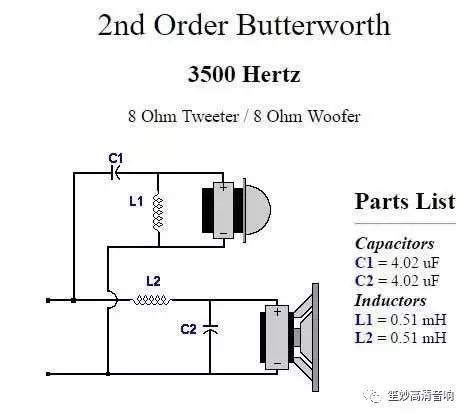

二阶型

高音喇叭串联电容,并联电感。低音喇叭串联电感,并联电容。这种方法衰减斜率会增至

12dB/octave 40dB/decade。

12dB/octave频率2倍时衰减12dB=16倍

40dB/decade频率10倍时衰减40dB=1万倍

这种分音方式,喇叭分工会更清楚,共同区域会减少,但因为高音移相+90°低音移相-90°,两者正好相差180°,所以有人主张必须将高音单元反接,以使其相位一致。其实中音反接也可以,意思一样。在三喇叭系统时,则是高低音喇叭保持正接,只有中音喇叭反接。

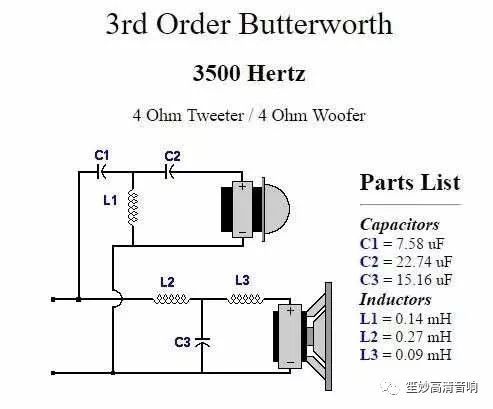

三阶型

高音串两个电容,中间接一个电感接到负极。

低音串两个电感,中间接一个电容接到负极。

这也就是射频滤波器常用的PI型滤波器。用这种方法滤波,斜率会增至18dB/octave即60dB/decade

它是所有高级喇叭分音器的主流作法,因为高音移相+180°,低音移相-180°

(180-(-180))=360°)=0°

绕一圈后相位变一样。所以他就没有喇叭需要反置的担忧,频率响应也很平坦。

18dB/octave频率2倍时衰减18dB=63倍

60dB/decade频率10倍时衰减60dB=100万倍

这种分音方式,频率切割已经非常锐利,两只喇叭同时为同样频率发声只有很窄的区域,纸盆震动相位不协调造成的困扰几乎都消失了,设计师只要将分频点调到两个喇叭震动完全同相,就大功告成了。这也是喇叭制造厂的重要KNOW HOW。不轻易告诉别人。但是这种滤波器,数学上是不对称的。要用技巧克服,方法当然是商业秘密。

四阶及更多阶

越多阶的分音器频率切换越锐利,分音点越没有问题,但是其它问题却很多,所以用的人不多。

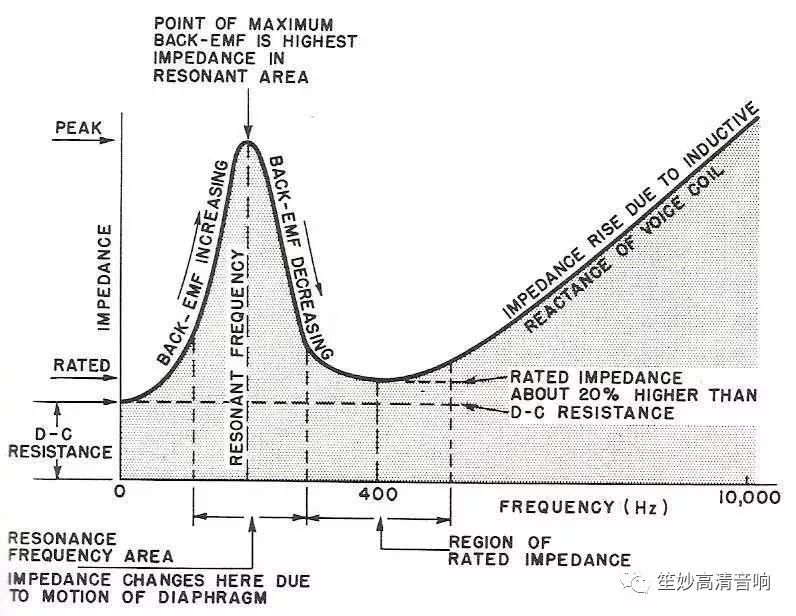

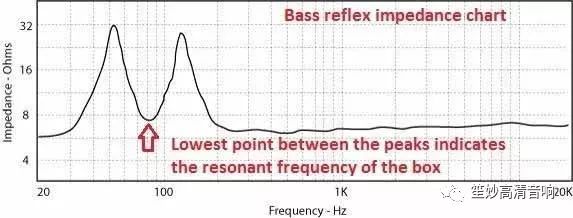

三、自己设计分音器

你如果想自己用计算机辅助,设计分音器,就会发现,所有分音器电路都是假想两只喇叭的阻抗都是8欧姆,或2/4/6/8 欧姆,但是只要看看喇叭的阻抗曲线就知道喇叭只有在1KHz时是8欧姆。在其他地方及分音点例如:3KHz时,从来不是8欧姆。高音喇叭的阻抗在分音点可能是2欧姆,中音喇叭的阻抗可能是20欧姆,低音喇叭可能是100欧姆,根本没有一个是8欧姆。套8欧姆怎能算出有用的数字。套用公式后会发现,计算机跑出来的电容/电感值与原厂的实际数值差了3倍,而百思不得其解。

-

阻抗

+关注

关注

17文章

983浏览量

48806 -

分频器

+关注

关注

43文章

536浏览量

52321

原文标题:喇叭分频器与相位移问题 (谈谈喇叭)

文章出处:【微信号:SONMIU,微信公众号:笙妙高清音响】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

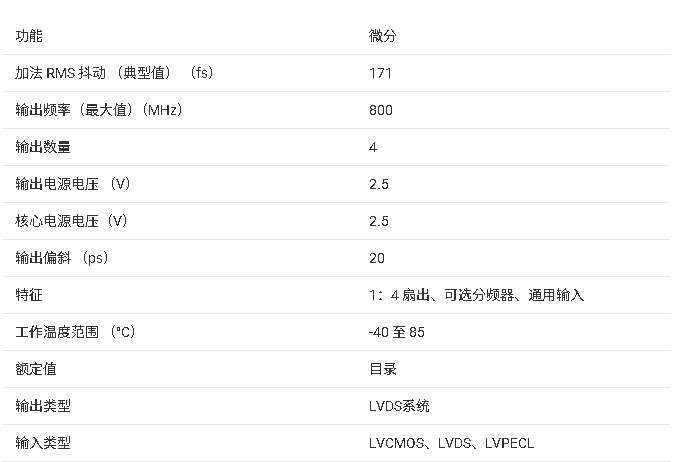

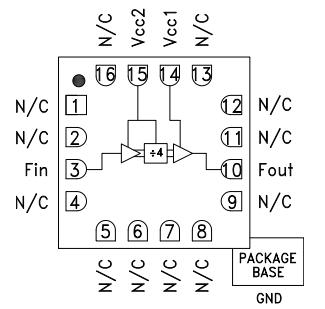

CDCLVD1213 1:4低附加抖动LVDS缓冲器带分频器 技术文档摘要

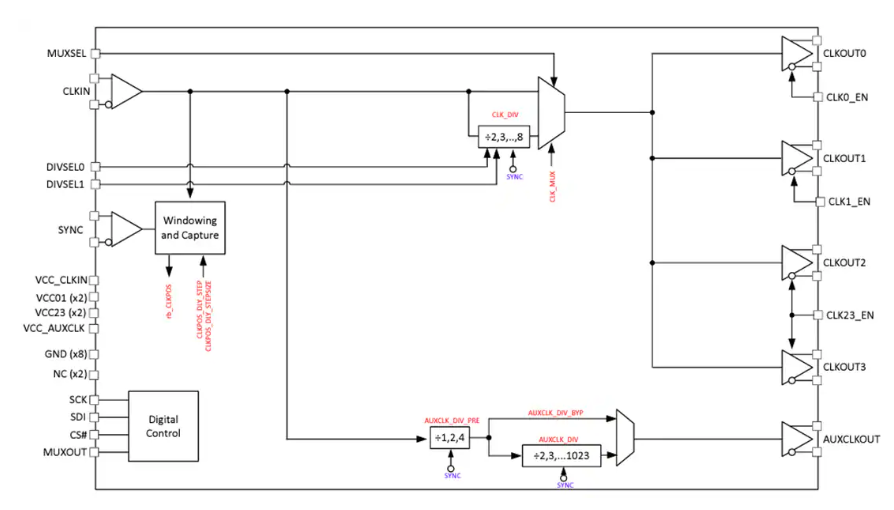

德州仪器LMX1214射频缓冲器与分频器技术解析

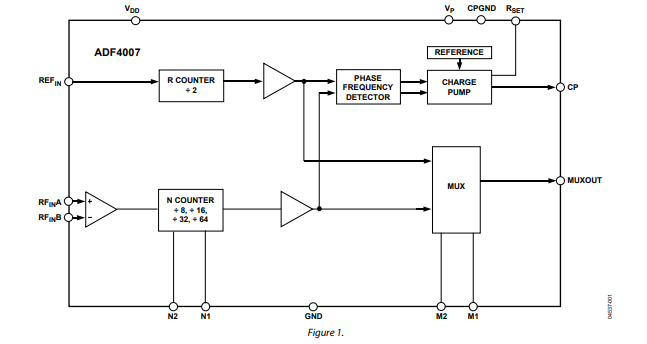

ADF4007高频分频器/PLL频率合成器技术手册

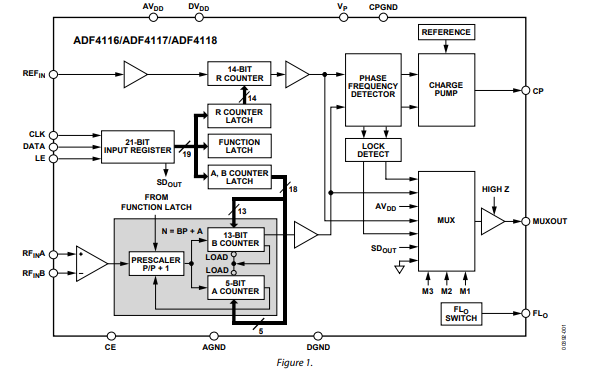

ADF4116/ADF4117/ADF4118单通道、整数N分频550MHz PLL技术手册

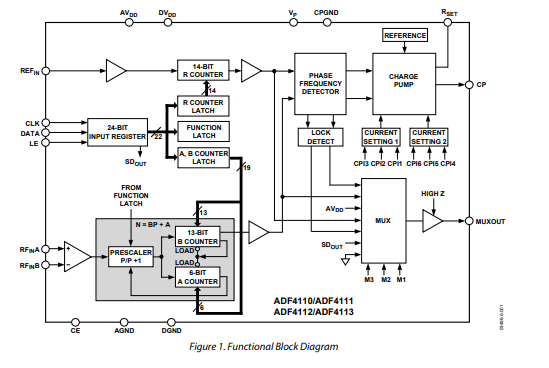

ADF4110/ADF4111/ADF4112/ADF4113单通道、整数N分频、550 MHz PLL,内置可编程预分频器和电荷泵技术手册

ADF4156 6.2GHz小数N分频频率合成器技术手册

ADF4151小数N/整数N分频PLL频率合成器技术手册

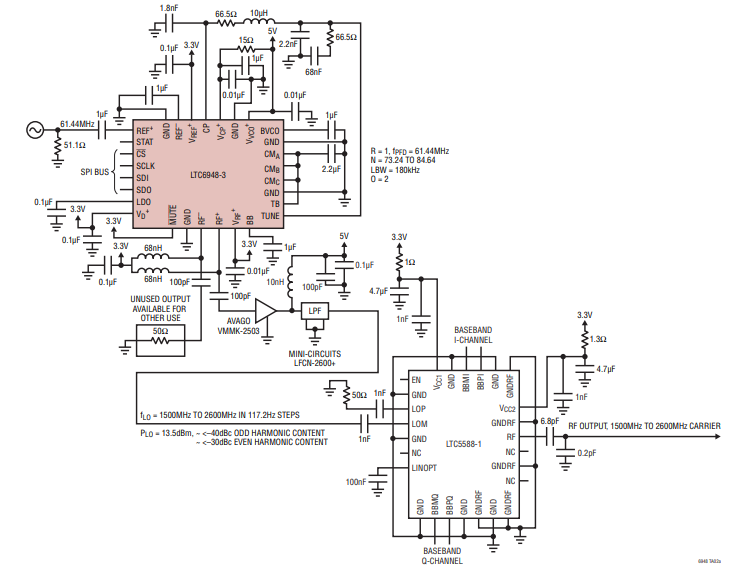

LTC6948具集成型VCO的超低噪声0.37GHz至6.39GHz分数N合成器技术手册

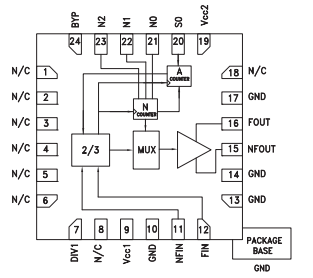

HMC705LP4/HMC705LP4E 6.5GHz可编程分频器SMT技术手册

HMC447LC3使用InGaP HBT技术,4分频,采用SMT封装技术手册

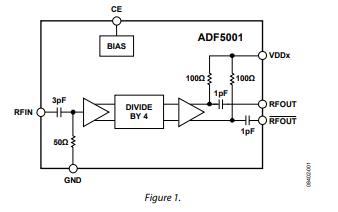

ADF5001 4GHz 至18GHz 4分频预分频器技术手册

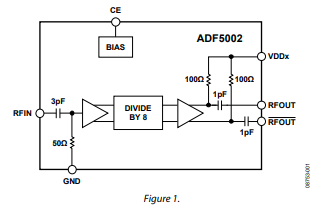

ADF5002 4GHz至18GHz 8分频预分频器技术手册

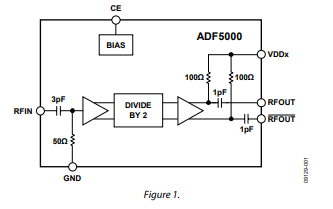

ADF5000 4GHz 至18GHz 2分频预分频器技术手册

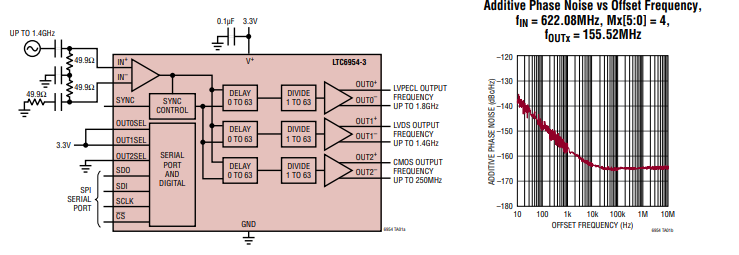

LTC6954低相位噪声、三路输出时钟分配分频器/驱动器技术手册

74HC4060-Q100;74HCT4060-Q100计数器/分频器和振荡器规格书

喇叭分频器与相位移问题

喇叭分频器与相位移问题

评论